大华FPGA的笔试问题解析

二、试题内容解析

1.选择题

1、Assign a = (b[15:0] == 16’hd5) ? 1’b0 : 1’b1;该语句需要几个4输入LUT实现( )

A 2 B 3 C 4 D 5

2、#include

Main()

{

int a;

int b;

a=-2;

b=0;

while(a++&&++b);

printf("%d,%d\n", a,b);

}

程序运行后的输出结果是

A 1,3 B 0,2 C 0,3 D 1,2

3、大规模可编程器件主要有CPLD和FPGA两类,下面对CPLD结构和工作原理描述中,不正确的是( )

A CPLD中文全称是复杂可编程逻辑器件

B 基于SRAM的FPGA器件,每次上电须进行一次配置

C CPLD的触发器资源丰富

D CPLD信号通过芯片的延时时间是确定的

4、综合是EDA设计的关键步骤,下面有关综合的描述错误的是( )

A 综合就是把抽象设计中的一种表示转换成另一种表示的过程。

B 综合就是将电路的高级语言转换成低级的,可与FPGA/CPLD相映射的功能网表文件。

C 为实现系统的速度、面积、性能要求,需要对综合加以约束,成为综合约束。

D 综合可以理解为一种映射过程,并且这种映射关系是唯一的,即综合结果是唯一的。

5、Y(A,B,C) = Σm(0,1,2,3)逻辑函数的化简式为( )

A Y=AB+BC+ABC B Y=A+B C Y=A’ D Y=B’

6、以下代表异或门的是( )

A B C D

7、FPGA设计优化主要考虑面积优化和速度优化,以下不属于面积优化的是( )

A 流水线设计 B 逻辑优化 C 串行化 D 资源共享

8、设有定义:int x[2][3];则以下关于二维数组x的叙述错误的是( )

A x[0]可以看作是由3个整型元素组成的一维数组

B x[0]和x[1]是数组名,分别代表不同的地址常量

C 数组x包含6个元素

D 可以用语句x[0]=0;为数组所有元素赋初值0

2.解析

1.在开发FPGA的时候,很多人不会关注LUT与逻辑电路映射的关系,也没有关注过Verilog代码与逻辑电路的映射关系,直接用Verilog硬件描述语言描述电路的功能。

这道题目是用组合逻辑实现的代码,也就是不会使用到寄存器资源,而题目的问题是“需要几个4输入LUT实现”,也就是告诉大家用Verilog描述的组合逻辑在FPGA中最后会映射到LUT上来实现,所以先来看看这是一种怎样的映射关系。所以[15:0]一共是4个4位的LUT,最后一个四位的LUT用来选择这4个。所以本题的答案一共是5个LUT。

2.代码问题

include <stdio>

Main()

{

int a;

int b;

a=-2;

b=0;

while(a++&&++b);

printf("%d,%d\n", a,b);

}

这个是C语言基础问题,经过分析可以知道:在c中,while循环当为0时,判断为false,其他都为true(包括-2这样的负数)

a++先取值后累加 ++a先累加后取值

那么循环为

第一次:a=-2 b=1 true

结果 a=-1 b=1

第二次:a=-1 b=1 true

结果 a=0 b=2

第三次:a=0 b=2 false(循环终止)

循环虽然终止了,但是循环条件依然执行了,所以a=1 b=2

3.B 基于SRAM的FPGA器件,每次上电须进行一次配置

4 综合可以理解为一种映射过程,并且这种映射关系是唯一(并不是唯一)的,即综合结果是唯一的。错误

5.本题主要考察了数电中逻辑表达式的化简

先把题干的内容转化为逻辑表达式后再进行化简。

Y(A, B, C) = ∑m(0, 1, 2, 3)

= 000+001+010+011

= A’B’C’+A’B’C+A’BC’+A’BC

= (A’B’C’+A’B’C) + (A’BC’+A’BC)

= [A’B’(C’+C)] + [A’B(C’+C)]=

A’B’+A’B

= A’(B’+B)

= A’

所以答案选C。

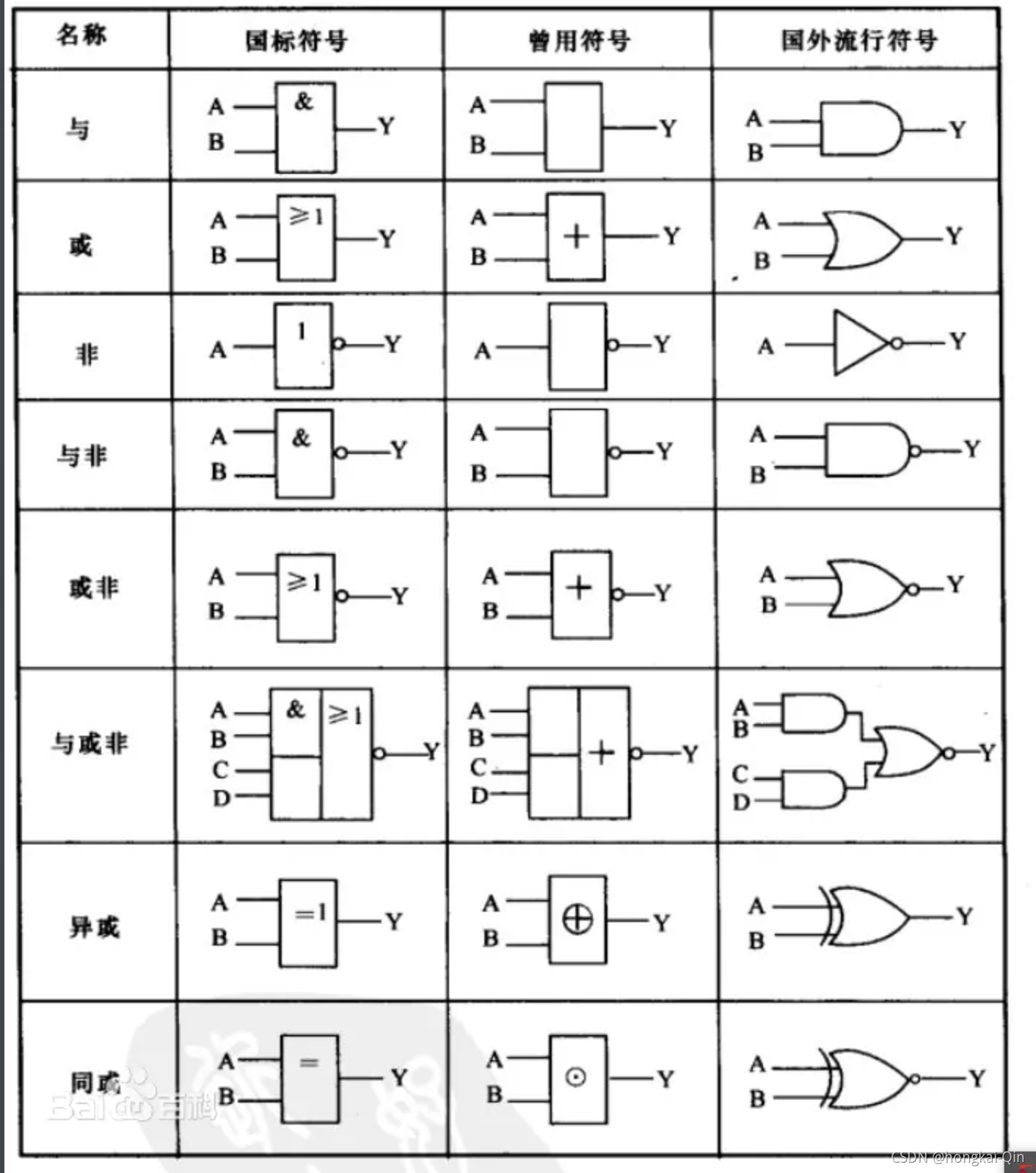

6.

7.速度优化,提高运行速度:

(1)流水线设计(也是属于关键路径的优化,在关键路径的组合逻辑中插入寄存器);

(2)寄存器配平(重定时);

(3)关键路径优化(减少关键路径上的组合逻辑延时);

(4)消除代码优先级(if_else嵌套、case);

(5)并行化(加法树、乘法树,消除符号运算的优先级);

面积优化,提高资源利用率以降低功耗要求:

(1)串行化;

(2)资源共享;

(3)逻辑优化;

8.D 可以用语句x[0]=0;为数组所有元素赋初值0。选项错误

3下次来分析填空题

提示:欢迎大家多多交流