笔试

联发科技笔试内容考试比较全面,对verilog语法的掌握,验证方法论,设计方法论,低功耗,跨时钟域,复位,C语言等均有涉猎

举例说明同步复位和异步复位,什么情况下使用异步复位同步释放,举一个异步复位同步释放的列子:

什么情况下要用异步复位同步释放

未在本模块时钟域做过“异步复位,同步释放”处理的复位信号,提供给本模块做异步复位使用时,都需要做“异步复位,同步释放”处理。常见于系统内两部件不在同一时钟域的情况下。

只是拉高的信号打两拍,拉低的信号,也就是复位信号有效的时候,该复位就复位,该干嘛干嘛,我们不用去管它

动态功耗和静态功耗分别指哪些,可以通过什么方法降低?

动态功耗和静态功耗

动态功耗:开关功耗和短路功耗,开关功耗即负载电容充电放电产生的功耗,短路功耗为0-1/1-0变换过程中npmos管同时导通产生的功耗

静态功耗:漏电流功耗 想减少动态功耗,那么方法就是:

- 降低电压;

- 降低翻转率;

- 减少负载电容;

什么叫input_delay,什么是output_delay?可以通过作图等方式来解释

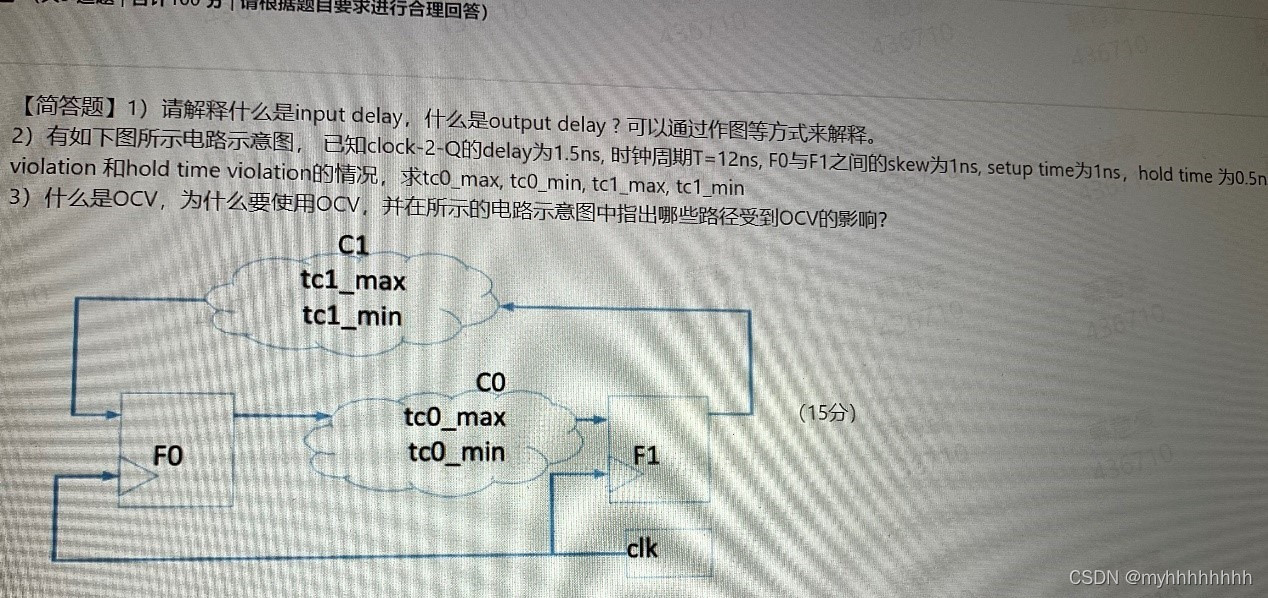

有如下图所示的电路图,已知clock-2-q的delay是1.5ns,时钟周期T=12ns,F0与F1之间的skew是1ns,set up time为1ns,hold time是0.5ns,在考虑setup violation和hold violation的情况下,求tc0_max,tc0_min,tc1_max,tc1_min

什么是OCV,为什么要使用OCV,电路中的哪些路径受到OCV的影响

OCV:全芯片变化分析模式,on-chip variation mode

为什么要使用OCV?因为制造工艺的限制,同一芯片上不同位置的MOS晶体管的性能会有一些差异。库中的PVT是一个"点",比如1.2V,250℃,工艺1.0。

但实际芯片的PVT永远不会落在一个点上,而是一个范围;比如说有时序关系的几个cell,可能这几个cell的PVT是1.18V,20℃,工艺0.98。而那个cell的PVT是1.21V,35℃,工艺1.01。这些cell的PVT都不在那个点上,怎么去分析呢?这时候就需要OCV了。

STA三种模式的理解和特点

单一模式,最好最坏分析模式,全芯片变化分析模式,这三种模式会影响时钟路径和数据路径

正则表达式的使用和字符匹配

一面

同步FIFO的目的是什么?

写进去的和读出来的速度不一样,才需要缓存,一样就不需要缓存了。

异步FIFO深度36可以实现吗,格雷码和二进制码转换

如果FIFO深度不是2的整次幂,那么地址从最大跳变到0时,相应的格雷码地址变化就不止1bit了,这样会增加亚稳态的概率。

格雷码是对控制信号进行控制的,异步FIFO的本质,没有对数据本身做格雷码,fifo的空满状态,对控制信号采错了,只会影响数据的延时,但是不会改变数据本身的值。

建立时间保持时间不满足的解决办法

建立时间不满足:pipeline做成流水线,重定时,

保持时间不满足:传输路径上插入buffer

二面

一面未通过,结束在一面上