笔者作为一名FPGA小菜,但仍然孜孜不倦的前进着(其实是被push)。再调用rom核(Distributed Memory generator)使用时,出现了一些小问题,仅已此篇博文来记录自己的写代码的沙雕日常。

总结:在给rom地址赋值时,不要使用阻塞赋值,会使得仿真时出现地址值与rom输出数据值同步的情况,而不是正常的延时一个clk,也许上板后错误会更加离谱。

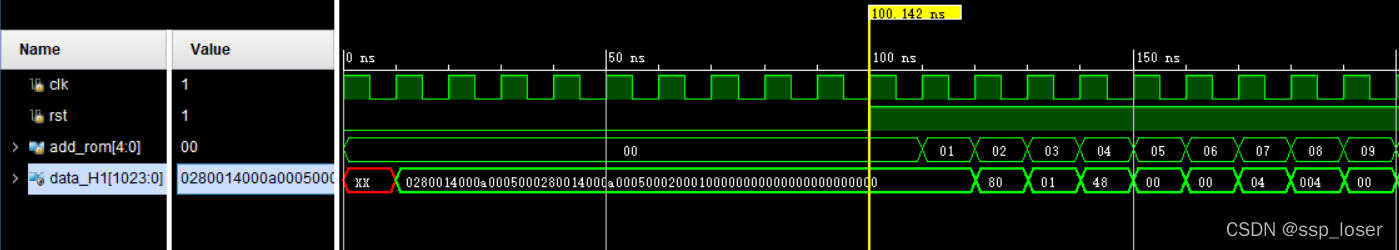

1. 阻塞赋值代码及仿真图如下:

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

add_rom = 5'd0 ;

end

else

begin

add_rom = add_rom + 5'd1 ;

end

end

ROM1 H1 (

.a(add_rom), // input wire [4 : 0] a

.clk(clk), // input wire clk

.spo(data_H1) // output wire [1023 : 0] spo

);

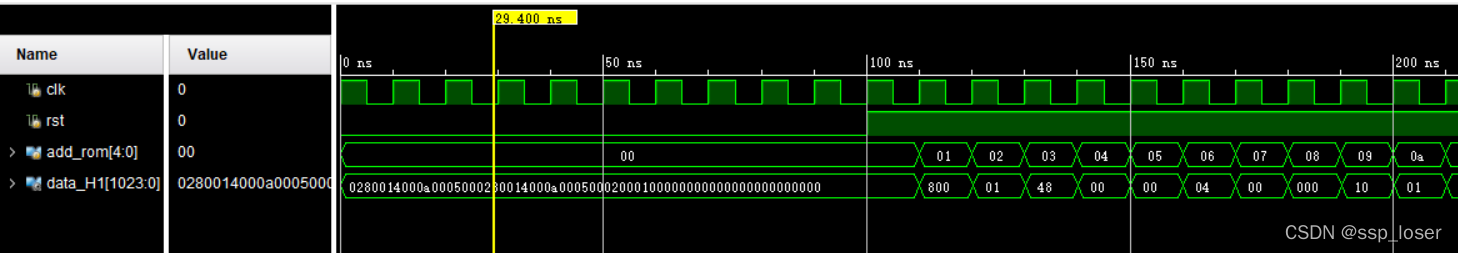

?2. 非阻塞赋值代码及仿真图如下:

always@(posedge clk or negedge rst)

begin

if(!rst)

begin

add_rom <= 5'd0 ;

end

else

begin

add_rom <= add_rom + 5'd1 ;

end

end

ROM1 H1 (

.a(add_rom), // input wire [4 : 0] a

.clk(clk), // input wire clk

.spo(data_H1) // output wire [1023 : 0] spo

);