目录

一. UFS Hibernate 简介

Hibernate是一种Unipro的状态,这个Hibernate 进出的流程是在M-PHY定义的。

Hibernate 是一种 UniPro 状态,其中 PHY 处于 HIBERNATE_STATE,UniPro 堆栈保持 只有最小的一组功能处于活动状态。 UniPro 堆栈保留每个堆栈层定义的最小状态。 在休眠(Hibernate )期间,UniPro 堆栈无法进行应用级数据传输/通信, 并且应用程序级接口的原语 T_CO_SAP 具有未定义的行为。 在休眠(Hibernate )的期间,DME 继续可供 DME 用户使用。

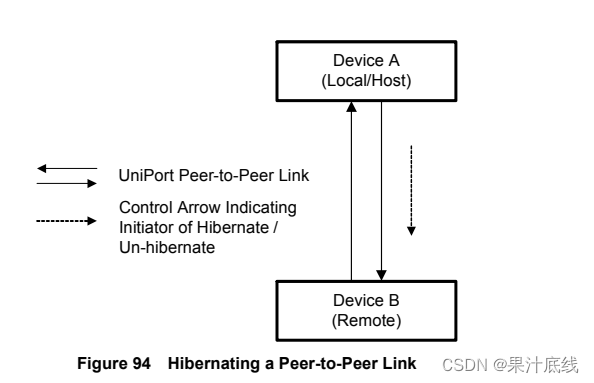

下图描述了链路休眠,其中一个设备(通常是主机设备)启动链路休眠 使用远程设备。

UFS 协议分析仪抓取PA通过分析Unipro数据包可以深入理解Hibernate进出的整个流程。

二 . 从UFS 协议来看UFS Hibernate

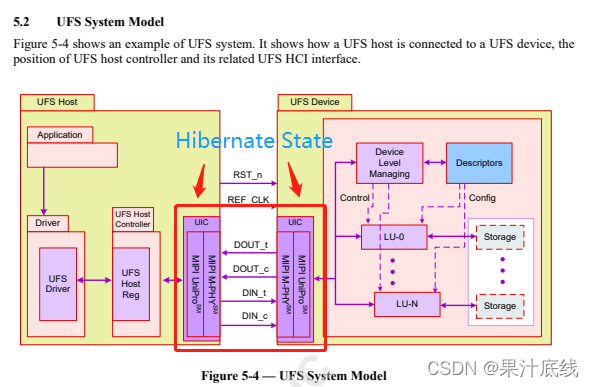

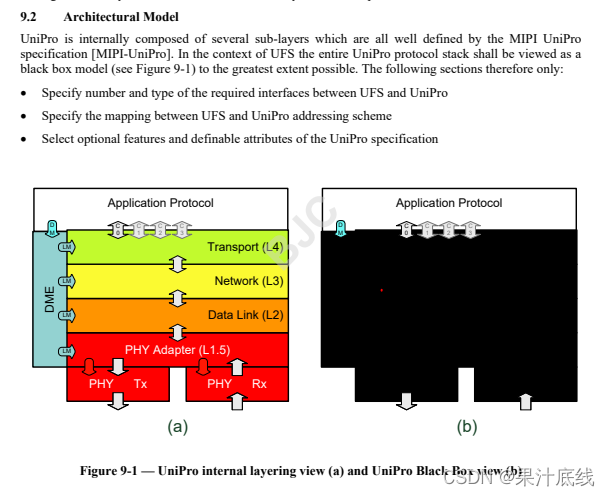

从UFS 协议层来看的话UFS Hibernate是通过Unipro和M-PHY层接口交互的,Unipro层和M-PHY统称为UIC层。

UFS层和UIC层关于Hibernate流程交互的命令是DME命令,?DME_HIBERNATE_ENTER / DME_HIBERNATE_EXIT。

下面是DME Hibernate命令的具体介绍:

DME_HIBERNATE_ENTER/DME_HIBERNATE_EXIT

(1)允许将整个链路(Link)的环境放到Hibernate Power Mode, 并且允许唤醒整个链路(Link)?起来

(2)影响本地和对等的Uniport(UniPro L1.5-L4 and M-PHY)

Note: 退出休眠后所有 UniPro 传输层属性(包括 L4 T_PeerDeviceID、 L4 T_PeerCPortID、L4 T_ConnectionState 等)将被重置为其重置值。 所有必需的属性 必须在两端正确恢复,才能恢复通信。

三. 从Unipro协议来看UFS Hibernate

5.7.13 PA Hibernate

Hibernate 与正常的电源模式更改操作分开。本节介绍hibernate enter和hibernate exit过程。

hibernate enter状态时,会存储当前的电源模式配置,包括 M-PHY 设置和通道计数信息。 exiting hibernate时它们会自动恢复。

PA 层延迟 exit hibernate操作,直到 HIBERNATE_TIMER 到期。

5.7.13.1 Entering Hibernate

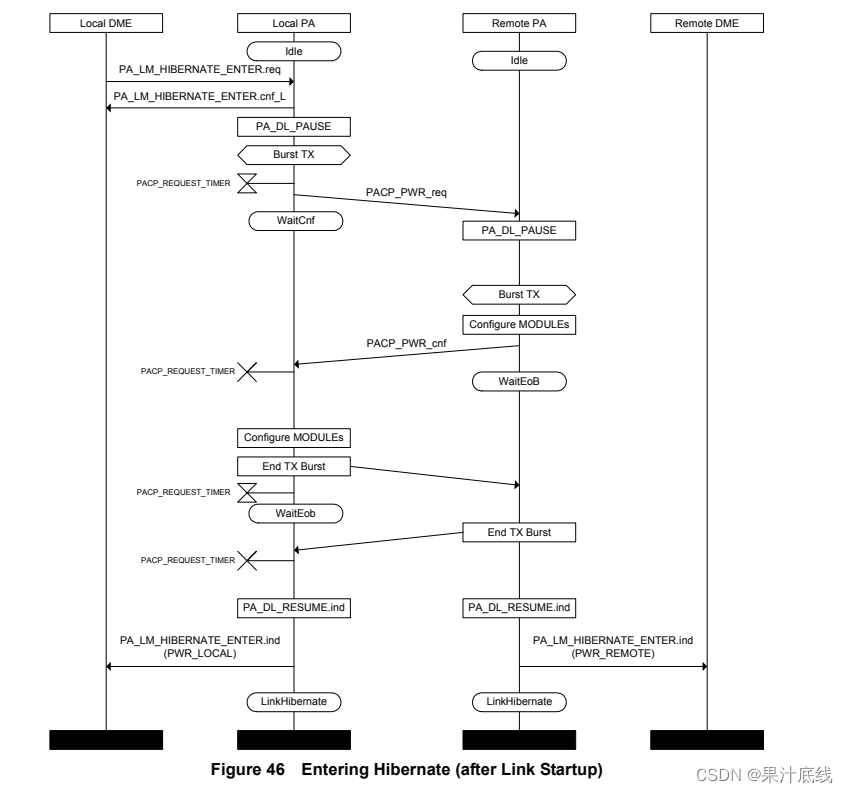

DME 向 PA 层发出 PA_LM_HIBERNATE_ENTER.req 原语以使 PA 层进入hibernate状态。 如果 PA 层不忙于另一个Power Mode更改操作,它应使用参数设置为 SUCCESS 的 PA_LM_HIBERNATE_ENTER.cnf_L 原语进行响应。 否则,它应以设置为 FAILURE 的参数响应。

当上述程序流程成功完成时,PA 层应向请求的 DME 发出参数设置为 PWR_LOCAL 的 PA_LM_HIBERNATE_ENTER.ind 原语。 对等 PA 层应向对等 DME 发出参数设置为 PWR_REMOTE 的 PA_LM_HIBERNATE_ENTER.ind 原语。 在错误情况下,原语具有其他状态,例如 PWR_BUSY 或 PWR_FATAL_ERROR。

成功完成该过程后,双向链路处于 HIBERNATE_STATE 状态,M-PHY MODULE 处于 HIBERN8 状态。 M-RX 的静噪检测可以在除逻辑通道 0 之外的所有通道上关闭,以节省功耗。

该过程如图 46 所示。在内部,PA 层应使用与第 5.7.12 节中指定的相同的链路配置过程,包括能力检查、错误和重试处理、M-PHY 和媒体转换器配置,并进行以下修改:

? DME 使用 PA_LM_HIBERNATE_ENTER.req 原语而不是使用属性

? PA 层使用 PA_LM_HIBERNATE_ENTER.cnf_L 表示接受休眠 要求

? PA 层使用 PA_LM_HIBERNATE_ENTER.ind 原语指示状态

? PACP_PWR_req 和 PACP_PWR_cnf 帧中的用户数据未使用,也未转发到 DME(参见第 5.7.12.4 节)

? 进入休眠状态永远不会因为无效配置或能力检查而失败

? 对于所有活动的 M-TX,TX_HIBERN8_Control 应设置为 ENTER,TX_LCC_Sequencer 应设置为 LCC WRITE-ATTRIBUTE 请求,其他属性不应设置

? 对于所有活动的 M-RX,RX_Enter_HIBERN8 应设置为 YES,其他属性不应设置

并发和错误恢复方法与正常的链路配置过程相同。 如果链路启动序列尚未启动,则 PA_LM_HIBERNATE_ENTER.req 原语应使 PA 层将所有可用的 M-RX 通道设置为 HIBERNATE_STATE,而不是使用链路配置过程。PA 层应生成 PA_LM_HIBERNATE_ENTER.cnf_L 和 PA_LM_HIBERNATE_ENTER.ind 原语,如前所述

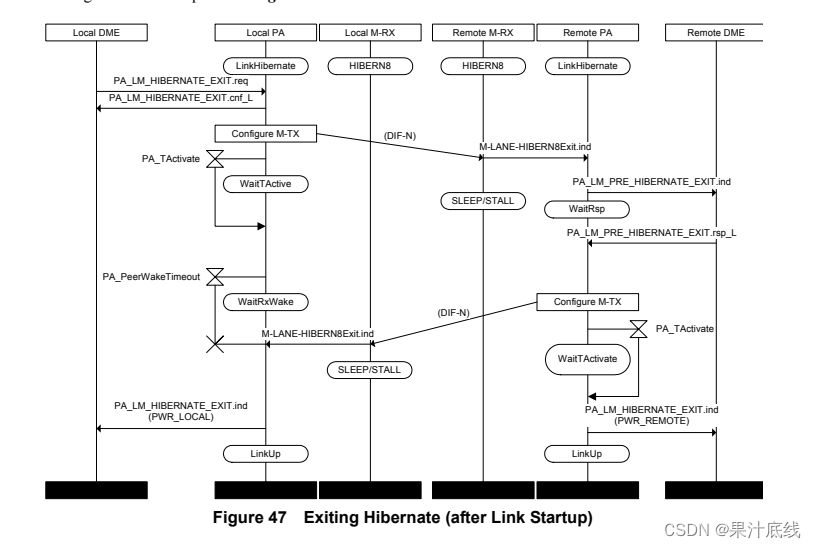

5.7.13.3 Exiting Hibernate

DME 可以通过发出 PA_LM_HIBERNATE_EXIT.req 原语来请求 PA 层exit hibernate。

PA 层应使用 PA_LM_HIBERNATE_EXIT.cnf_L 原语确认请求。 当exit hibernate程序流程完成时,本地 PA 层应发出 PA_LM_HIBERNATE_EXIT.ind 参数设置为 PWR_LOCAL 的本地 DME 原语。 类似地,当远程 PA 层检测到hibernate结束时,它应向远程 DME 发出 PA_LM_HIBERNATE_EXIT.ind 原语,参数设置为 PWR_REMOTE。 PA_LM_HIBERNATE_EXIT.ind 原语表示链路已恢复并且正在使用hibernation前的活动配置。

PA 层使用 M-PHY 信令退出 HIBERNATE_STATE。首先,应通过将 TX_HIBERN8_Control 设置为 EXIT 来唤醒所有活动的 TX 通道。这导致 M-TX 开始将 DIF-N 驱动到通道。本地 PA 层应等待 PA_TActivate,然后启动设置为 PA_PeerWakeTimeout 的计时器 WAIT_HIBERN8EXIT_TIMER。

当远程 M-RX 检测到 DIF-N 时,它会唤醒并使用 M-LANEHIBERN8Exit.ind 原语通知远程 PA 层。 M-LANE-HIBERN8Exit.ind 原语应使远程 PA 层唤醒并向 DME 发出 PA_LM_PRE_HIBERNATE_EXIT.ind。 DME 应根据第 9.5.2 节对 DL、N 和 T 层进行休眠退出准备并发布 PA_LM_PRE_HIBERNATE_EXIT.rsp_L 到远程 PA 层。 当远程 PA 层接收到 PA_LM_PRE_HIBERNATE_EXIT.rsp_L 时,它将通过在所有活动通道上将 TX_HIBERN8_Control 设置为 EXIT 来唤醒其 M-TX。 远程 PA TX 应启动一个设置为 PA_TActivate 的定时器。 如果定时器超时,表明hibernate 已经结束,PA 层将发送 PA_LM_HIBERNATE_EXIT.ind(PWR_REMOTE) 到远程 DME。 在接收到 PA_LM_PRE_HIBERNATE_EXIT.rsp_L 之后,远程 PA RX 应该能够从 M-RX 接收符号数据并将其转发到 DL 层。

当本地 M-RX 检测到 DIF-N 时,它会唤醒并向本地 PA 层发送一个 M-LANE-HIBERN8Exit.ind 原语。 本地 PA 层应停止 WAIT_HIBERN8EXIT_TIMER 并通过发送本地 DME PA_LM_HIBERNATE_EXIT.ind(PWR_LOCAL) 指示hibernate 已结束。

如果 WAIT_HIBERN8EXIT_TIMER 到期,则hibernate exit失败,本地 PA 层应向本地 DME 发出 PA_LM_HIBERNATE_EXIT.ind(PWR_FATAL_ERROR)。 此时,Link 处于未知状态,可能无法运行。

在本地 PA 层发出 PA_LM_HIBERNATE_EXIT.ind(PWR_LOCAL) 之后,本地 DL 层可以立即向本地 PA 层请求传输。 在远程 PA TX 仍等待 PA_TActivate 期间,本地 PA 授予的此传输可能导致 M-LANE-PREPARE.ind 和 M-LANE-SYMBOL.ind 到达远程 PA 层。 PA_LM_PRE_HIBERNATE_EXIT.ind 和 PA_LM_PRE_HIBERNATE_EXIT.rsp_L 之间由远程 DME 发起的规定应确保远程 DL 层应正确接收此数据。 然而,远程 DL 层应仅在 PA_LM_HIBERNATE_EXIT.ind(PWR_REMOTE) 之后请求来自远程 PA 的传输。

如果Link Startup Sequence尚未启动,则 PA_LM_HIBERNATE_EXIT.req 原语将导致 PA 层跳过前面描述的唤醒过程,即驱动 DIF-N 并等待传入的 DIF-N。

类似地,如果 PA 层在链路启动序列尚未开始时接收到 M-LANE-HIBERN8Exit.ind 原语,则 PA 层应跳过前面描述的唤醒过程,即驱动 DIF-N。 如前所述,PA 层应生成 PA_LM_HIBERNATE_EXIT.cnf_L 和 PA_LM_HIBERNATE_EXIT.ind 原语。

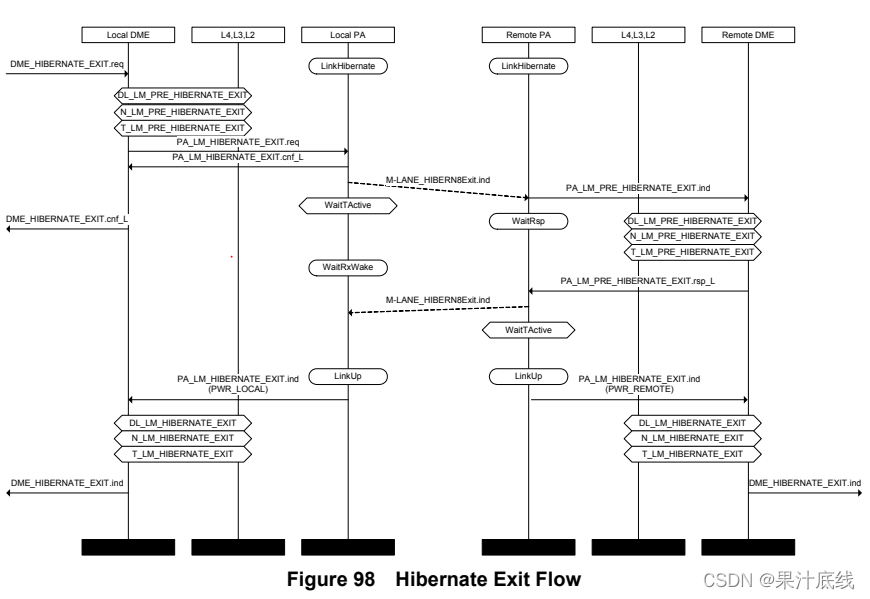

Exiting hibernate 如图 47 所示

9.5 Hibernate (M-PHY only)

9.5.1 Entering Hibernate

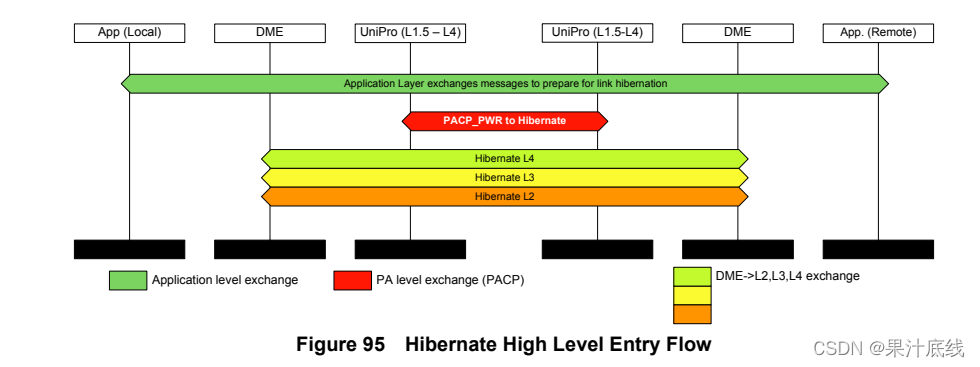

图 95 显示了进入hibernate状态的高级 MSC 流程。 以下部分描述了显示 SAP 原语的详细流程。 图 95 中的颜色编码将hibernate 进入流程向下划分为需要在应用层、PA 层和 DME 交换数据的步骤。

Hibernate 进入流程分两个关键阶段进行解释:

? 阶段 1,描述进入流程,直到应用程序准备好开始进入hibernation 过程。

? 阶段 2,描述应用程序指示 UniPro 堆栈后的进入流程进入hibernation状态。

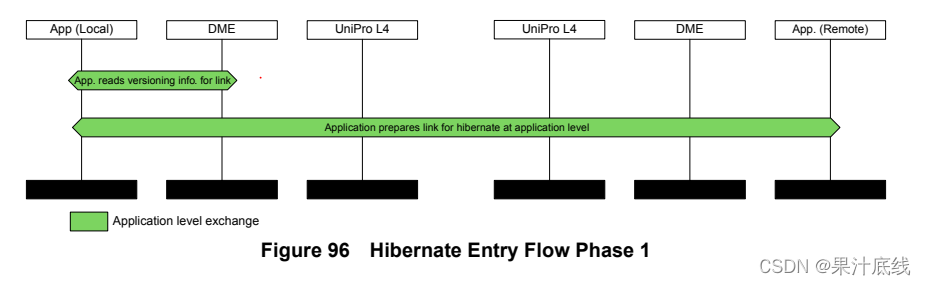

9.5.1.1 Hibernate Entry Phase 1 Flow for Peer-to-Peer (P2P) Devices

图 96 描绘了对等设备的Hibernate 进入阶段 1 MSC 流程。 在 UniPro 堆栈可以进入hibernate 状态之前,应用程序应在应用程序级别交换hibernate 进入的先决条件消息。

附件 F 提供了这些前置条件消息的信息性描述。 这些推荐的先决条件保证 UniPro 堆栈中没有未完成的数据。 一旦应用程序级别的先决条件成功完成,应用程序就可以hibernate UniPro 堆栈

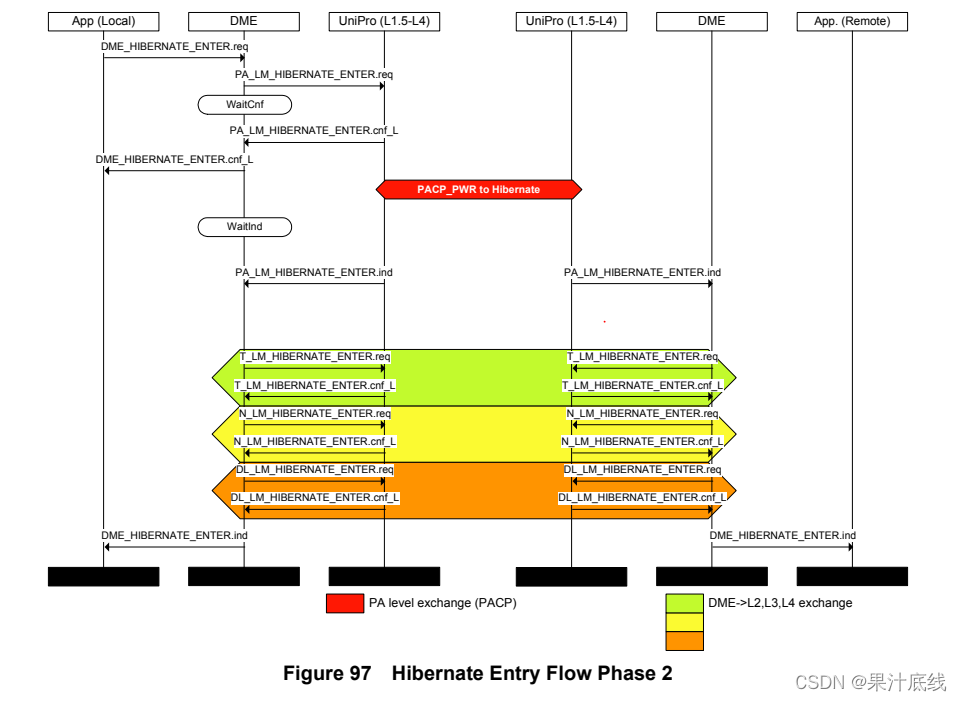

?9.5.1.2 Hibernate Entry Phase 2 Flow

图 97 描述了 UniPro 中的Hibernate 进入阶段 2 流程。 一旦应用程序级别的先决条件完成,应用程序将启动第 2 阶段,向 DME 发送 DME_HIBERNATE_ENTER.req。 DME 反过来通过向本地 PA 层发送 PA_LM_HIBERNATE_ENTER.req SAP 原语来启动 UniPro 堆栈休眠。 本地 PA 层接收此请求并使用 PACP 协议将 M-PHY 链路置于Hibernate 状态(PACP 协议的详细说明可在第 5.7.7 节中找到)。

一旦 PA 层成功hibernated the M-PHY 链路,本地和远程 UniPro 堆栈(L4 到 L2)的后续层应由 DME 通过发送 <layer-identifer>_LM_HIBERNATE_ENTER.req 对应层的 SAP 原语。

9.5.2 Exiting Hibernate (Un-hibernate)

图 98 显示了hibernate 退出流程。 应用程序应负责解除 UniPro Link 的-hibernat状态。

应用程序应通过向 DME 发送 DME_HIBERNATE_EXIT.req 来启动hibernate 退出。 DME 反过来通过向本地 PA 层发送 PA_LM_HIBERNATE_EXIT.req SAP 原语来启动 UniPro 堆栈取消hibernate 。 本地 PA 层接收此请求并使用 PACP 协议取消 M-PHY 链路的hibernate (有关 PACP 协议的详细说明,请参见第 5 节)。

一旦 PA 层成功取消M-PHY 链路的hibernate 状态,DME 将取消 本地和远程 UniPro 堆栈的后续层 (L4到L2)的hibernate状态,通过发送一个 <层标识符>_LM_HIBERNATE_EXIT.req 原始到各自的层。

Hibernate 前退出服务原语,<layer-identifier>_LM_PRE_HIBERNATE_EXIT,可以从 DME 添加到适当的层,以便允许层有更多时间从Hibernate 状态唤醒(参见图 98)。 一般来说, <layer-identifier>_LM_PRE_HIBERNATE_EXIT 原语应用于从Hibernate 状态唤醒层(接收路径),<layer-identifier>_LM_HIBERNATE_EXIT 原语用于在唤醒后激活层(传输路径)。 PA_LM_PRE_HIBERNATE_EXIT.ind 原语从 PA 层发送到 DME,用于向 DME 指示在远程启动的Hibernate 退出过程期间执行 <layer-identifier>_LM_PRE_HIBERNATE_EXIT 的正确时间。 这些层可能会在 PA_LM_PRE_HIBERNATE_EXIT.rsp_L 和 <layer-identifier>_LM_HIBERNATE_EXIT 请求,它们应该能够正确处理该数据,独立于 <layer-identifier>_LM_PRE_HIBERNATE_EXIT 的实现。

四. 从M-PHY协议部分来看UFS Hibernate

4 Architecture and Operation

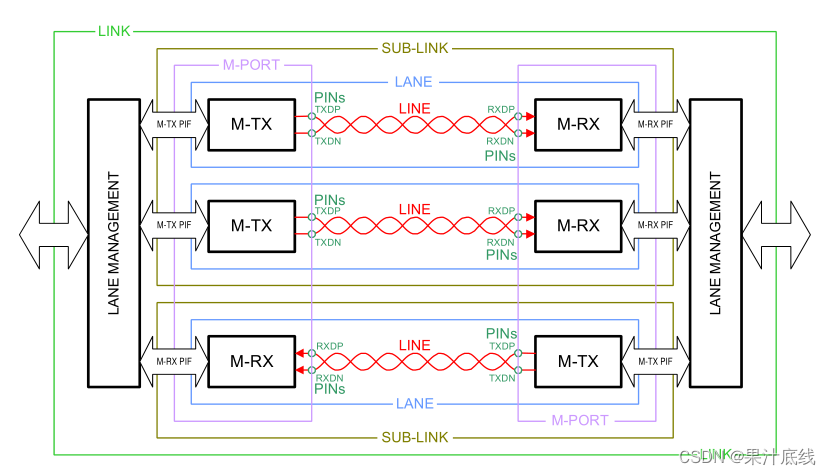

LANE 是一个单向、单信号的物理传输通道,用于从 A 点到 B 点。一个 LANE 由一个 M-PHY 发送模块 (M-TX)、一个 M-PHY 接收 MODULE (M-RX) 和 LINE,它是 M-TX 和 M-RX 之间的点对点互连。 一个 M-TX 或 M-RX 分别只有一个差分电输出或输入 LINE 接口, 对应于每个 MODULE 的两个信令 PIN。 PIN 分别表示为 DP 和 DN, 其中 DP 定义为差分信号的正节点。 可以使用可选前缀 TX 或 RX 分别指示 M-TX 或 M-RX PIN。 本文档中的规格在 PIN 中定义 M-TX 和 M-RX,以及通过 LINE 的 PIN 到 PIN。 图1说明了之间的关系 M-PHY LINK 的不同部分

4.6 State Machines

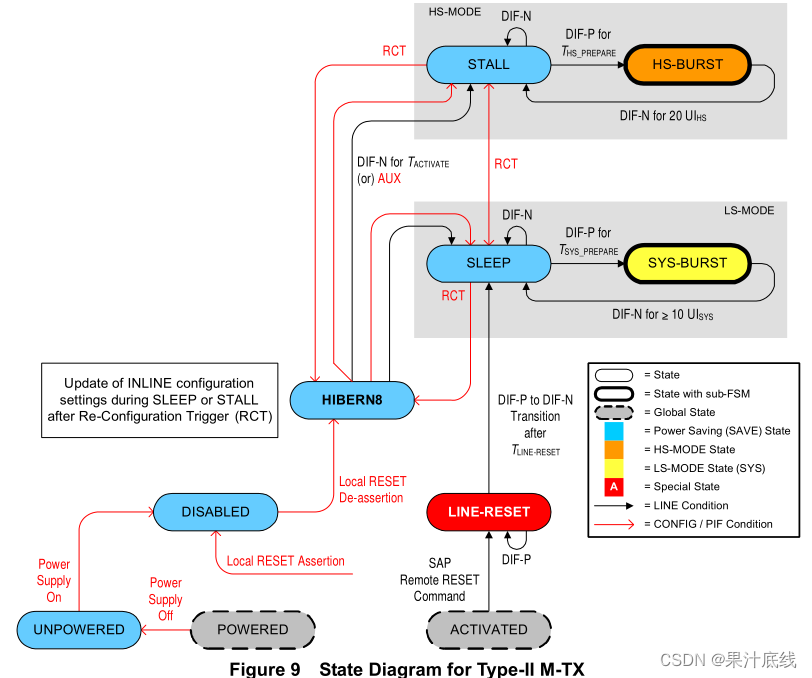

这两种类型的 MODULE 会产生两个备用状态机,用于具有不同应用程序边界条件的不同应用程序。不同类型的 M-PORT 不可互操作。 两种状态机都允许 LS-MODE 和 HS-MODE 操作,每个都包括一个 BURST 数据 传输和省电状态。通过使用这些模式以及模式内的 GEAR 可以实现性能可扩展性。 两种状态机的主要区别如下:

? LS-BURST 的信令方案(PWM 与 SYS)

? 支持 LINE 中的媒体转换器 (MC)

? 关于辅助信号可用性的假设(例如参考时钟、复位) 两个状态机之间的高级共性如下:

? 用于在 Mbps 速度范围内传输的 LS-MODE

? 用于以 Gbps 速率传输的 HS-MODE

? LS-MODE 和 HS-MODE 中的单独省电状态 SLEEP 和 STALL

? 超低功耗状态HIBERN8 ? BURST 及其省电状态之间的 LINE 控制状态切换

? 协议辅助配置机制

尽管有高级别的共性,但两种 MODULE 类型的这些方面并不相同,有时甚至不相似,例如带有 PWM(I 型)与 SYS(II 型)信号的 LS-MODE。 LANE 中的状态机对于 M-TX 和 M-RX 是相似的,但是状态转换条件从两个角度来看是不同的。因此,为 M-TX 和 M-RX 提供了单独的状态机。

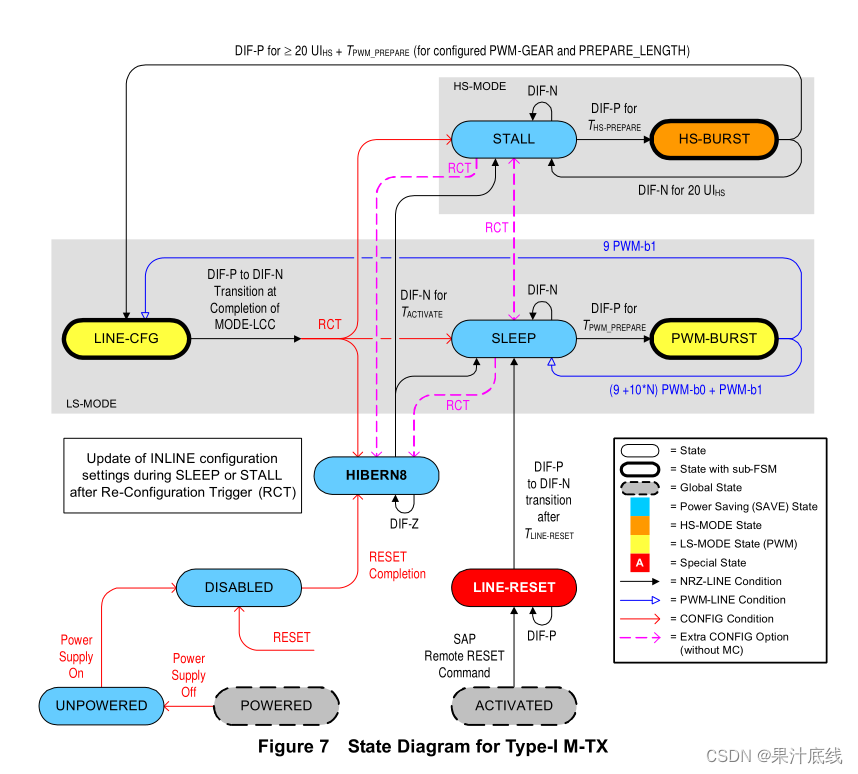

4.6.1 State Machine for a Type-I MODULE

Type-I MODULE 的具体功能包括:

? PWM 自时钟 LS 信号

? 使用独立的本地参考时钟运行; 可能会受益于共享参考时钟,如果 可用的

? LANE 内的完全嵌入式控制(不需要额外的辅助信号)

? 支持 LINE 中的媒体转换器

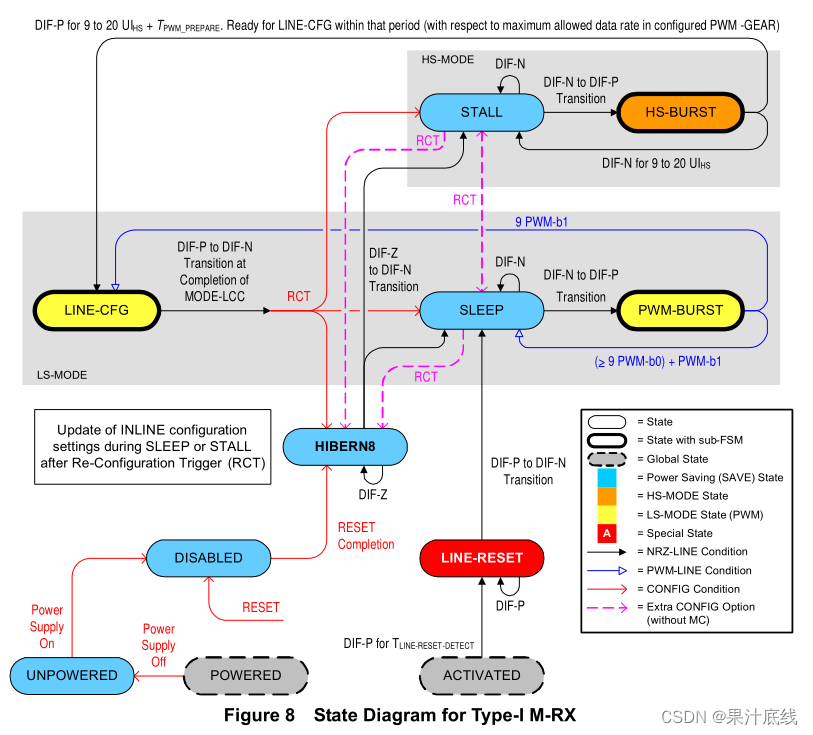

Type-I M-TX 和 M-RX 的状态机分别如图 7 和图 8 所示,并在以下部分中进行说明

4.6.2 State Machine for a Type-II MODULE

Type-II MODULE 的具体功能包括:

? 系统时钟同步 LS 信令 (SYS)

? 需要共享参考时钟

? LANE 中的部分嵌入式控制(某些状态转换需要额外的辅助 控制信号)

Type-II M-TX 和 M-RX 的状态机分别如图 9 和图 10 所示,并且 在后面的章节中解释。

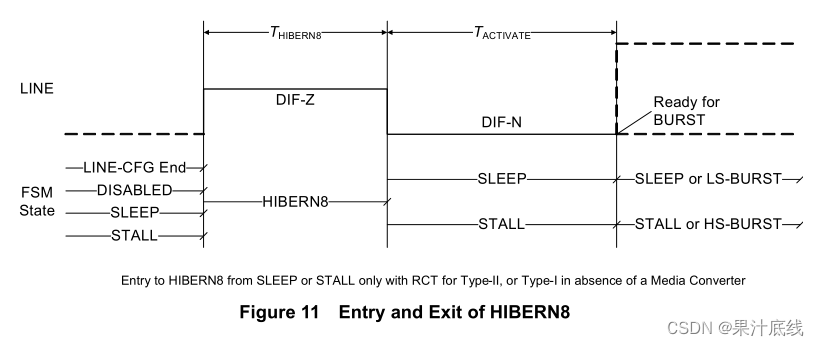

4.7.1.3 HIBERN8

HIBERN8 状态可实现超低功耗,同时保持配置设置。 模块应支持 HIBERN8。 M-TX 应在 HIBERN8 中为高阻抗,而 M-RX 应将 LINE 保持在 DIF-Z。 在这些条件下,M-RX 被认为处于静噪状态。 当从 LS-MODE 或 HS-MODE 进入 HIBERN8 时,协议层不应在 HIBERN8 的最小周期 T HIBERN8 之前请求 MODULE 退出 HIBERN8,该周期定义为本地 TX_Hibern8Time_Capability 和远程 RX_Hibern8Time_Capability 中的较大者。 如果本地 M-TX 支持 Advanced Granularity Capability,则 T HIBERN8 应按表 5 中的描述计算。如果远程 M-RX 支持 Advanced Granularity Capability 并且 RX_Advanced_Hibern8Time_Capability 小于 RX_Hibern8Time Capability,则应使用它来计算 T HIBERN8,如图所示 在表 5 中。

在从 SLEEP/STALL 到 HIBERN8 的状态转换时,观察 DIF-Z 之前的 LINE 状态不应被解释为 HIBERN8 退出条件。对于从 ACTIVATED 进入 HIBERN8 的每个 LANE,协议应确保 M-RX 在 M-TX 之前进入 HIBERN8。

本地 M-TX 应在禁用去加重的情况下在 HIBERN8 退出时驱动 DIF-N 一段时间 T_ACTIVATE。在此期间,M-TX 的输出电阻应为 R SE_TX。如果不支持高级粒度能力,T_ACTIVATE 应符合远程 M-RX 的 RX_Min_ActivateTime_Capability。如果远程 M-RX 支持 Advanced Granularity Capability 并且 RX_Advanced_Min_ActivateTime_Capability 小于 RX_Min_ActivateTime_Capability,则它应用于 T ACTIVATE 的计算,如表 5 所示。对于嵌入式 HIBERN8 退出控制,M-RX 需要检测LINE 转换到 DIF-N 的非静噪状态。 Type-I MODULE 应使用嵌入式 HIBERN8 退出控制。对于 Type-II 模块,可以嵌入 HIBERN8 退出控制,或者使用辅助控制信号。请注意,静噪检测仅在 HIBERN8 中使用,因此对于所有其他状态可以禁用此功能。 LANE MODULE 在退出 HIBERN8 时变为 ACTIVATED,并应返回到配置的操作模式的省电状态并准备好 T ACTIVATE 内突发。

进入 HIBERN8 可以从 LINE-CFG、STALL、SLEEP 和 DISABLED 状态发生。通过配置控制从 LINE-CFG、STALL 或 SLEEP 状态进入 HIBERN8(参见表 51)。该机制在第 4.7.4.2.4 节中指定。请注意,当从 LINE-CFG 请求 HIBERN8 时,LINE 信号首先从 DIF-P 切换到 DIF-N,这会结束 LINE-CFG 并导致重新配置触发 (RCT)。 RCT 是在 LINE-CFG 结束后发生的内部驱动事件,由于同一 BURST 中的先前配置导致 LINE 信号从 DIF-N 切换到 DIF-Z,因此会启动到 HIBERN8 的转换。因此,HIBERN8 总是从 DIF-N LINE 状态进入。对于 LANE 中的 M-TX 和 M-RX,从 DISABLED 进入 HIBERN8 通常不会同时发生,因为它取决于 LANE 每一侧的 RESET 信号的独立时序。之前的信号和状态, HIBERN8 状态期间和之后的状态如图 11 所示。 当 RCT 在从 BURST 状态转换到 SAVE 状态后立即请求进入 HIBERN8 时,需要额外的时间。发布 TOB 后,M-TX 将驱动带有 DIF-N 的 LINE 用于 T HIBERN8_ENTER_TX 。

M-RX 将开始驱动 LINE 到 检测到 TOB 后 T HIBERN8_ENTER_RX 内的 DIF-Z。

五.参考资料

1.?Universal Flash Storage (UFS)?Version 2.2

2 .mipi alliance?Specification for Unified Protocol (UniPro SM)?Version 1.6?

3.?mipi alliance?Specification for M-PHY?Version 4.1