2022年6月14日

1. 部署开发环境

略。工作需要,TMS320C6678。

从今天开始学习DSP的知识。

后面会补充如何安装部署环境。

1.1 组件

1.1.1 SDK

-

MCSDK(CCSv5,CCSv6)+Path(全英文路径,无中文,无空格)

安装完之后,需要打一个补丁。 -

Pocessor SDK (CCSv6)

1.1.2 组件

- XDCTools

- SYS/BIOS

- NDK

- UIA

- XDAIS

- Framework Components

1.1.3 算法库

- DSPLIB

- MATHLIB

- IMGLIB

- VLIB

1.2 集成开发环境

- Code Composer Studio (CCSv5,CCSv6)

1.3 其他

1.3.1 编译器

CGT 7.4.x ,CGT 8.1.x

1.3.2 编码/解码算法库

-

视频

HEVC[H265],压缩效率高,计算量大。

H264 BP/MP/HP

MPEG4

JPEG

JPEG2000 -

语音

G711

G722/G722…1/G722.2

G726

G728

OPUS -

医学有关

-

电信有关

1.4 安装过程

1.4.1 下载CCS镜像

-官网,搜索CCS,下载相关版本。

https://www.ti.com.cn/tool/cn/download/CCSTUDIO

1.4.2 安装CCS镜像

- 如果安装过程中,提示VC++运行库安装失败,可以先安装VC++2008以及VC++2012运行库[32位],然后再安装CCSv5。

1.4.3 安装字体

- 推荐安装等宽字体,中英文宽度一致。

- 下载等宽字体,放到Windows的font文件夹中

- 在CCS软件中进行编码设置,字体设置。字体大小建议12号,脚本选择 中文GB2312。

1.4.4 修改主题

- 安装eclipse主题插件,Eclipse Marketplace,更新,搜索theme,

- 选择深色主题,保护眼睛。

1.4.5 菜单显示中文

- 安装eclipse的语言翻译,显示中文。

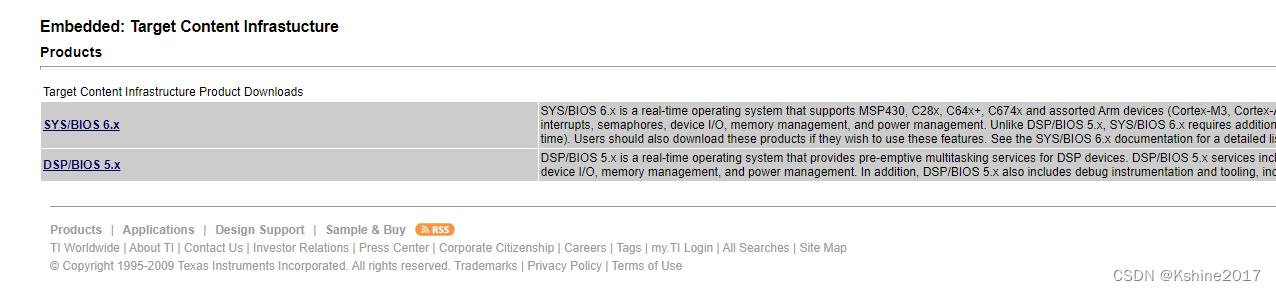

1.5 安装软件组件

嵌入式软件产品下载地址:https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/index.html

更老的一些软件:https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/legacy.html

1.5.1 TI-RTOS

https://www.ti.com.cn/tool/zh-cn/TI-RTOS-MCU?keyMatch=&tisearch=search-everything&usecase=software#downloads

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/tirtos/index.html

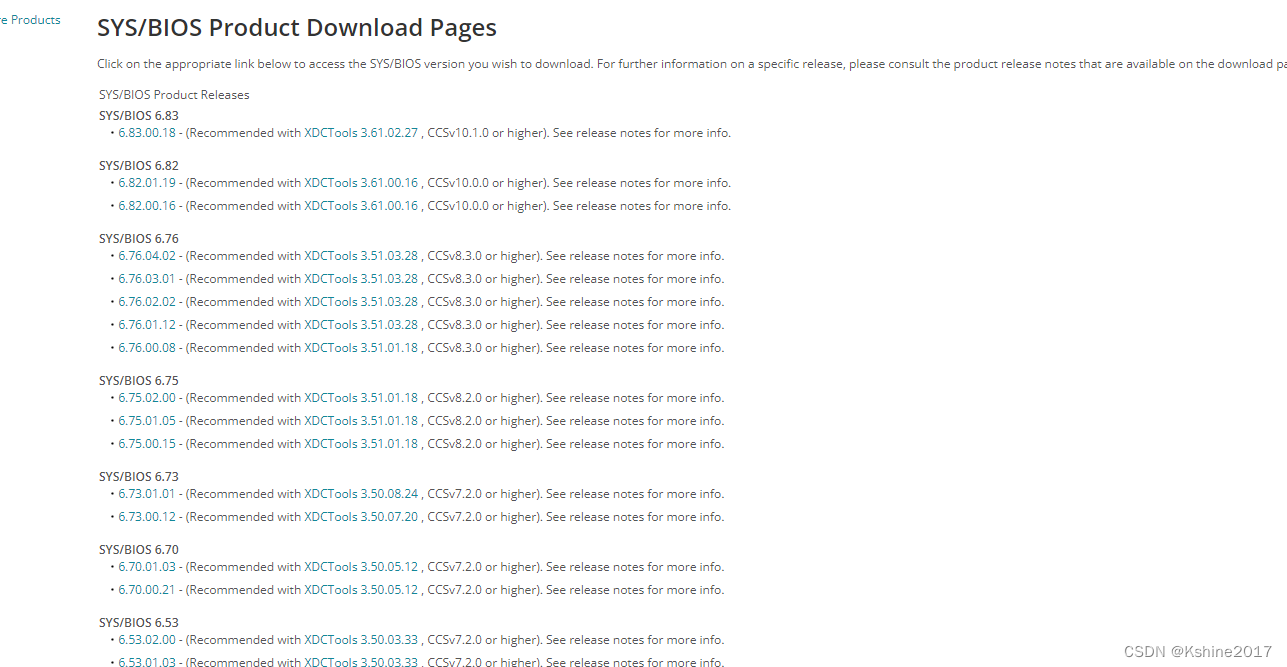

1.5.2 SYS/BIOS

https://www.ti.com.cn/tool/cn/SYSBIOS?keyMatch=SYS%20BIOS%20DOWNLOAD

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/bios/index.html

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/bios/sysbios/index.html

1.5.3 网络NDK

https://www.ti.com.cn/tool/zh-cn/NDKTCPIP?keyMatch=&tisearch=search-everything&usecase=software

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/ndk/index.html

1.5.4 UIA

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/uia/index.html

1.5.5 IPC

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/ipc/index.html

- 多核之间通信,多片之间通信。

- 已经不再更新

1.5.6 Multimedia Framework Products

-

Codec Engine 管理资源,框架

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/ce/index.html -

Framework components 提供抽象的接口

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/fc/index.html -

XDAIS,XDM算法

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/xdais/index.html

1.5.7 XDCtools 实时软件组件

https://software-dl.ti.com/dsps/dsps_public_sw/sdo_sb/targetcontent/rtsc/index.html

1.5.8 CGT编译器

https://www.ti.com/tool/TI-CGT

https://software-dl.ti.com/codegen/non-esd/downloads/download_archive.htm

1.6 软件库

1.6.1 MATHLIB

https://www.ti.com.cn/tool/cn/MATHLIB?keyMatch=MATHLIB#downloads

1.6.2 IQMath

- C64x+ IQMath 库 - 虚拟浮点引擎

https://www.ti.com.cn/tool/zh-cn/SPRC542?keyMatch=&tisearch=search-everything&usecase=partmatches

1.6.3 FastRTS

- 基本的数学运算的优化。

1.6.4 DSPLIB

- 数字信号处理,处理浮点

1.6.5 IMGLIB

- 图像处理,DCT变换,离散余弦变换

- 图像分析,直方图

1.6.6 VLB

- 更上层的图像处理

1.6.7 VICP

- 信号处理

1.6.8 VoLIB

- 声音处理库

1.6.9 FaxLIB

- 传真,编解码

1.6.10 AER/AEC

- 编解码

1.6.11 Codecs

- 编解码

- 语音,视频,图像编码

1.7 软件开发包

- MCSDK多核软件开发套件(比较老的)

- MCSDK-VIDEODEMO

- PROCESSOR-SDK-C667X

2. 基础知识

B站学习视频:北航电子信息工程学院王俊《DSP体系结构》

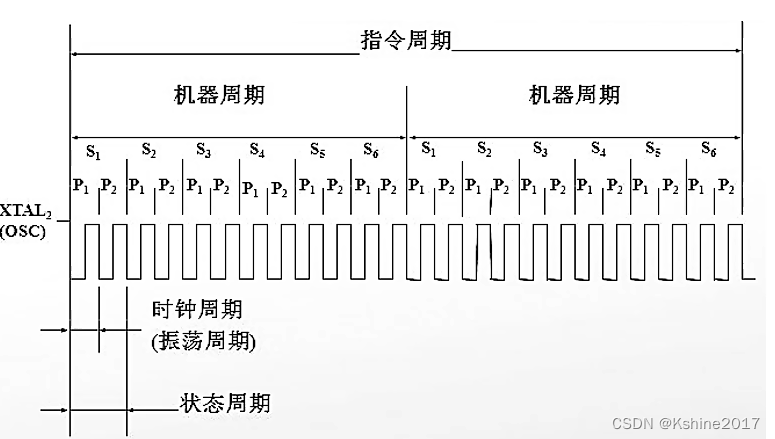

2.1 指令周期

冯诺依曼结构。

-

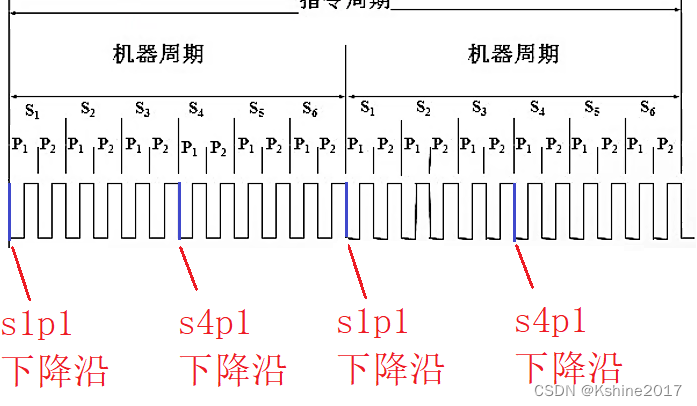

1个指令周期 = 1个或者多个机器周期。

-

1个机器周期 = 6个状态周期 = 12个时钟周期。6节(s)12拍(p)。

-

1个状态周期 = 2个时钟周期。

-

1个指令周期的执行过程:取指令,译码,执行,(写回)。

取指令:从数据寄存器MDR,经过总线,读取到指令寄存器IR中。

译码:指令译码器ID。将指令寄存器IR中的指令翻译一下。

执行:执行指令译码器ID给出的指令。 -

在s1p1和s4p1下降沿时,分别读一次指令(每次读取一个字节)。

-

不同的指令,指令的长度是不一样的,指令的执行周期也是不相同的。有单字节单周期,双字节单周期,单字节双周期,双字节双周期,双字节三周期。。。。。。

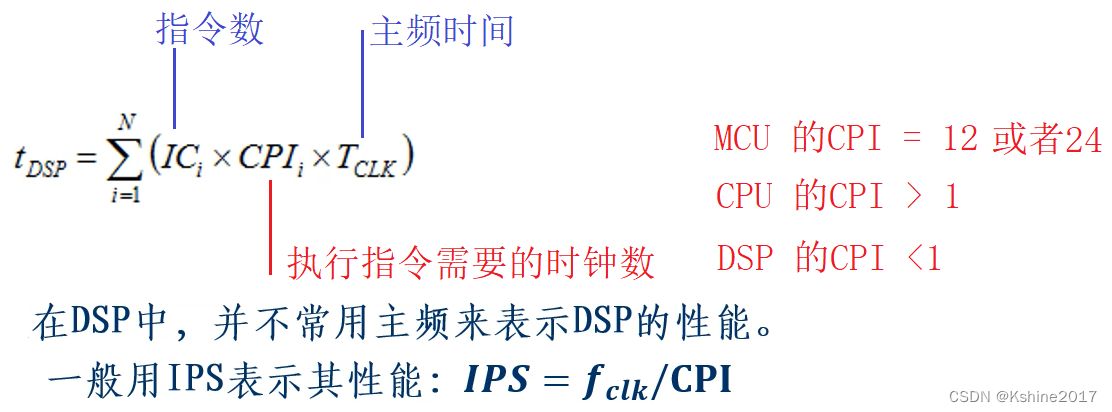

2.2 执行性能

-

在主频相同的情况下,CPI越小,性能越好。

-

时钟频率:反应DSP实现技术,生产工艺

-

CPI:反应DSP指令集结构,DSP体系结构。

-

IC:反应DSP指令集的结构和编译技术,以及编程水平。

-

指令周期,指的是执行一条指令所需要的时间。通常以ns为单位。

-

MAC时间,一次乘法和一次假发的时间。大部分DSP可以在一个指令周期内完成一次乘法和加法。

-

FFT执行时间,衡量DSP芯片运算能力的一个指标。

-

MIPS:即M+IPS。每秒执行百万条指令。

-

MFLOPS,每秒执行百万次浮点操作。

-

在实际应用中,tdsp时间必须要小于采样时间ts,

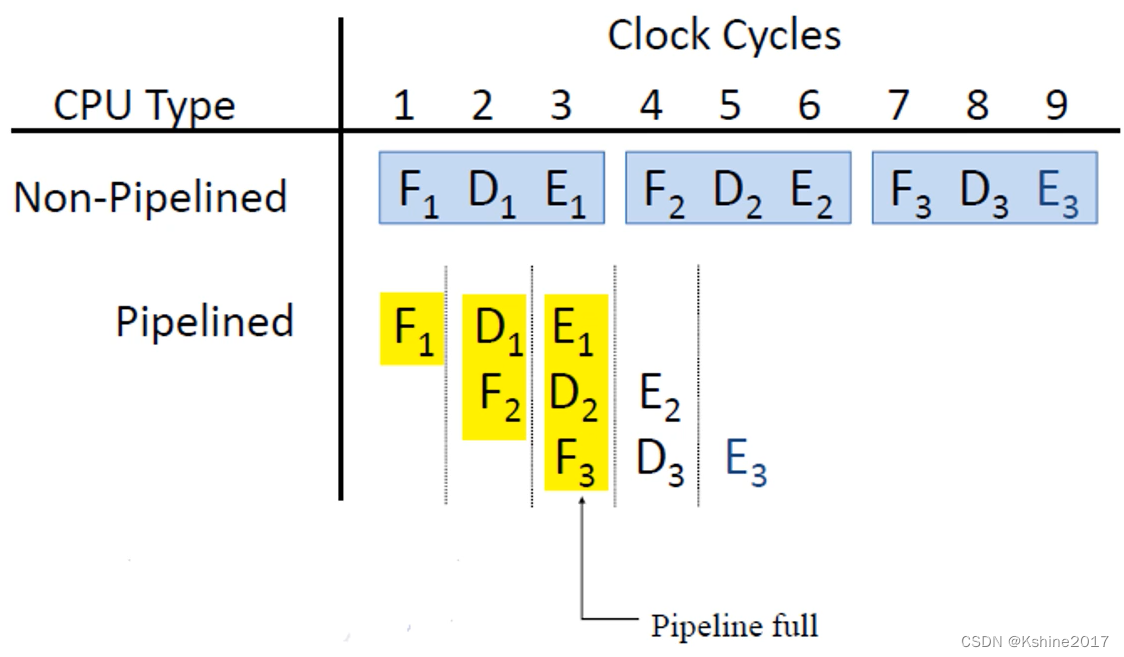

2.2 流水线

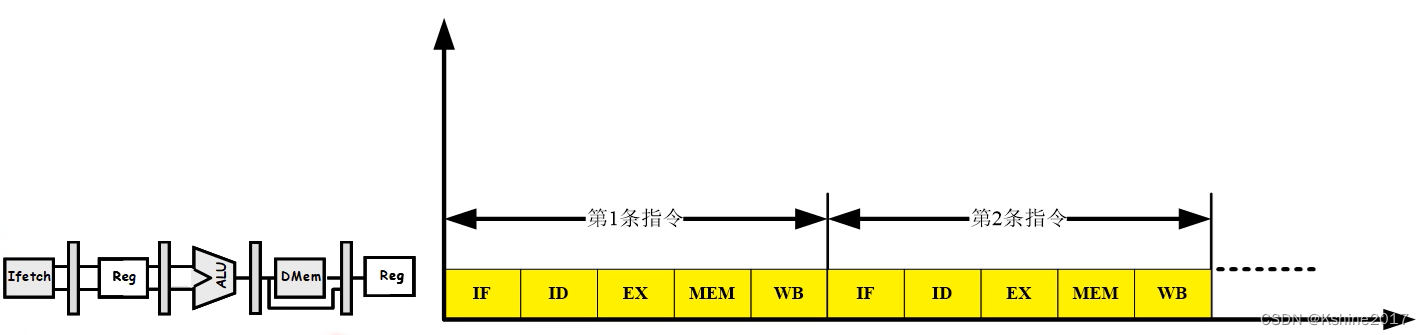

- PipeLine。

- 使用流水线的方式,将CPI=12(24)降到CPI=1。

2.2.1 流水线的类型

(1)按照功能的多少来分

单功能流水线,只能完成一个功能。

多功能流水线,可以完成不同的功能。

(2)按照同一时间内各段之间的连接方式

静态流水线,同一时刻,各段按照一种功能连接。

动态流水线,同一时刻,各段可以按照不同功能连接。

(3)按照片内流水线的级别来分

片内,指令流水线DLX,运算流水线(核内流水线,核间流水线)。

片间,多芯片并行处理机。

机间,多处理机并行处理,任务流水。

(4)按照数据表示来分

(5)按照是否有反馈回路来分

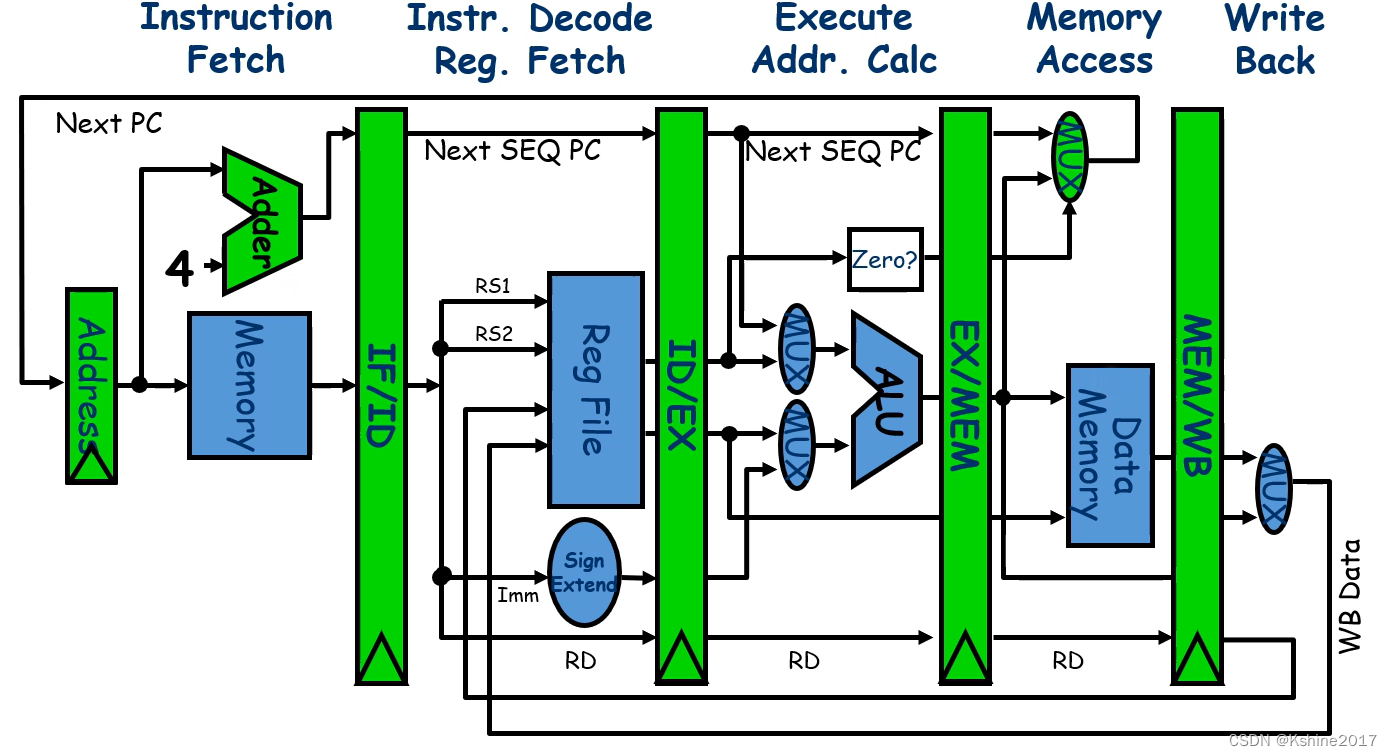

2.2.2 指令流水线DLX(RISC架构)

- 处理器的体系结构,取指令,译码,执行,访存,写回。

2.2.3 指令流水线竞争

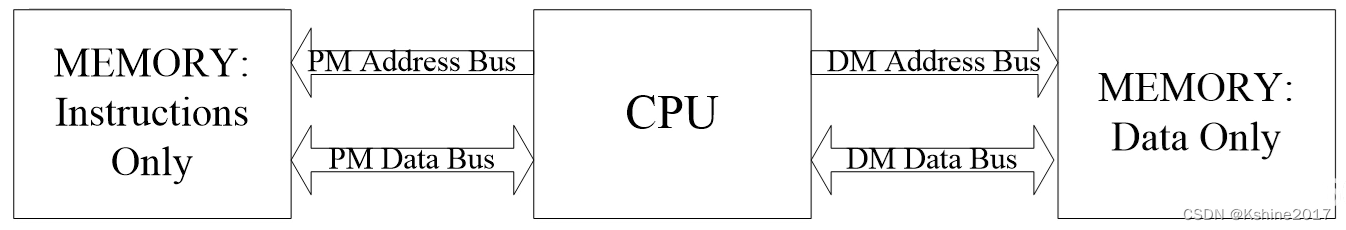

(1) 结构竞争,硬件资源无法满足指令流水线执行。

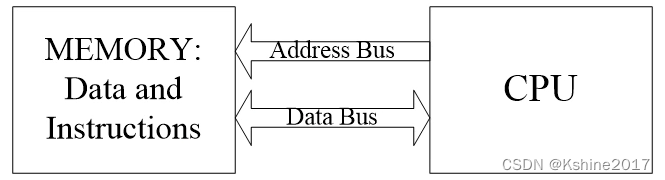

- 冯诺依曼结构只有一个总线,用于数据和指令的传输。

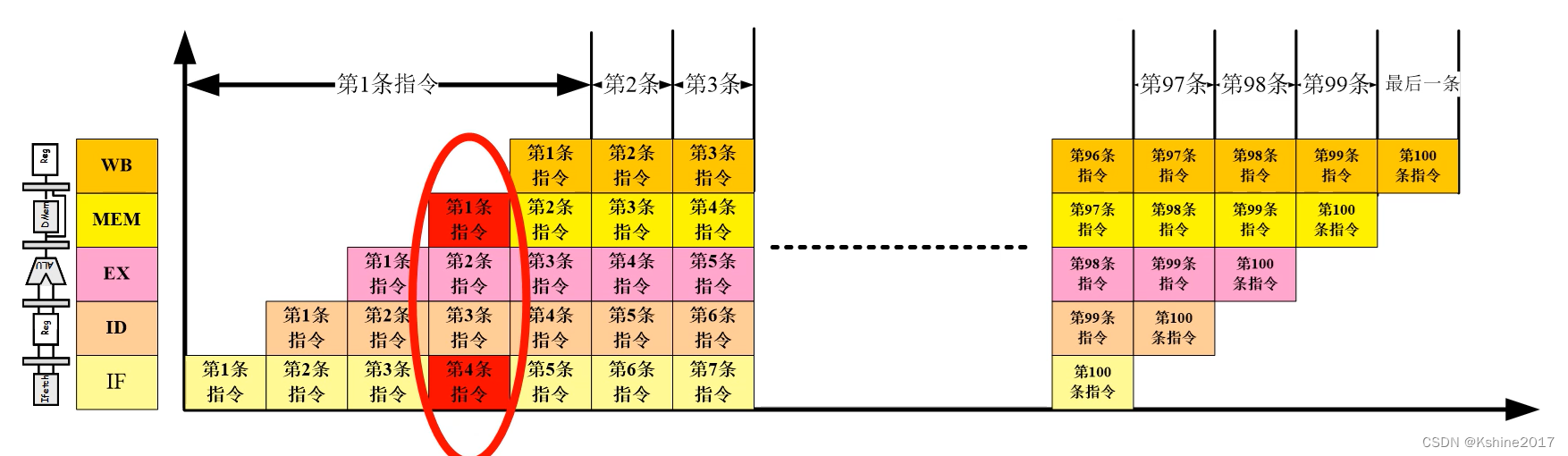

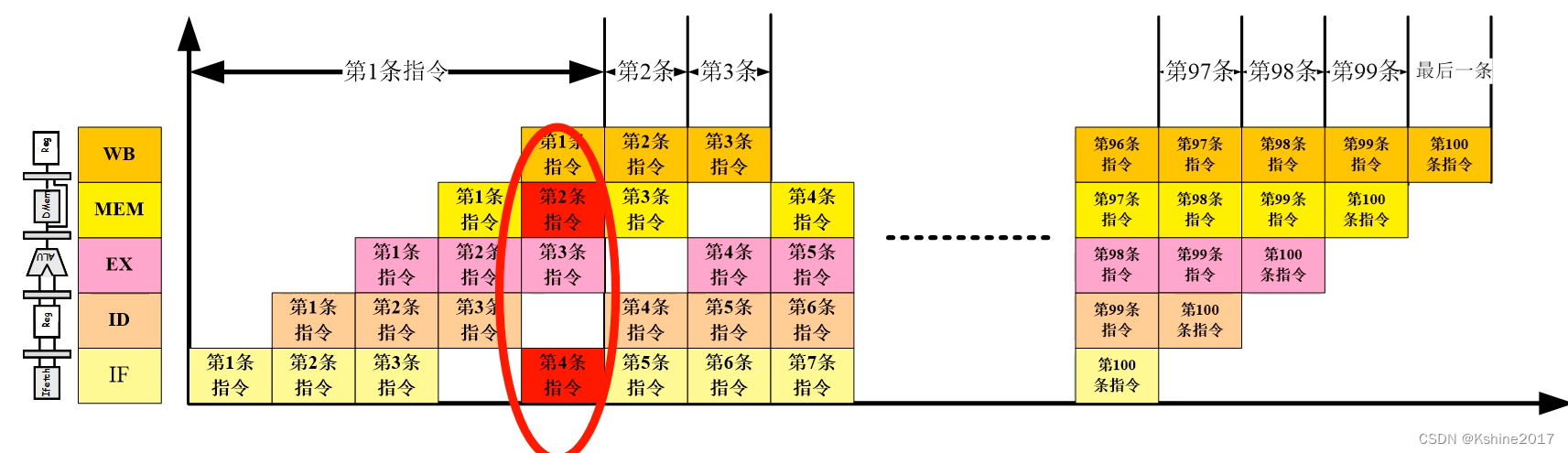

- 当流水线的两个环节都要访问内存时,会出现竞争。如下图所示,当第一个指令被传送到第四个环节时,出现第一个环节和第四个环节争抢总线的情况。

- 解决方式是,将指令向后移动,且必须移动到第四环节和第一环节不同时的位置。这种方式效率低。

- 另一种解决方式,另一种结构,哈佛结构。增加一条总线,数据和指令分开存放,避免冲突。

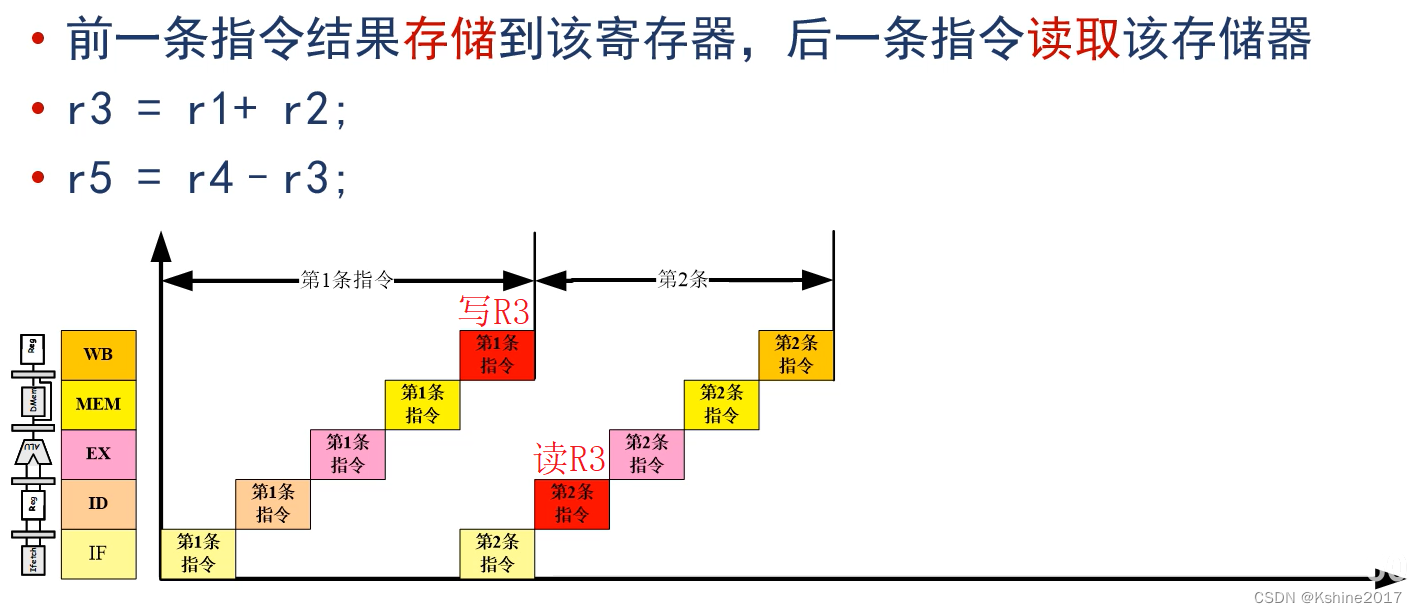

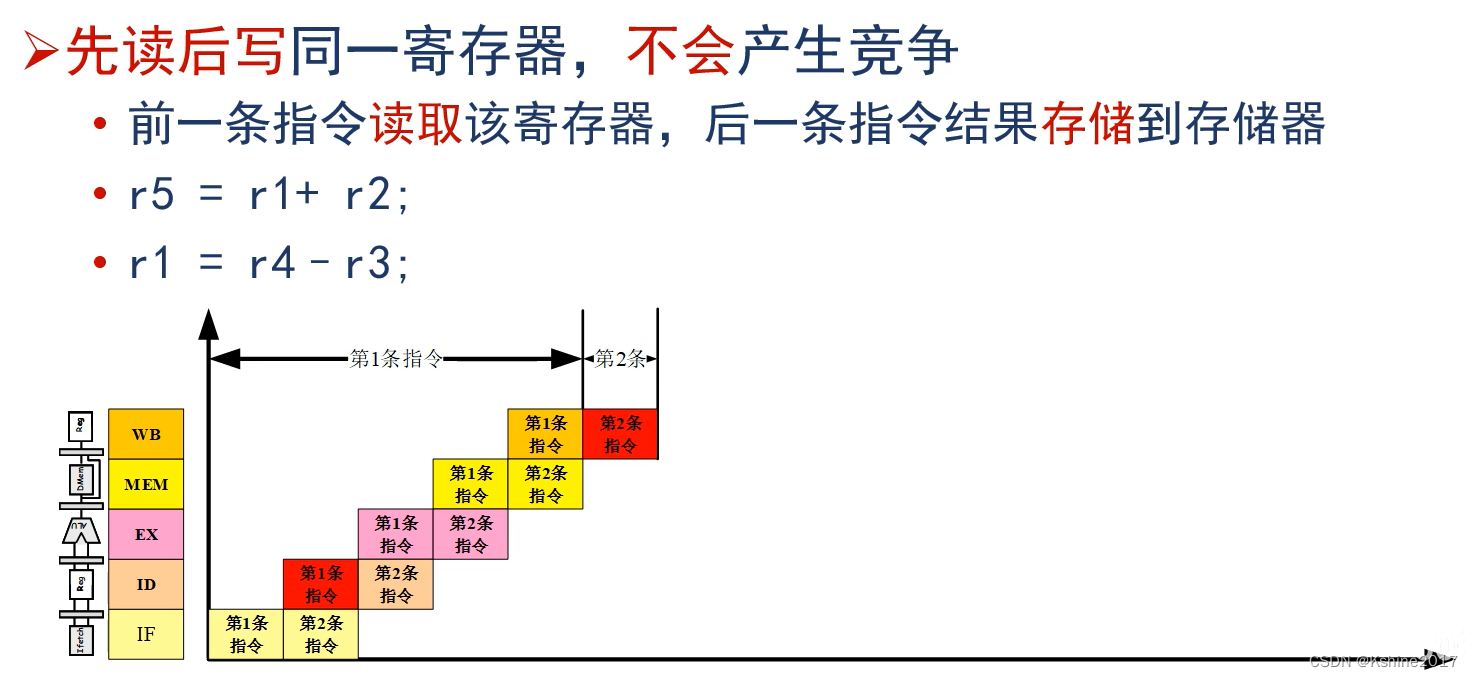

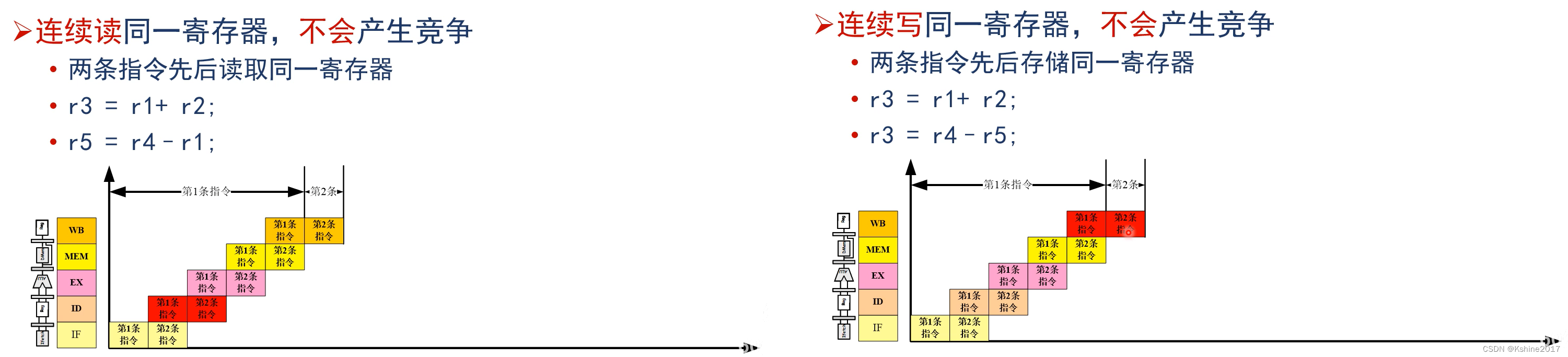

(2) 数据竞争,当前面指令结果无法及时输出。

-

靠编译器和编程方式来解决。

-

先写后读同一个寄存器,会产生竞争。如果采用后移等待的方式,效率会很低。

-

改成先读后写同一寄存器,不会产生竞争。

-

连续读或者连续写同一个寄存器,不会产生竞争。

-

消除数据竞争,尽量避免操作同一个寄存器;前移不会产生竞争的指令(中间插入其他的指令)。

-

编译器的选择:

流水线的时钟正确,

流水线的数据结果正确

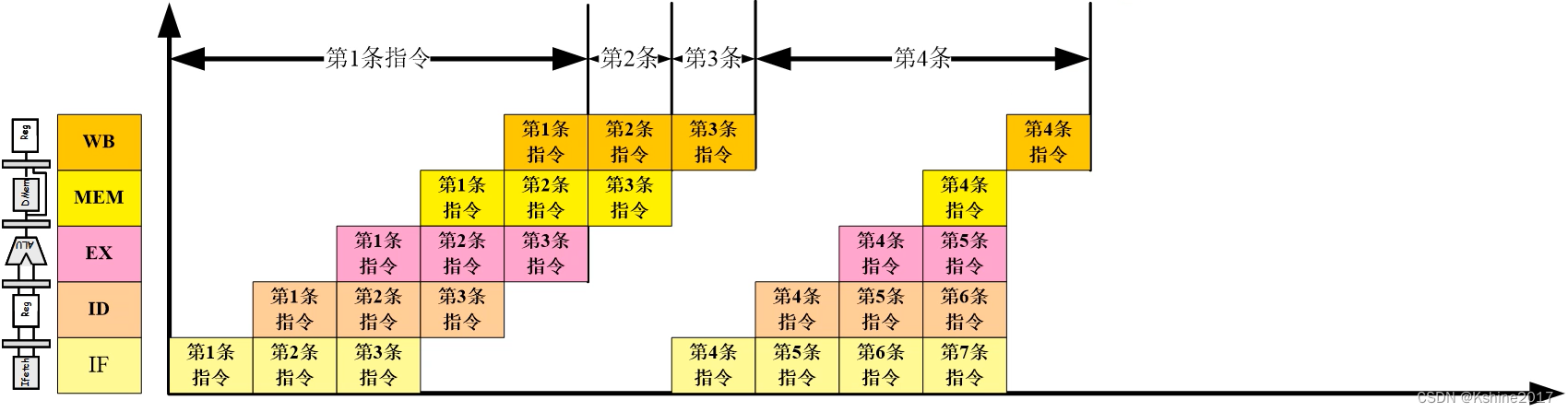

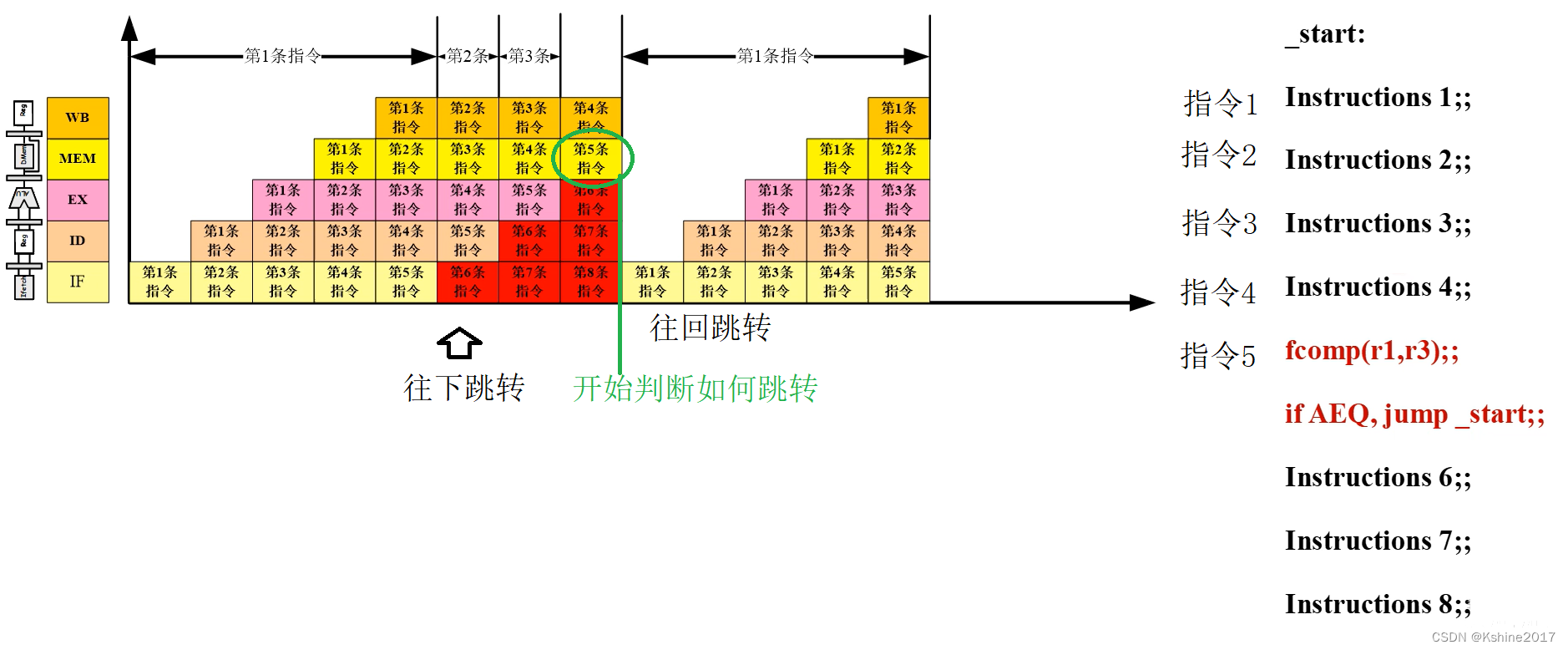

(3)控制竞争,跳转等改变PC值指令预读取与实际不符。

- 指令5用来判断跳转方向,一种是继续执行指令6,一种是跳回指令1。

- 如果出现跳回指令1的情况,流水线下其他678指令已经被载入的部分需要被清除,这样中间就会出现空档,流水线断开了。

- 方法一:分支预测,加载执行概率大的指令。

- 方法二:跳转指令前移。如下图所示,除了指令1和指令6外,234是一定需要被执行的。

2.3 使得CPI进一步下降

视频连接《DSP体系结构》

- 已知,流水线使得CPI=12或24 降到 CPI=1。本节讲述如何使得CPI<1。

- 传统流水线CPI = 1。

- 一个时钟内完成多条指令CPI<1。

2.3.1 超流水线

- CPI=1,主频提升。

- 细化流水,提高主频,空间换时间。

- Pentium4 奔腾4处理器上,应用20级流水线。

- 《百度百科》超流水处理器是相对于基准处理器而言的,一般cpu的流水线是基本的指令预取,译码,执行和写回结果四级。超流水线(superpiplined)是指某型CPU内部的流水线超过通常的5~6步以上,例如Pentium pro的流水线就长达14步。将流水线设计的步(级)数越多,其完成一条指令的速度越快,因此才能适应工作主频更高的CPU。

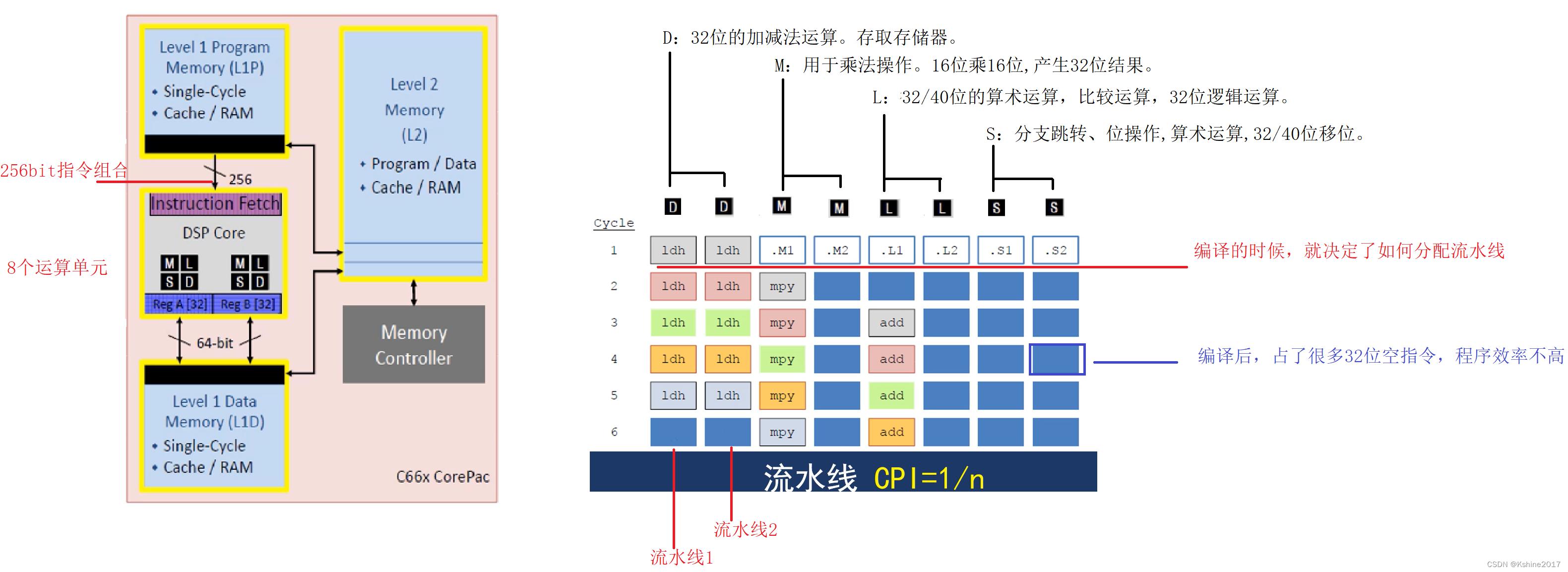

2.3.2 超长指令字(VLIW,very long instruction word)

- 一个时钟内完成多条指令CPI<1

- 一个非常长的指令组合,8x32bit = 256bits。多个流水线并在一起。

- TI公司的C6000系列之后开始使用VLIW技术。

- 程序编译时,根据并行性,组合为多操作超长指令字。会有很多的32位空指令,程序编译后,比较大,程序存储效率不高。

- VLIW每段对应不同的操作单元。D,D,M,M,L,L,S,S。

(1)每个时钟周期启动一条VLIW指令。

(2)每段控制一个操作单元。

(3)编译,编程时,解决竞争问题,控制硬件较简单。

2.3.3 超标量(super scalar)

- 与VLIW结构类似。

- 执行时,根据资源,数据竞争,决定个单元是否执行。

- 在超长指令集基础上程序的存储效率提升。

2.4 DSP软件优化技术

- 软件优化的实质:如何高效使用DSP中的硬件资源。

- 需要我们了解硬件有哪些硬件资源。

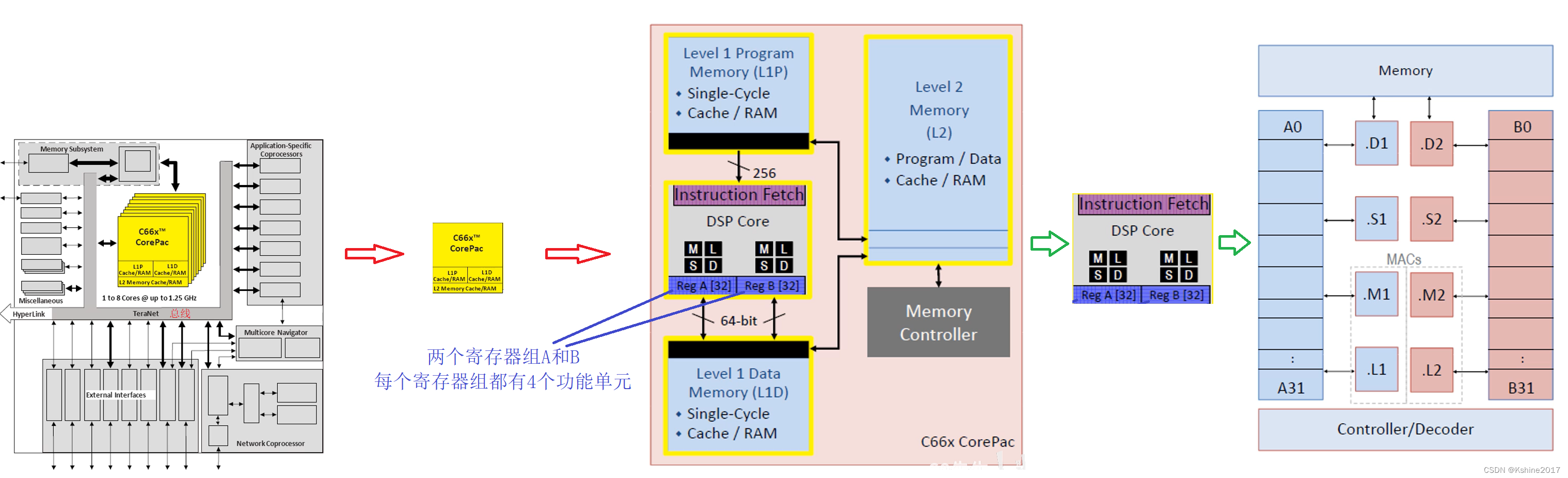

2.4.1 了解DSP的硬件资源

简述

- 以TI公司的TMS320C6678为例。

- L1存储器(L1P程序,L1D数据),L2存储器。

功能单元

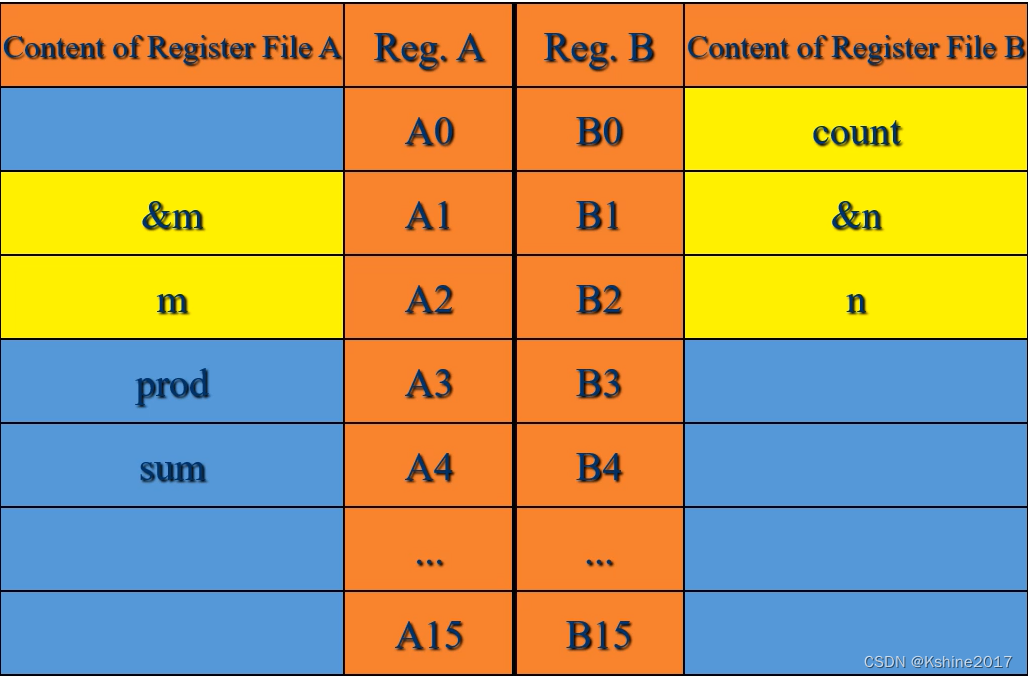

- 有两个寄存器组A和B,每个寄存器组有4个功能单元MLSD。

(1)M,multiplier乘法器。

(2)L,ALU逻辑单元。

(3)S,Data数据单元。

(4)D,Control控制和跳转单元。

交换路径

A侧和B侧交换数据。

内部总线

指令流水线

三条指令,没有流水线时,串行执行,需要9个时钟周期。采用流水线,只需要5个时钟周期。

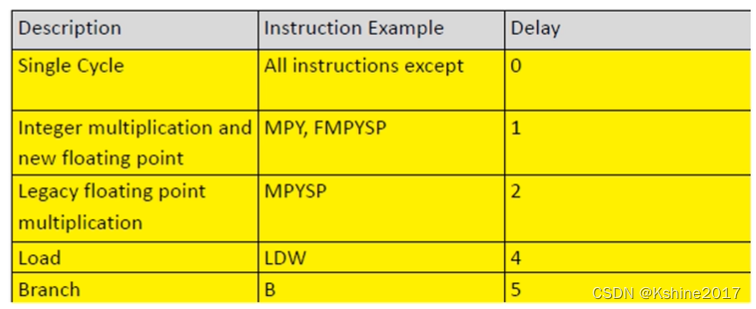

指令延迟

- 大部分的指令立刻可以得到结果。

- 乘法,延迟1拍。

- 浮点乘法,延迟2拍。

- 数据加载,需要先给一个地址,存储器才返回一个数据,需要延迟4拍。

- 跳转,需要清除之前已经预存的指令,需要延迟5拍。

2.4.2 DSP软件优化

- 软件优化的目的:运行速度和代码尺寸。

- 优化编程的要求:熟悉处理器架构,熟悉编程语言(C,汇编,线性汇编)。

- 了解代码生成工具(编译器,汇编器,链接器)

- C6X优化C编译器,使用ANSI C源代码,可以达到手工优化的80%。需要了解各种优化等级。

汇编优化的手段

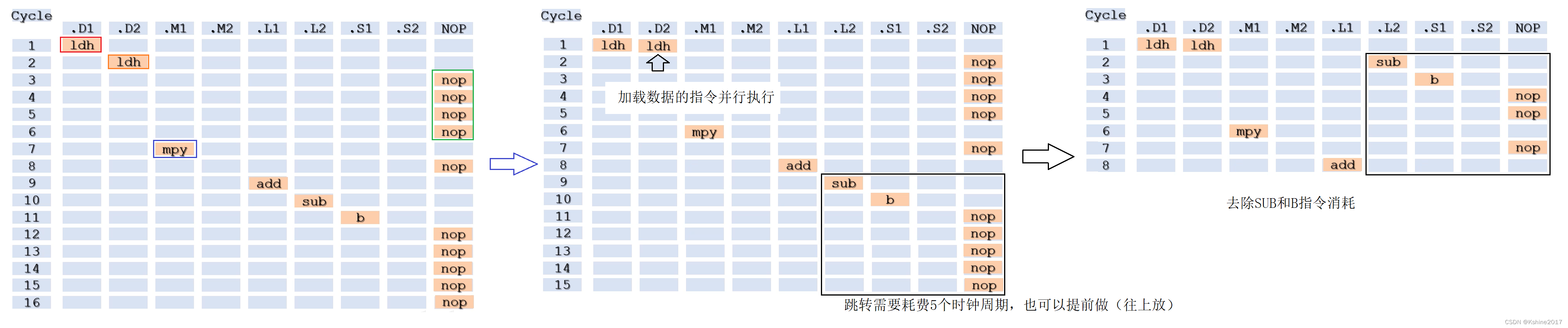

(1)指令并行。

(2)填充NOP指令。

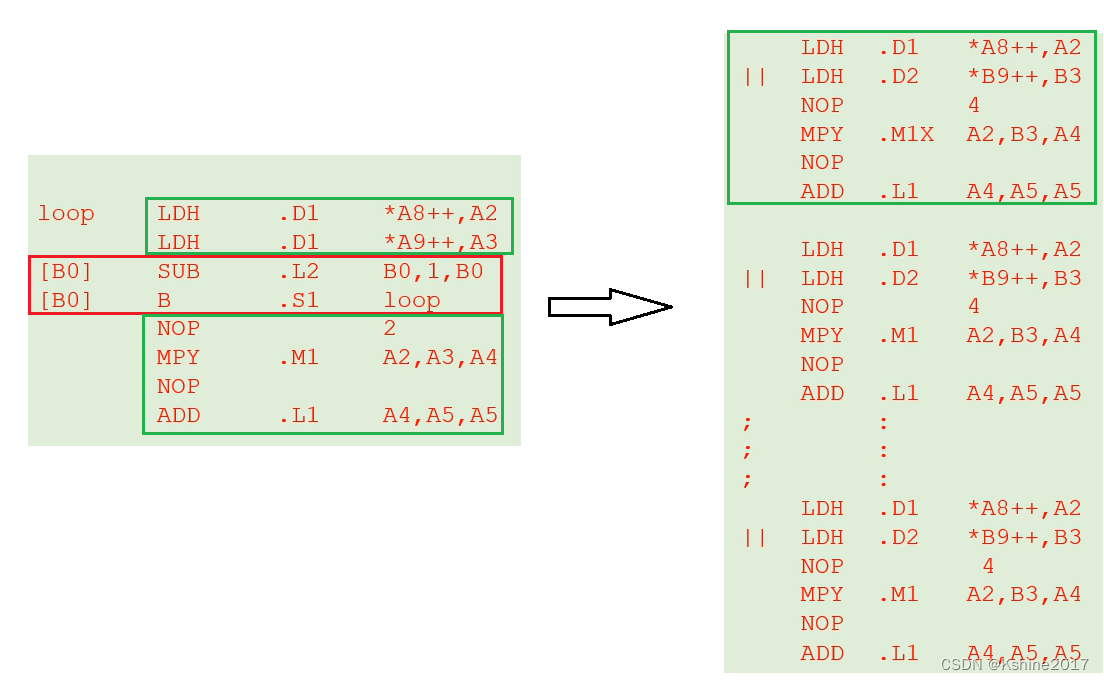

(3)循环展开。(消除sub,b指令开销)。

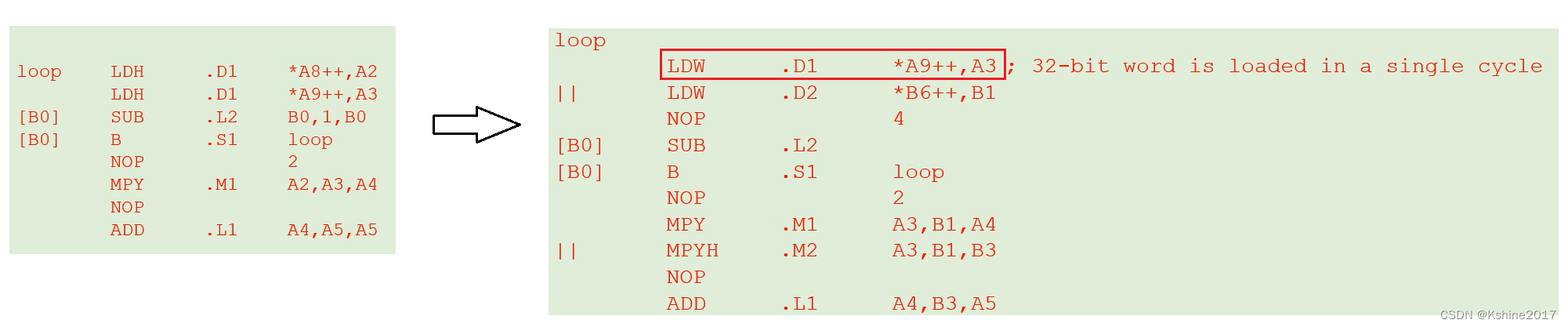

(4)字或者双字访问。

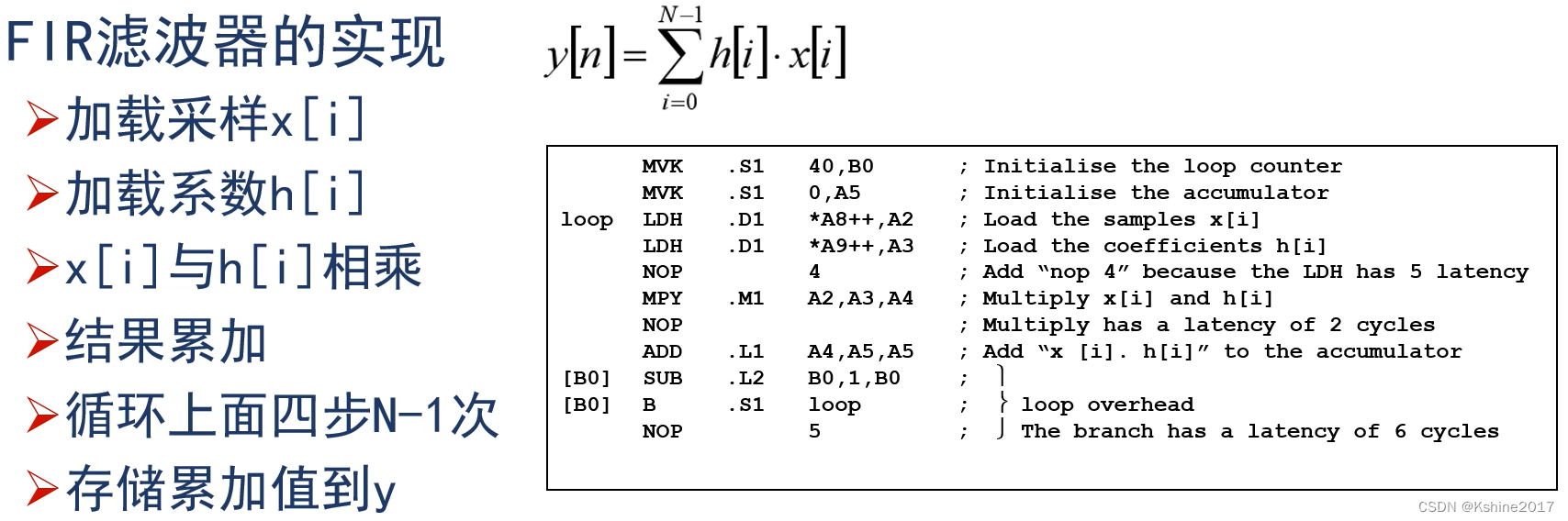

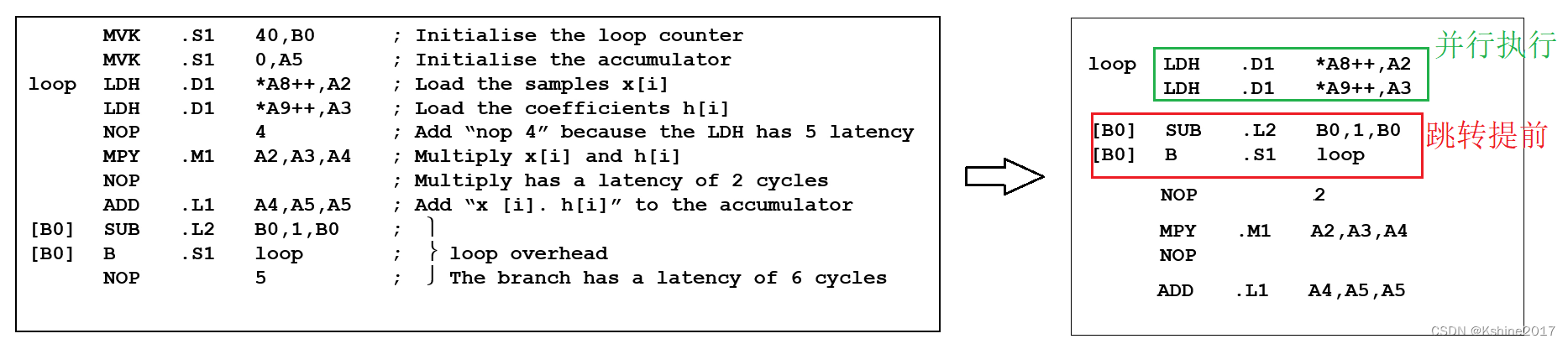

2.4.3 参考优化案例

- 加载数据的指令,可以并行执行。

- 消除sub+b跳转的时间等待。

- 循环展开,消除跳转指令的开销。

- 使用字或者双字访问

2.4.4 软件流水操作

B站视频《DSP软件优化》

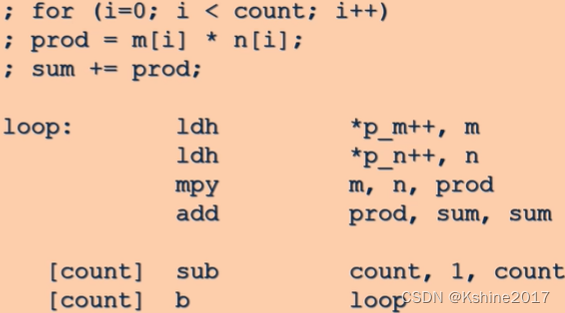

1. C语言实现算法

2. C6x的线性汇编

- 无延迟Nop

- 无指令并行

- 无需考虑功能单元和寄存器

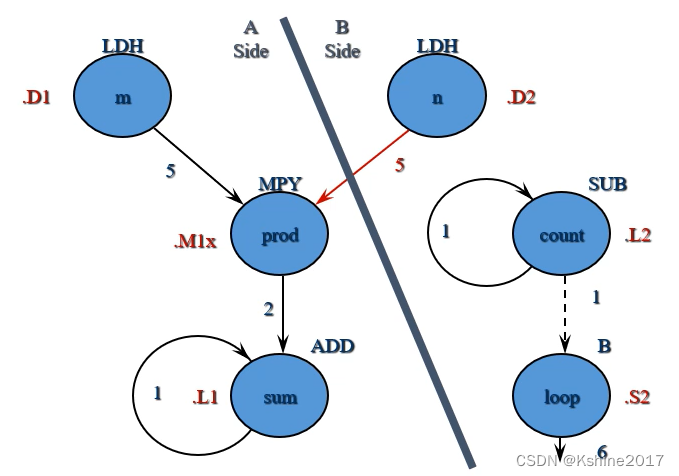

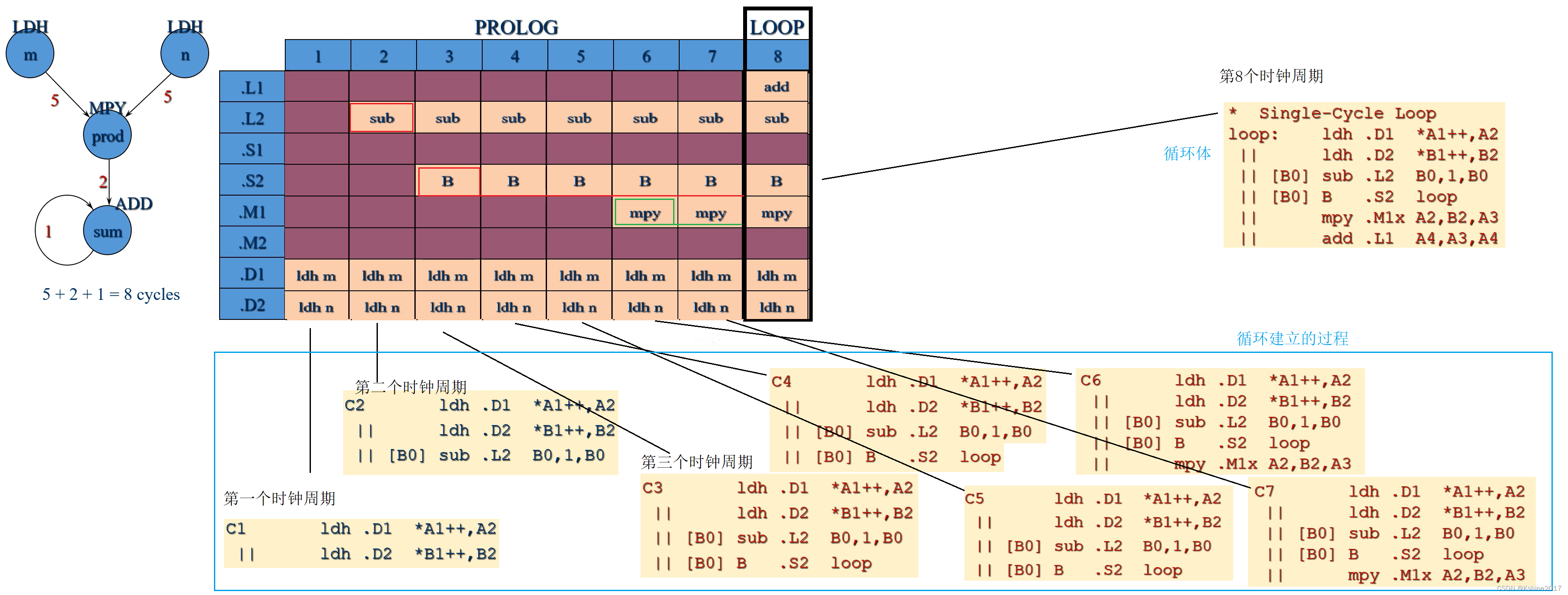

3. 设计关系图

- 得到代码的过程中,依存关系,数据路径,指导我们分配资源。

- 绘制算法节点和路径

- 写出指令周期数消耗

- 分配功能单元到节点

- 将节点分成A,B两侧所有功能单元

4. 分配寄存器

5. 创建进程表

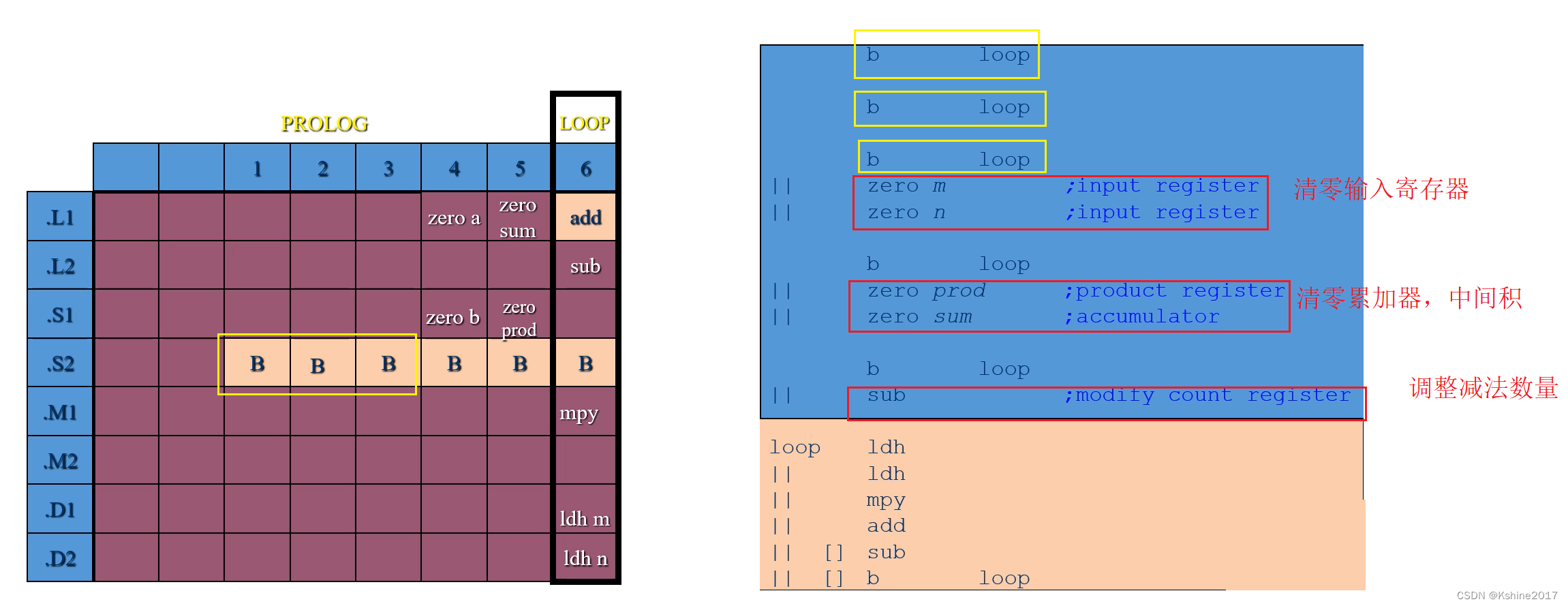

- 前7个时钟周期,处于建立循环的过程。

- 第8个时钟周期开始,是循环体。

- 图中没有给出循环结束后的,循环收尾处理的过程。

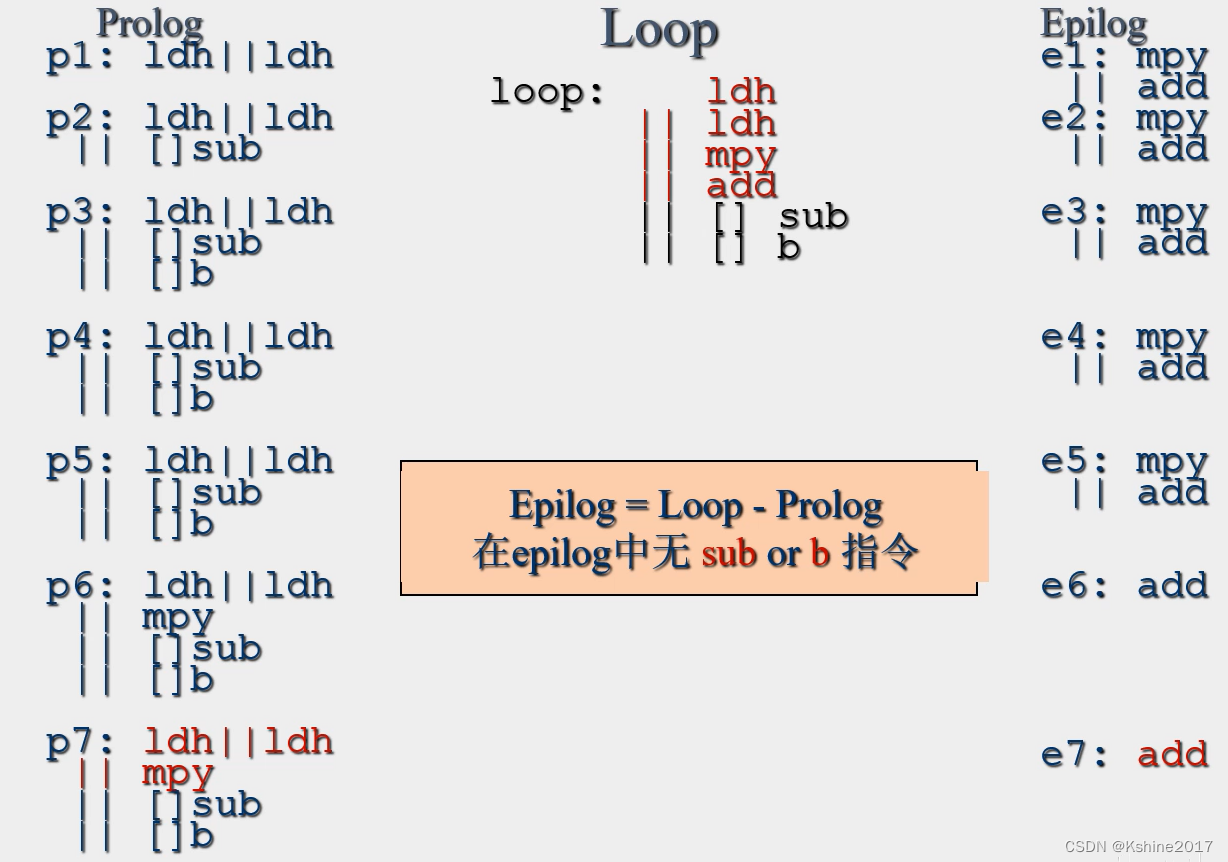

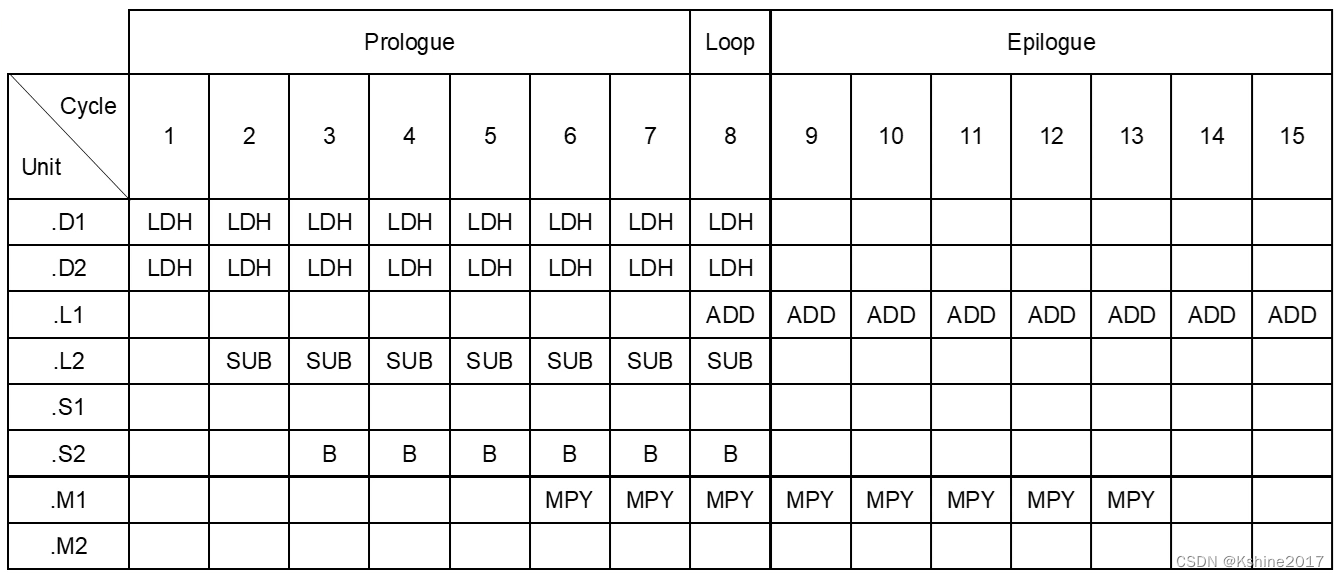

6. 转换C6x代码

-

Prolog,循环建立

-

Loop,循环

-

Epilog,循环收尾,已知循环体包括加载两个数据,乘法,加法。循环收尾和循环建立对应且互补。

-

额外的load

-

完整的进程表,包括循环收尾,如下图。

-

Loop Only,在循环过程中,把收尾工作实现。

去除除跳转指令的所有指令。

清零输入寄存器,累加器和中间积。

调整减法数量。

2.4.5 C代码优化

-

Intrinsics内联技术。

(1)直接阈C6000汇编指令相对应的特殊内联函数,没有函数调用开支。

(2)使用C的变量名(不是寄存器),与C环境兼容。

(3)不增加C的编程工作量。

(4)代码效率与汇编相同。 -

C代码:(代码效率低)

y=a*b;

- 使用Intrinsics的C代码:

y = _mpy(a,b);

- 嵌入汇编:(容易破坏C环境)

asm("MPY A0,A1,A2");

- 汇编代码:(编程工作量大)

MPY A0,A1,A2 ;a,b,y