Verilog数字系统设计六

时序逻辑实验2

前言

随着人工智能的不断发展,机器学习这门技术也越来越重要,很多人都开启了学习机器学习,本文就介绍了机器学习的基础内容。提示:以下是本篇文章正文内容,编程实现方式可控的移位寄存器,移位方式共有四种:a、自循环左移;b、带进位位的循环左移;c、自循环右移;d、带借位位的循环右移。寄存器异步复位。

一、可控的移位寄存器是什么?

示例:pandas 是基于NumPy 的一种工具,该工具是为了解决数据分析任务而创建的。

二、编程

1.要求:

实现方式可控的移位寄存器,移位方式共有四种:a、自循环左移;b、带进位位的循环左移;c、自循环右移;d、带借位位的循环右移。寄存器异步复位。

2.设计思路:

①方式可控:select(两位二进制),四种方式,0x00:自循环右移;0x01:带借位位的循环右移;0x02:自循环左移;0x03:带进位位的循环左移。

②异步复位:时钟或者置位信号到来就变化。

3.实现代码:

always代码如下:

module controllableShiftRegister(select,data,clock,load,rest,result);

input [7:0] data;

input [1:0] select;

input clock,load,rest;

output [7:0] result;

reg CF,temp;

reg [7:0] result;

always @(select,clock,load,rest,data)

begin

if(rest)

begin

result = 0;

CF = 1;

end

else if(load)

begin

result = data;

CF = 1;

end

else

begin

case (select)

2'b00: result = {result[0],result[7:1]};//right

2'b01://right_Borrow

begin

temp=result[0];

result={CF,result[7:1]};

CF=temp;

end

2'b10: result = {result[6:0],result[7]};//left

2'b11://left_carry

begin

temp=result[7];

result = {result[6:0],CF};

CF=temp;

end

default:result =8'bx;

endcase

end

end

endmodule

测试代码如下:

module controllableShiftRegister_tb;

reg [7:0] data_t;

reg clock_t,rest_t,load_t;

reg [1:0]select_t;

wire [7:0]result_t;

controllableShiftRegister mycontrollableShiftRegister(

.data(data_t),

.clock(clock_t),

.rest(rest_t),

.load(load_t),

.select(select_t),

.result(result_t)

);

initial

begin

data_t [7:0] = 0;

clock_t = 0;

rest_t = 1;

load_t =0;

select_t=2'b0;

#5 rest_t = 0;

#20 load_t=1;

#5 load_t=0;

end

always #20 data_t [7:0]={$random}%256;

always #200 select_t=select_t+1;

always #20 clock_t = ~clock_t;

endmodule

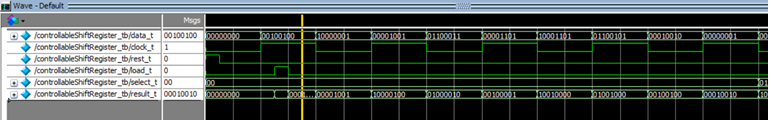

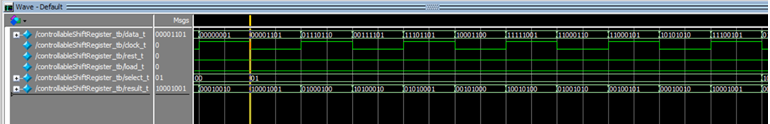

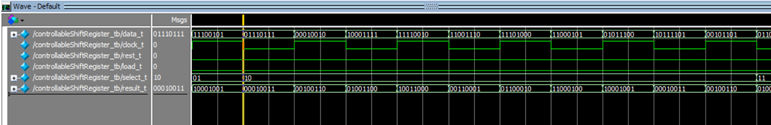

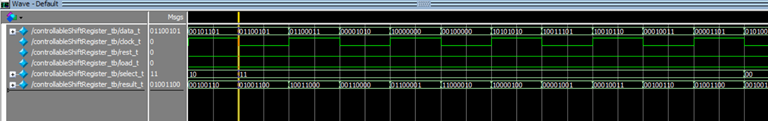

4.仿真测试:

①当select=0时,自循环右移;

②当select=1时,带借位位的循环右移;

③当select=2时,自循环左移;

④当select=3时,带进位位的循环左移。

总结

提示:

以上就是今天要分享的内容,本文仅仅简单介绍了Verilog实现方式可控的移位寄存器,移位方式共有四种:a、自循环左移;b、带进位位的循环左移;c、自循环右移;d、带借位位的循环右移。寄存器异步复位功能。