前言

首先介绍滤波原理,再附上verilog实现思路

一、滤波原理

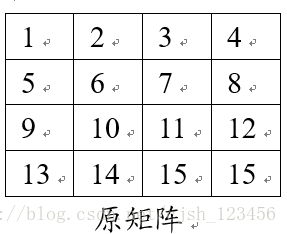

滤波的原理网上介绍很多,简单的滤波有很多,中值滤波,均值滤波,极值滤波,原理差不多,本次使用的滤波器是3×3,同时图像边缘填0。

1、均值滤波,是图像处理中最常用的手段。值滤波是用每个像素和它周围像素计算出来的平均值替换自己。

2、中值滤波也是消除图像噪声最常见的手段之一,特别是消除椒盐噪声,中值滤波的效果要比均值滤波更好。中值滤波是跟均值滤波唯一不同是,不是用均值来替换中心每个像素,而是将周围像素和中心像素排序以后,取中值。

3、最大最小值滤波是一种比较保守的图像处理手段,与中值滤波类似,首先要排序周围像素和中心像素值,然后将中心像素值与最小和最大像素值比较,如果比最小值小,则替换中心像素为最小值,如果中心像素比最大值大,则替换中心像素为最大值。

二、FPGA上Verilog实现步骤

1.图像周围填0

在对图像应用滤波器进行过滤时,边界问题是一个需要处理的问题。对图像的边界做扩展,在扩展边界中填充0,对于边长为2k+1的方形滤波器,扩展的边界大小为k,若原来的图像为[m, n],则扩展后图像变为[m+2k, n+2k]。

举例:即将800×480的图像首先扩展成802×482

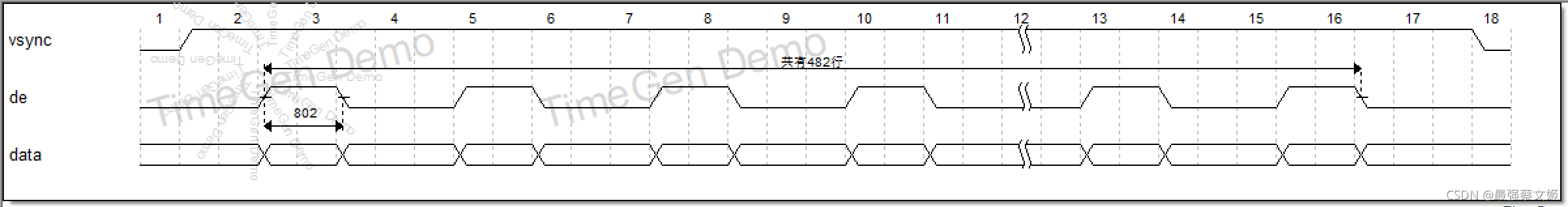

将此前帧有效vsync信号中有数据有效de信号进行扩展。原有的de有480行,800个脉宽,扩展成482行,800个脉宽。

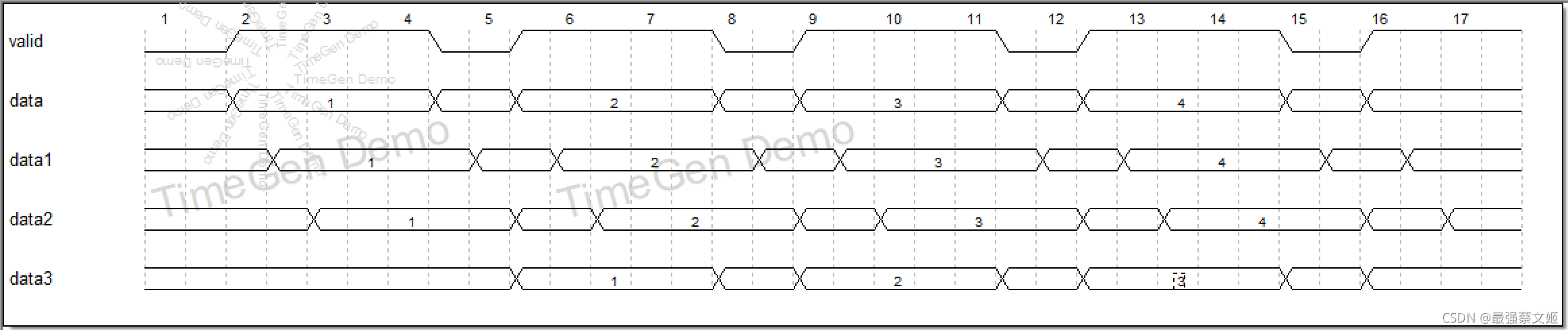

2.数据延迟

将对应的数据data进行延迟,data1相对于data延一拍,data2相对于data延两拍,data3相对于data延迟一行,……,data8相对于data延迟两行。

3.数据处理

中值滤波:

第一步: 分别求出 3 行中同一行的最大值、 最小值、 中间值

设 max_h1 为第一行的最大值, min_h1 为第一行的最小值, mid_h1 为第一

行的中间值。

同理有 max_h2, mid_h2, min_h2, max_h3, mid_h3, min_h3。

第二步: 3 行的最大值、 最小值、 中间值进行比较

max_h1, m2ax_h2, max_h3 这 3 个值比较, 得到这 3 个值的最小值 min_max。

mid_h1, mid_h2, mid_h3 这 3 个值比较, 得到这 3 个值的中间值 mid_mid。

min_h1, min_h2, min_h3 这 3 个值比较, 得到这 3 个值的最大值 max_min。

第三步: 得到 3x3 矩阵的中间值

将第二步得到的 min_max, mid_mid, max_min 进行比较, 得到的中间值,

即该 3x3 矩阵的中间值。

极值滤波:

同理:

第一步: 分别求出 3 行中同一行的最大值、 最小值、 中间值

设 max_h1 为第一行的最大值, min_h1 为第一行的最小值, mid_h1 为第一

行的中间值。

同理有 max_h2, mid_h2, min_h2, max_h3, mid_h3, min_h3。

第二步: 3 行的最大值、 最大值、 最大值进行比较max_h1, m2ax_h2, max_h3 这 3 个值比较, 得到这 3 个值的最大值 max_zong。

均值滤波:

同理:

将9组数据进行求和再求平均。

总结

本章将fpga实现各类滤波进行思路整理