GPU��cuda������

���ѧϰ������ͼ�����ݵĴ����ͼ���,����������CPU�����Ҫ����,���������ͼ�����ͼ����ٶȵ�Ҫ�� �Կ�GPU��������CPU����������ġ� GPU�ر��ó�����ͼ������,CUDA (�����ͳһ�豸��ϵ�ṹ)���Կ�������CUDA��NVIDIA�Ƴ���ͨ�ò��м�����ϵ�ṹ,GPU����, ����CUDAָ���ϵ�ṹ(ISA )��GPU�ڲ��IJ��м�������,ͨ����װCUDA���Լ���GPU������ʹ�����

���������

https://www.zhangshilong.cn/work/35703.html

https://mp.weixin.qq.com/s/7lSuTnoi3V-8-BMP8m53tg

Matrix Multiplication CUDA����https://ecatue.gitlab.io/gpu2018/pages/Cookbook/matrix_multiplication_cuda.html

https://mp.weixin.qq.com/s/TaewNgRtValtFEPQafYs-Q

ʲô���Կ�?

�Կ�(Video card��Graphics card )��ȫ��ʾ�ӿڿ�,����ʾ������,�Ǽ���������������,Ҳ������Ҫ�ĸ���֮һ�� �Կ���Ϊ������������Ҫ��ɲ���֮һ,�Ǽ����������ģ�ź�ת�����豸,�е��������ʾͼ�ε����á� �Կ����ӵ�����������,�����Ե������ź�ת��Ϊģ���ź�,��ʾ����ʾ���ϡ� �Կ�������ͼ��������,������CPU���в�������������ٶȡ� ����רҵ����ͼ����Ƶ�����˵,�Կ��Ƿdz���Ҫ�ġ� ���ú;����Կ�оƬ��Ӧ����Ҫ����AMD (���뵼��)��Nvidia ) NVIDIA (NVIDIA )���ҹ�˾�� ���ڵ�top500���������ͼ�μ�����ġ� �ڿ�ѧ������,�Կ�����Ϊ��ʾ������������

ʲô����ʾ�ڴ�?

Ҳ��Ϊ֡����,���ڴ洢��ͼ��оƬ��������ȡ����Ⱦ���ݡ� �ͼ�����ڴ�һ��,ͼ���ڴ������ڴ洢Ҫ������ͼ����Ϣ�IJ�����

�Կ����Կ����������CUDA֮��Ĺ�ϵ

�Կ�: (GPU ),������NVIDIA��GPU�� ��Ϊ���ѧϰ������Ҫ�����ļ��㡣 GPU�IJ��м����������⼸���кܺõ����������ѧϰ����Ҫ�� AMD��GPU������֧��,���Բ����롣 ��������:���û���Կ���������,GPUӲ��������ʶ��,���������ü�����Դ�� ����,��Linux�ϰ�װNVIDIA���������ر��鷳,�ر��ǶԳ�ѧ����˵,����ج�Ρ� ������ֹ�������Կ��������� �̳�������ʾ�� CUDA :���Կ�������NVIDIA�Ƴ���ֻ�������Լ�GPU�IJ��м����ܡ� ֻ�а�װ�����ܲ��ܽ��и��ӵIJ��м��㡣 �������ѧϰ���Ҳ����CUDA������GPU���м���,������һ���⡣ ��һ������cudnn,����������������ļ��ٿ⡣ ΪʲôGPU�ر��ó�����ͼ������?

������Ϊͼ���ϵ��������ص㶼��Ҫ������,�����������ص�Ĵ������̺ͷ��������ơ� GPU������һ�ִ�����˺�ս��,ʹ������ļ��㵥Ԫִ�д����ļ������� GPU����Ӧ����ͼ��������,��Ӧ���ڿ�ѧ���㡢���ܡ���ֵ�������Ӵ�����ݴ���(����Map-Reduce��)�����ڷ�������Ҫ���ģ���м��������

Ӣΰ��GPU�º˵���Hopper H100

2022��3��NVIDIA GTC�����,NVIDIA���ܻ���ȫ��Hopper�ܹ�GPU����H100,��Ӣΰ������Ϊֹ,���ڼ����˹�����(AI)�������ܼ���(HPC)�����ݷ������������ǿGPUоƬ�����оƬ�Լ����ѧ����Grace Hopper������������

Hopper H100����ʷ�������Ĵ��ʷ�Ծ��H100����800�ڸ������,�������Ͽ���NVIDIA�ġ��º˵�������š��º˵����ĺ��ļܹ���ʲô����?

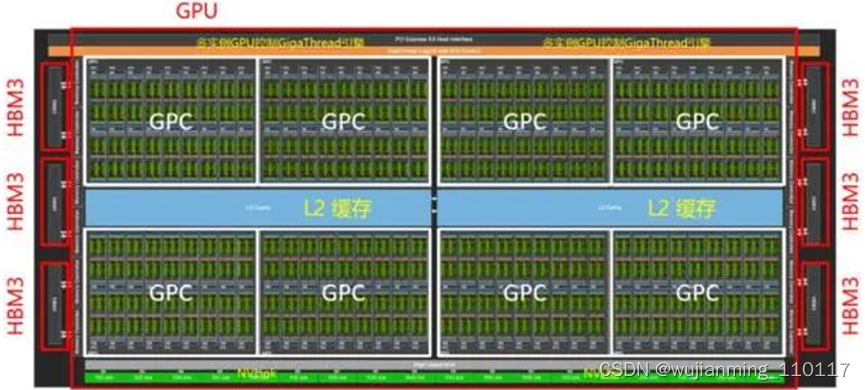

�����ǹ����,NVIDIA Hopper�ܹ���H100оƬ����̨����4nm����(N4��̨����N5���յ��Ż���),�������Ϊ814ƽ������,��A100С14ƽ�����ס���Ȼ���������A100С14ƽ������,��������4nm����,������ܶ�������542��������800�ڡ�

�Ӻ������ͼ����,NVIDIA Hopper�ܹ���ƻ��UltraFusion����,�����ڱ����ϻ��ǵ�����һ�ž�Ƭ,������ƻ��M1 Ultra���ֽ�����оƬ�Ž�����������������Ampere�ܹ����,����Hopper�ܹ�GPU��8��ͼ�δ�����Ⱥ(Graphics Processing Cluster,GPC)��ƴ�ӡ����,��ÿ4��GPC����25MB��L2���档������������HBM3�Դ�,ӵ��5120 Bit��λ��,��������ɴ�80GB��

����Ƭ�ϵ�ÿ��GPC��9������������Ⱥ(Texture Processor Cluster,TPC)���,��PCIe5��ӿڽ���ļ�������,ͨ�����ж�ʵ��GPU(Multi-Instance GPU,MIG)���Ƶ�GigaThread������������GPC��GPCͨ��L2���湲���м�����,GPC������м�����ͨ��NVLink������GPU��ͨ��ÿ��TPC��2����ʽ�ദ����(Streaming Multiprocessor)��ɡ�

Hopper�ܹ���������������Ҫ�仯�����������߳̿鼯Ⱥ��������һ������ʽ�ദ������NVIDIA��Hopper���������µ��߳̿鼯Ⱥ����,��ʵ�ֿ絥Ԫ����Эͬ���㡣H100�е��߳̿鼯Ⱥ����ͬһGPC�ڵĴ�����������,�Խϴ��ģ�;��и��õļ���������

ÿ������128��FP32 CUDA���ġ�4����4����������(Tensor Core)��ÿ����Ԫ��ָ�����ȴ���L1ָ���(L1 Instruction Cache),�ٷַ���L0ָ���(L1 Instruction Cache)����L0���������߳���������(Wrap Scheduler,�߳���)�͵��ȵ�Ԫ(Dispatch Unit)ΪCUDA���ĺ��������ķ����������ͨ��ʹ��4�����⺯����Ԫ(Special Function Unit,SFU)��Ԫ,���г�Խ�����Ͳ�ֵ�������㡣

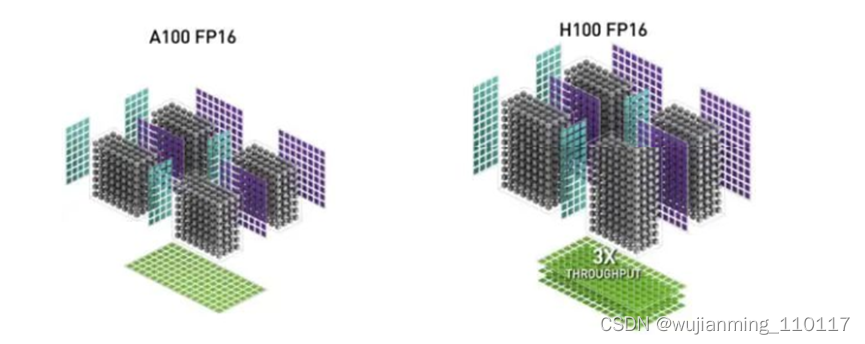

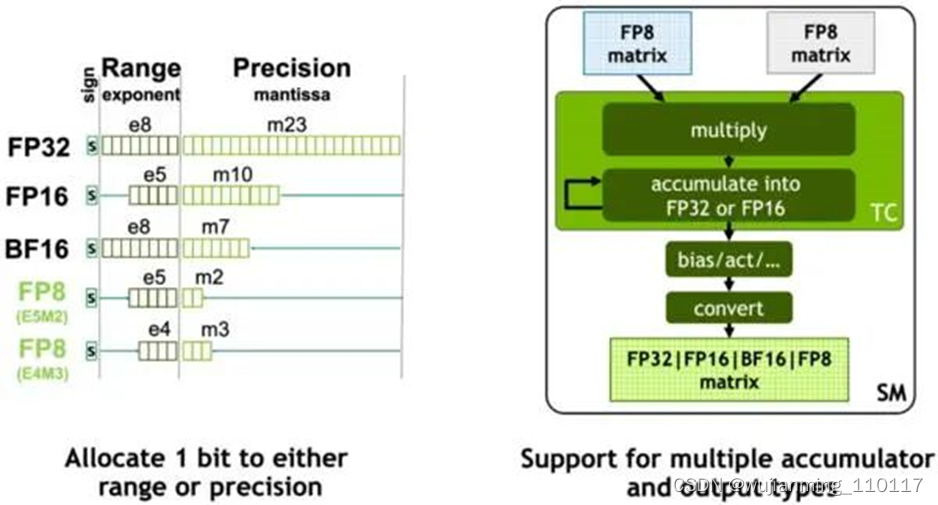

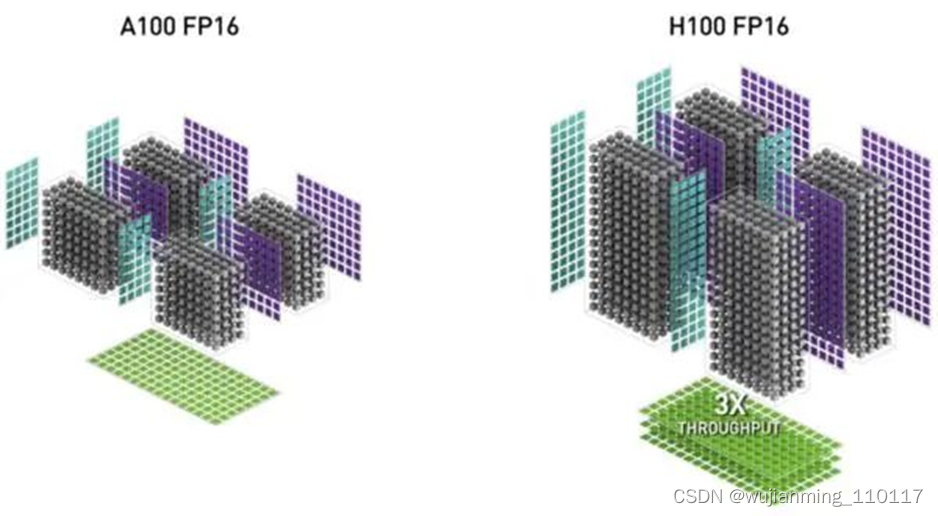

����NVIDIA��Hopper�ܹ���������һ����ʽ�ദ������FP8��������(Tensor Core),��������AIѵ����������FP8��������֧��FP32��FP16�ۼ����Լ�����FP8 ��������(E4M3��E5M2)����FP16��BF16���,FP8�����ݴ洢Ҫ�����,��������������Transformer����ķ�����,���ῴ��ʹ��FP8������Ӧ������Transformer�ļ����ٶȡ�

������GPU��,��������AI���ٵĹؼ�ģ��,Ҳ��Ampere��֮��GPU�ܹ�������GPU����Ҫ�����������������ھ���˷��;����ۼ� (Matrix Multiply-Accumulate,MMA) ��ѧ�����ר�ø����ܼ������,��ΪAI��HPCӦ�ó����ṩͻ���Ե����ܼ��١�

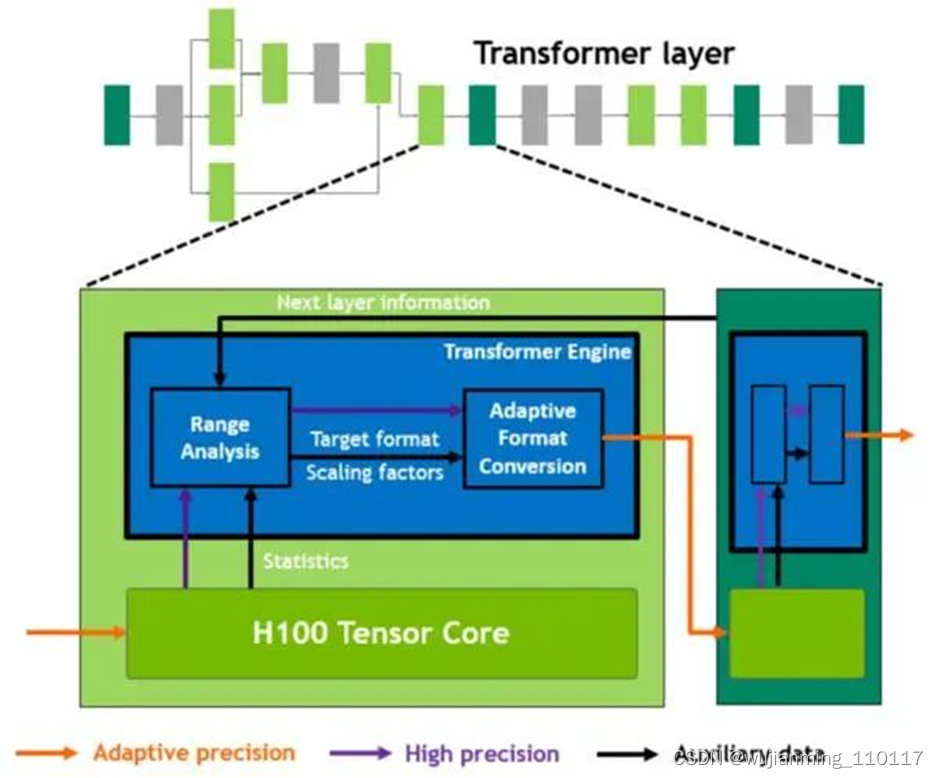

Hopper����������֧��FP8��FP16��BF16��TF32��FP64��INT8 MMA�������͡���һ���������ĵĹؼ���������Transformer���档Transformer������������BERT��GPT-3��NLPģ�͵Ļ���,Խ��Խ���Ӧ���ڼ�����Ӿ��������ʽṹԤ��Ȳ�ͬ����

����һ��A100���,�µ�Transformer������Hopper FP8������������,�ڴ���NLPģ�����ṩ�ߴ�9����AIѵ���ٶȺ�30����AI�����ٶȡ�Ϊ������Transformer�ļ���Ч��,��Transformer����ʹ�û�Ͼ���,�ڼ�����������ܵع������㾫��,��Transformer�����ÿһ��,������һ��������㼰����ľ���,��FP8�����������ʽ�н��ж�̬��ʽת��,��������������ĵ�������

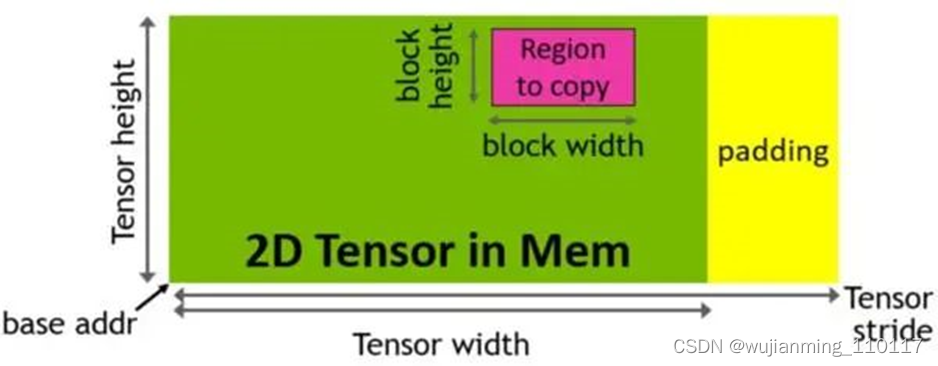

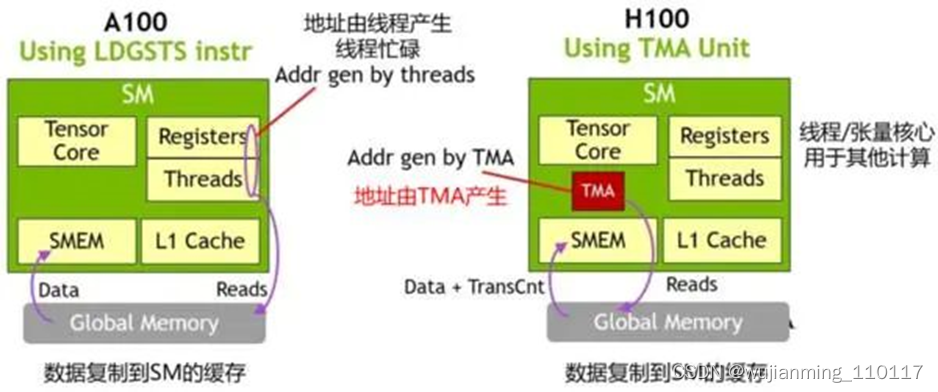

Hopper�ܹ��������������洢������ (Tensor Memory Accelerator,TMA) ,���������������ȫ�ִ洢�����洢�����ݽ���Ч�ʡ��µ�TMAʹ������ά�ȺͿ�����ָ�����ݴ���,�����Ǽİ����ݵ�ֱַ��Ѱַ��TMAͨ��֧�ֲ�ͬ����������(1D-5D����)����ͬ�Ĵ洢����ģʽ����������Ѱַ�����������Ч�ʡ�

TMA�������첽��,����߳̿��Թ�������ͨ��,����������ݴ��䡣TMA�Ĺؼ������ǿ����ڽ������ݸ��Ƶ�ʱ��,�ͷ��̵߳�������ִ����������������,��A100���̱߳��������������е�ִַ���������ݸ��Ʋ���;��Hopper�е�TMA���������ɵ�ַ����(���˼·����DMA������),�ӹ����ݸ�������,���߳�ȥ�������¡�

������Ampere A100�����,����Hopper�ܹ���H100����������ߴ�Լ6�������ܴ�������ĺ���ԭ����NVIDIA����FP8�������ĺ����NLP�����Transformer����,����TMA�������ٵ�Ԫ�����ݸ���ʱ�����ù���

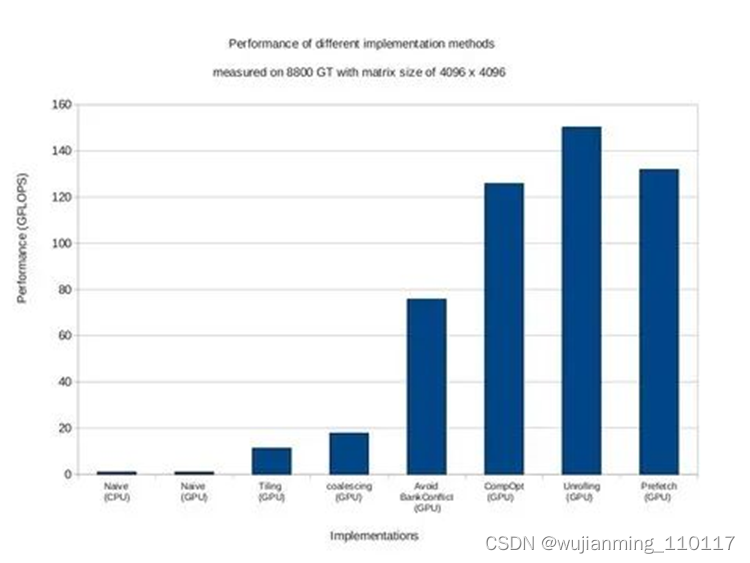

CUDA ���м����Ż������ܽ�

���м���Ϊ������㷨����Ч��,����ͨ���Ծ���˷�(C = A * B)�ĸ���ʵ��˼·�Լ��Ż������ܽ�Ϊ����,��һ��cuda�ļ��������Ż����ԡ�

1 ���ھ���˷�����������

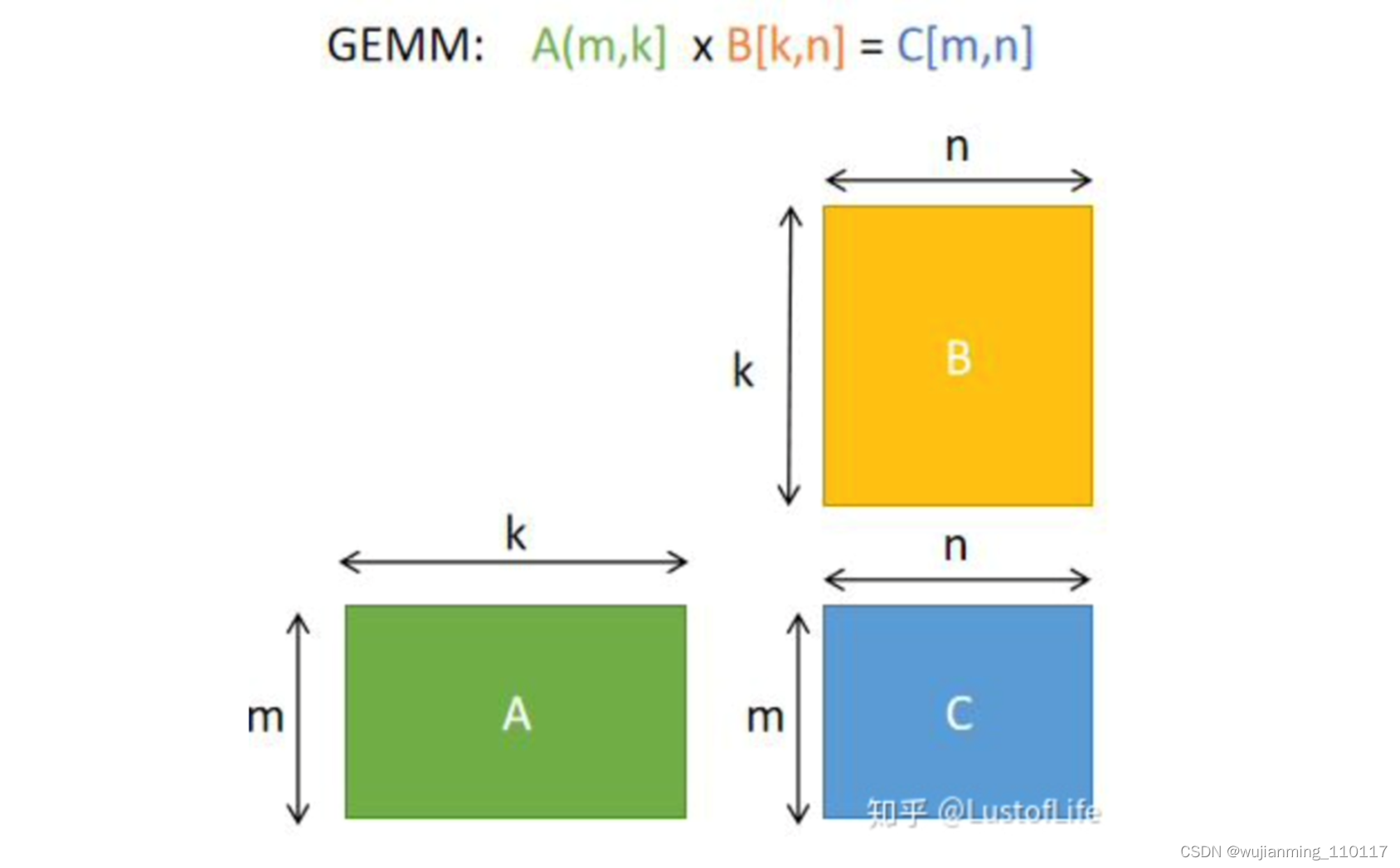

���Ƚ������˷������������˵�ǽ��GEMM(GEneral Matrix to Matrix Multiplication,ͨ�þ���˷�)���⡣��C=��A*B+��C������A��B��C�Ǿ���A��M��K����,B��K��N����,C��M��N����Ϊ�˷���˵��,�����������м������alpha=beta=1��

��ô��θ���Ч�Ľ���GEMM��?

2:�Ż����Եĺ���˼��

? 1.������(cached)

? 2.ʹд���ٶȸ���ָ��ļ����ٶ�

����GEMM����,��ֱ�ӵ��뷨����loop,elements��������

for (int i = 0; i < M; ++i) //---->����A����,��id����i

for (int j = 0; j < N; ++j) //---->����B����,��id����j

for (int k = 0; k < K; ++k) //---->������i,jȷ����ǰ����,���ж�ӦԪ�ص� ��� �� �Ӻ� ,Ԫ��id����k

C[i][j] += A[i][k] * B[k][j]; //---->��������C�ĵ�i,j��Ԫ��

����M=N=K�Ĵ��ͷ���,����˻��е���ѧ������ΪO(N3),�������������ΪO(N2),�Ӷ�����N�ļ���ǿ�ȡ�Ȼ��,�������ۼ���ǿ��(heoretical compute intensity)��Ҫ���ظ�ʹ��ÿ��Ԫ��O(N)������,������ڻ��㷨�����ڻ���(fast on-chip caches)�б���һ����Ĺ�����,��ᵼ������M��N��K����ʱ,CPU��Ҫ���ذ�������,���۵�Ҫ����(�����ϼ�С�����˼��)

PS:һ����˵,���������ڻ�,K��ά����ҪԶ����N,M(����SVM�еĺ˺�������),���Խ����������Kά������ѭ������һ�������ľ�����

һ�����õĹ�ʽ��ͨ������Kά�ϵ�ѭ����Ϊ������ѭ�����û�ѭ��Ƕ�ס�������ʽ�ļ���һ�μ���a�к�B��,���������,����������Ľ���ۼӵ�����C�С��˺�,a�к�B�еĽ��������ʹ�á�

for (int k = 0; k < K; ++k) // K dimension now outer-most loop

for (int i = 0; i < M; ++i)

for (int j = 0; j < N; ++j)

C[i][j] += A[i][k] * B[k][j];

����һ��˼��,��ν�һ�����ټĴ�ռ�Ļ����С?

����������һ��������,��Ҫ�����C������M-by-NԪ�ض��Ǽ����,�Դ洢ÿ���˷��ۼ�ָ��Ľ�����������ѱ�֤�ڴ��е�д���ٶ��ܹ�����CPU�еļ����ٶȡ�

���ȥʹ���ڴ��д���ٶ������˷��ۼ�ָ����ٶ�һ������?

�C ���÷ֿ�(Tile)�IJ���

�ص�����,

���� ,���ǿ���ͨ��������C�Ĺ����ռ�PartitioningΪ��СΪ(Mtile-by-Ntile)��Tile������C�Ĺ����ռ��С(the working set size of C), ��ЩTile�Ĵ�С��Ҫ��洢��(on-chip memory)����Ӧ��

Ȼ��,���ǽ�����������ڻ��IJ���Ӧ�õ�ÿһ��Tile�ϡ���������ѭ��Ƕ��������

for (int m = 0; m < M; m += Mtile) // iterate over M dimension

for (int n = 0; n < N; n += Ntile) // iterate over N dimension

for (int k = 0; k < K; ++k) //----> like above example

for (int i = 0; i < Mtile; ++i) // compute one tile

for (int j = 0; j < Ntile; ++j) {

int row = m + i;

int col = n + j;

C[row][col] += A[row][k] * B[k][col];

}

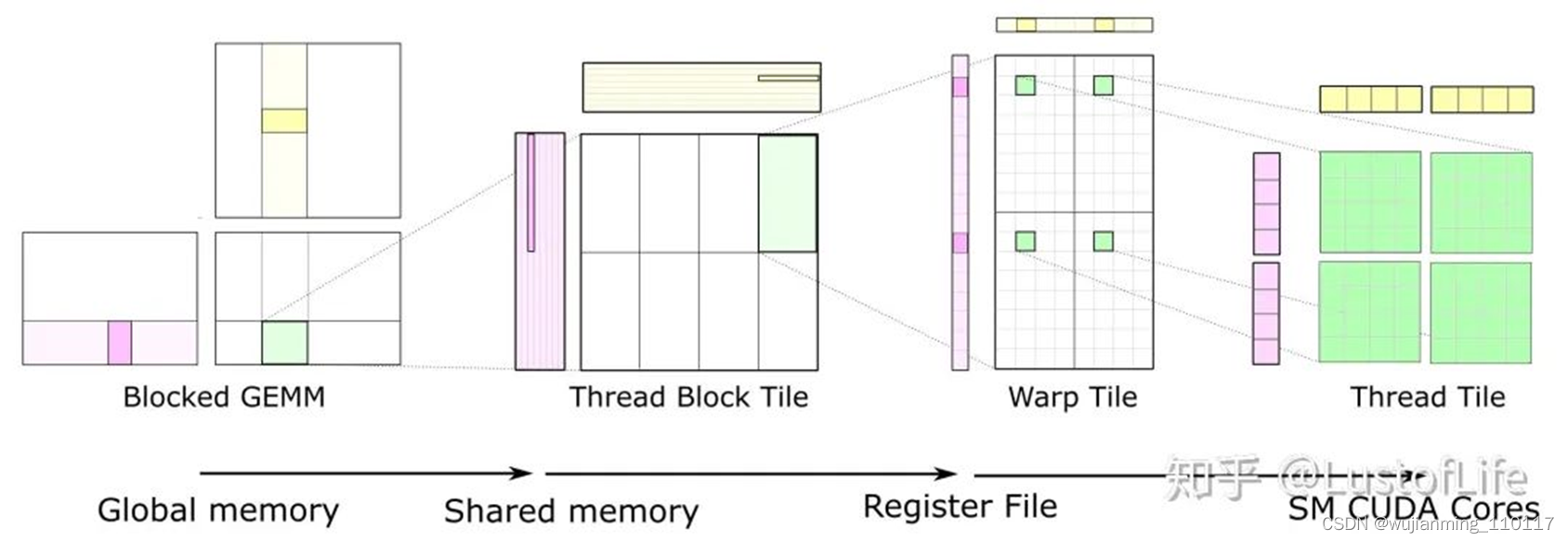

����C�ϵ�ÿһ��Tile,��ֻȡ��һ��A��B�е�Tiles,ʹ��ﵽ*O(N)*�ļ���ǿ�ȡ�ʾ��ͼ����������������(����� global memory / shared memory / register file/ SM cores ��̫����Ļ�,���ǽ���ú��о��о�һ��,�Ժ������Ż�����������а���!)

����GPU��˵,The size of each tile of C may be chosen to match the capacity of the L1 cache or registers of the target processor, and the outer loops of the nest may be trivially parallelized. This is a great improvement !

Here, you can see data movement from global memory to shared memory (matrix to thread block tile), from shared memory to the register file (thread block tile to warp tile), and from the register file to the CUDA cores for computation (warp tile to thread tile).

���������

https://www.zhangshilong.cn/work/35703.html

https://mp.weixin.qq.com/s/7lSuTnoi3V-8-BMP8m53tg

Matrix Multiplication CUDA����https://ecatue.gitlab.io/gpu2018/pages/Cookbook/matrix_multiplication_cuda.html

https://mp.weixin.qq.com/s/TaewNgRtValtFEPQafYs-Q