TSMC台积电各种制程工艺技术

台积电在半导体制造行业的专用 IC 代工领域拥有最广泛的技术和服务。IC Industry Foundation 战略体现了一种集成方法,将工艺技术选项和服务捆绑在一起。

台积电与合作伙伴合作,确保支持这些技术的所有服务代表专用 IC 代工领域的最佳实践。为此,台积电及其生态系统合作伙伴提供最大的经过工艺验证的 IP 和库组合,以及 IC 行业最先进的设计生态系统,即开放式创新平台? (OIP)。

台积电提供最先进、最全面的专用代工工艺技术组合。

台积电的 3nm 技术 (N3) ,5nm 技术 (N5) 的另一个完整节点,并在推出时提供 PPA 和晶体管技术中最先进的代工技术。与 N5 技术相比,N3 技术将提供高达 70% 的逻辑密度增益,相同功率下高达 15% 的速度提升,以及相同速度下高达 30% 的功耗降低。N3技术发展步入正轨,进展良好。N3 技术将为移动和 HPC 应用程序,提供完整的平台支持,预计 2021 年将收到多个客户产品流片。此外,批量生产的目标是 2022 年下半年。

台积电的 5nm (N5) 鳍式场效应晶体管 (FinFET) 技术于 2020 年第二季度成功进入量产,并在 2020 年下半年经历了强劲的增长。

台积电的 N5 技术是台积电第二个可用的 EUV 工艺技术,以帮助客户在智能手机和 HPC 应用中进行创新。作为代工行业最先进、性能、功耗和面积(PPA)最佳的解决方案,N5技术比N7技术提供约20%的速度或约40%的功耗降低。N5 技术进一步扩展了客户产品组合,并增加了目标市场。

此外,台积电计划推出4nm(N4)技术,这是N5技术的增强版。N4 进一步增强了下一波 N5 产品的性能、功率和密度。N4技术开发如期进行,进展良好,预计2022年开始量产。

台积电的7nm翅片场效应晶体管(FinFET)(N7)工艺技术通过在2016年6月以两位数的产量交付256Mb SRAM,为7nm工艺技术的发展设定了行业步伐。2019年,在N7工艺节点批量生产的第二年,客户在N7上录制了110多种新一代产品。此外,7nm FinFET plus(N7+)技术于2019年进入全面生产,并向客户大量交付7nm产品。N7+技术是世界上第一种商用极紫外EUV铸造制造工艺技术。成功证明了TSMC世界领先的EUV体积生产能力,为N6和更先进的技术奠定了坚实的基础。

台积电的6nm FinFET(N6)技术在2019年顺利完成了产品良率验证。得益于EUV光刻技术实现的掩膜层减少和工艺复杂度,N6技术相比N7技术在2019年可以实现更好的良率和更短的生产周期。制造相同的产品。此外,N6 制造工艺的逻辑密度比 N7 工艺高 18%。同时,其设计规则与台积电久经考验的N7技术完全兼容,可重用其完善的设计生态系统。因此,以非常有限的工程资源为客户提供了一个具有快速设计周期的无缝迁移路径,不仅可以从新技术产品中获得产品优势,而且可以显着降低客户的成本。

N6 技术的风险生产于 2020 年第一季度开始,在 2020 年底量产,台积电的 N6 技术为客户提供额外的成本效益优势,同时将 7nm 家族的行业领先功率和性能扩展到广泛的阵列应用程序,包括中高端移动、消费类应用程序、人工智能、网络、5G 基础设施、GPU 和高性能计算。

与其 10 纳米 FinFET 工艺相比,台积电的 7 纳米 FinFET 具有 1.6 倍的逻辑密度、约 20% 的速度提升和约 40% 的功耗降低。台积电通过推出两个独立的 7nm FinFET 轨道创造了另一项行业记录:一个针对移动应用程序进行了优化,另一个针对高性能计算应用程序进行了优化。

TSMC 的 10 纳米鳍式场效应晶体管 (FinFET) 工艺提供了最具竞争力的性能、功率、面积和交付参数组合。公司于 2016 年第一季度开始接受客户为其 10 纳米 FinFET 工艺流片,并于 2017 年初开始大批量出货,成功支持主要客户的新移动产品发布。

凭借更激进的几何收缩,该工艺提供了比其前身 16nm 工艺高 2 倍的逻辑密度,以及约 15% 的速度和约 35% 的功耗降低。该工艺继续利用革命性的 FinFET 优势来帮助客户实现最佳密度和功率效率。

TSMC 的 10nm FinFET 支持各种细分市场,包括应用处理器、蜂窝基带和 ASIC 设计。

2013 年 11 月,台积电成为第一家开始 16 纳米鳍式场效应晶体管 (FinFET) 风险生产的代工厂。此外,台积电成为第一家为其客户生产业界首款 16 纳米 FinFET 全功能网络处理器的代工厂。

继 16 纳米 FinFET 工艺成功后,台积电推出了 16 纳米 FinFET Plus (16FF+) 工艺。16FF+ 于 2015 年 7 月迅速进入批量生产,这得益于其快速的良率提升和性能改进。

同时,16FF+技术于2017年开始为汽车行业的客户应用生产。

台积电还推出了更具成本效益的 16 纳米 FinFET 紧凑型技术 (16FFC),该技术于 2016 年第二季度投入生产。该工艺通过同时结合光学收缩和工艺简化,最大限度地降低了芯片成本。此外,12nm FinFET 紧凑型技术 (12FFC) ,将栅极密度提高到 2017 年投入生产的最大值。

TSMC 的 16/12nm 提供了业界 16/14nm 产品中的最佳性能。与台积电的 20nm SoC 工艺相比,16/12nm 的速度提高了 50%,相同速度下的功耗降低了 60%。下一代高端移动计算、网络通信、消费和汽车电子应用提供卓越的性能和功耗优势。

台积电于2014年成为全球第一家开始20纳米量产的半导体公司,采用其创新的双图形技术,并在同年创造了台积电最快的爬坡节点记录。截至2015年底累计晶圆出货量超过100万片12英寸晶圆。

由于使用节能晶体管和互连以及世界领先的双图案技术,20nm 技术提供了比以前的技术节点更好的密度和功率值。与其 28nm 节点相比,20nm 工艺提供了 15% 更好的性能,并且可以将总功耗降低三分之一。性能驱动型产品和移动计算应用程序迁移的理想选择。

22nm超低功耗(22ULP)技术是基于台积电行业领先的28nm技术开发的,并于2018年第四季度完成了所有制程资质。相比28nm高性能紧凑型(28HPC)技术,22ULP提供了10%的面积减少对于包括图像处理、数字电视、机顶盒、智能手机和消费产品在内的应用,速度提高 30% 以上或功耗降低 30% 以上。

22nm超低泄漏(22ULL)技术开发于2018年第四季度完成并进入风险生产,以支持物联网和可穿戴设备应用。与 40ULP 和 55ULP 解决方案相比,新的 ULL 器件和 ULL SRAM(静态随机存取存储器)可以提供更低的功耗。

台积电于 2011 年成为首家提供全球首个 28 纳米通用工艺技术的代工厂,此后一直在增加更多选择。台积电为客户提供代工厂最全面的28nm工艺组合,使产品性能更高、更节能、更环保。

台积电的 28 纳米制程技术具有高性能和低功耗的优势,再加上与其 28 纳米设计生态系统的无缝集成,可加快上市时间。28nm 制程技术支持广泛的应用,包括中央处理器 (CPU)、图形处理器 (GPU)、高速网络芯片、智能手机、应用处理器 (AP)、平板电脑、家庭娱乐、消费电子、汽车、和物联网。

台积电业界领先的28nm制程技术主要采用High-k Metal Gate (HKMG) 后栅极技术。与先栅极技术相比,后栅极技术提供更多优势,包括更低的漏电流和更好的芯片性能。

台积电于2008年成为首家使用其40nm工艺技术为多个客户量产多种产品的代工厂。40nm工艺集成了193nm浸没式光刻技术和超低k连接材料,以提高芯片性能,同时降低功耗。该工艺还创造了最小 SRAM (0.242μm2 ) 和宏尺寸的行业记录。

40 纳米通用 (GP) 和低功耗 (LP) 工艺的原始栅极密度比 65 纳米技术高 235%。在相同的漏电流水平下,40nm GP 的性能比 65nm 的同类产品高出 40%,在相同的运行速度下功耗仅为其一半。在相同的运行速度下,40nm LP 工艺与 65nm 工艺相比,可将泄漏电流和功耗降低多达 51%。

台积电多样化其 40 纳米制程技术,以满足更广泛的客户需求。新增功能包括 40 纳米增强型 LP 和 40 纳米超低功耗 (ULP) 工艺。与 40nm LP 工艺相比,40nm 增强型 LP 性能提升高达 30%,而 40nm ULP 可减少高达 70% 的漏电流并降低高达 30% 的功耗。

40nm GP 工艺技术针对高性能应用,包括中央处理单元 (CPU)、图形处理器、游戏机、网络、FPGA 和硬盘驱动器。40nm LP 和 40nm 增强型 LP 工艺针对智能手机、数字电视 (DTV)、机顶盒 (Set-Top-Box)、游戏和无线连接应用。40nm ULP工艺适用于物联网和可穿戴应用。

台积电于 2005 年成为第一家开始 65nm 风险生产的代工厂,并于次年通过了产品认证。

台积电的 65 纳米技术是该公司采用铜互连和低 k 电介质的第三代半导体工艺。该技术支持的标准单元栅极密度是台积电 90nm 工艺的两倍。它提供了更好的集成和改进的芯片性能。2005年,台积电还推出了代工厂首个65nm低功耗(LP)工艺,以满足客户的需求。65nm LP 工艺凭借其创新的电源管理技术显着降低了功耗。

继 65nm LP 工艺之后,台积电迅速推出了广泛的工艺组合,其中包括:通用 (GP)、混合信号/射频 (MS/RF)、嵌入式 DRAM 存储器 (eDRAM)、多次可编程非易失性存储器 (MNVM) )、嵌入式闪存 (eFLASH)、高压 (HV)、电源管理 (BCD) 和 MEMS 工艺。65nm 技术支持广泛的应用,例如移动设备、计算机、汽车电子、物联网和智能可穿戴设备。

55nm LP 的推出提供了进一步增强的 PPA 和缩小芯片尺寸。该系列的新增功能是 55 纳米增强型超低功耗 (ULP) 工艺。与 55nm LP 工艺相比,55nm ULP 提供更低的泄漏以延长电池寿命。55ULP 还集成了射频和嵌入式闪存功能,使客户的 SoC 设计具有更小的外形尺寸。

台积电成为第一家使用浸没式光刻技术生产全功能 90 纳米芯片的半导体公司。公司于 2004 年 12 月在 SEMICON Japan 上宣布了这一成就。

台积电创新的浸入式光刻机采用 193nm 光刻水介质扫描仪,而不是传统的 157nm 干式扫描仪,为全球半导体行业设定了新的扫描仪规格。这一发展巩固了台积电的技术领先地位,帮助半导体行业突破摩尔定律所定义的壁垒,推动整个行业朝着更多的工艺技术进步。

台积电推出了半导体行业首个 0.13 微米 (μm) 低 k 铜片上系统 (SoC) 工艺技术。公司坚持打造自己的研发能力,并在拒绝知名IDM(集成设备制造商)的联合开发邀请时做出了有助于取得成功的关键决策。台积电将其研发团队设在公司新竹总部,并领先于 IDM 和其他代工厂成功开发了该技术。这一成就不仅标志着台湾发展先进技术的能力,也成为台湾半导体产业发展的基石。

台积电的0.13μm SoC低k铜技术集成了多个世界一流的SoC CMOS晶体管工艺平台、超小型SRAM存储器(2.43-1.87平方μm)、全球最新的193nm光刻技术、全球首创的八层低k( k≤2.9) 铜线。如今,它在消费电子、计算机、移动计算、汽车电子、物联网和智能可穿戴设备中有着广泛的应用。

台积电于 1998 年提供了世界上第一个 0.18 微米 (μm) 低功率工艺技术。该公司通过每两年推出新的低功率工艺,从 0.13 微米和 90 纳米 (nm) 到20 纳米和 16 纳米技术。

低功耗工艺技术至关重要,极大地加速了移动和智能电子行业的技术发展,而这些行业在十多年的时间里改变了世界和生活方式。低功耗技术驱动着广泛的应用,包括移动电话、无线通信、平板电脑、蓝牙设备、游戏产品和各种便携式消费电子产品。

台积电提供最全面的超低功耗技术平台,涵盖从0.18μm到16nm FinFET的工艺节点,满足物联网和智能穿戴创新的多样化需求。与之前的低功耗节点相比,台积电的 16nm 超低功耗工艺将工作电压降低了 20% 至 30%,从而降低了主备功耗,显着将 IoT 和可穿戴应用的电池寿命延长了 2 至 10 倍。

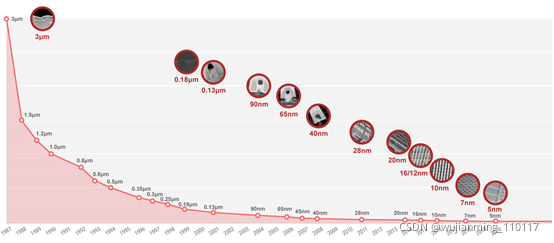

台积电自1987年成立以来,一直坚持“自主研发”的战略,这为公司带来了显着的竞争优势。

台积电是通过从台湾工业技术研究院转移 2 微米 (μm) 和 3.5 微米技术来创建公司的,它为飞利浦(荷兰)定制了 3.0 微米技术。仅仅一年后,台积电于1988年成功开发了自己的1.5μm技术。随后一系列持续的成功开发,包括1.2μm、1.0μm、0.8μm、0.6μm、0.5μm、0.3μm和0.25μm工艺。

1999年,台积电发布了全球首创的0.18μm Low Power工艺技术。从那时起,台积电创造了多项记录,以不断缩小的线宽技术引领行业,从 0.13 微米,到 90 纳米、65 纳米、40 纳米、28 纳米、20 纳米、16/12 纳米,再到当今最先进的 10 纳米和 7 纳米工艺。

由于其“建立内部研发”战略和对研发的持续投资,台积电是半导体技术的领导者,帮助全球公司释放其 IC 创新。

参考链接:

https://www.tsmc.com/english