STM32 ��̫�� ETHģ��˵��

1.overview

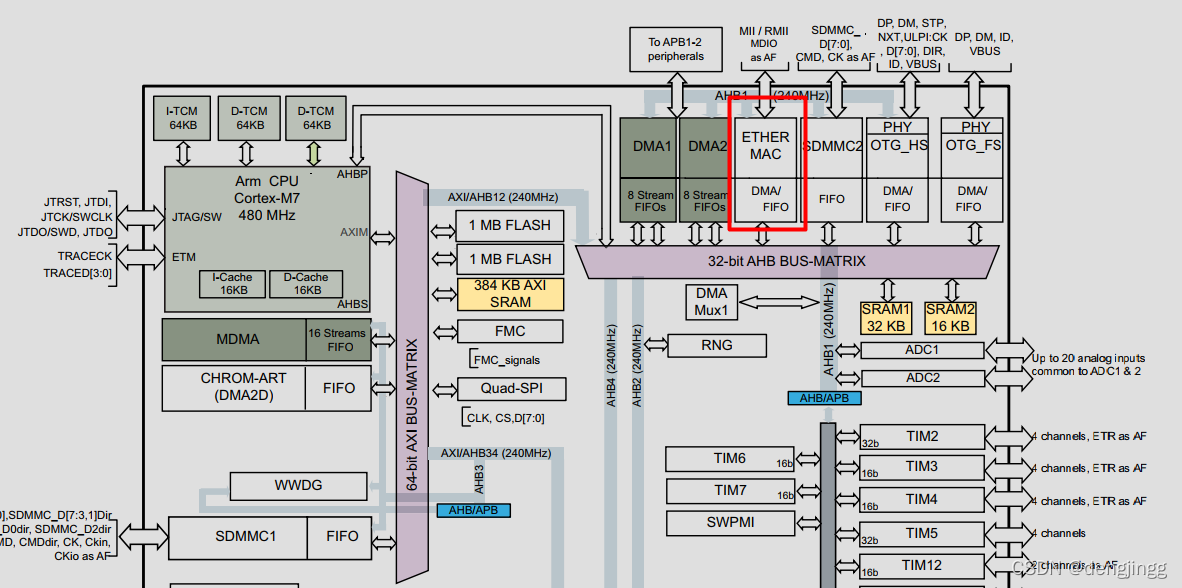

2.ETH module in stm32h743

STM32H743 ��

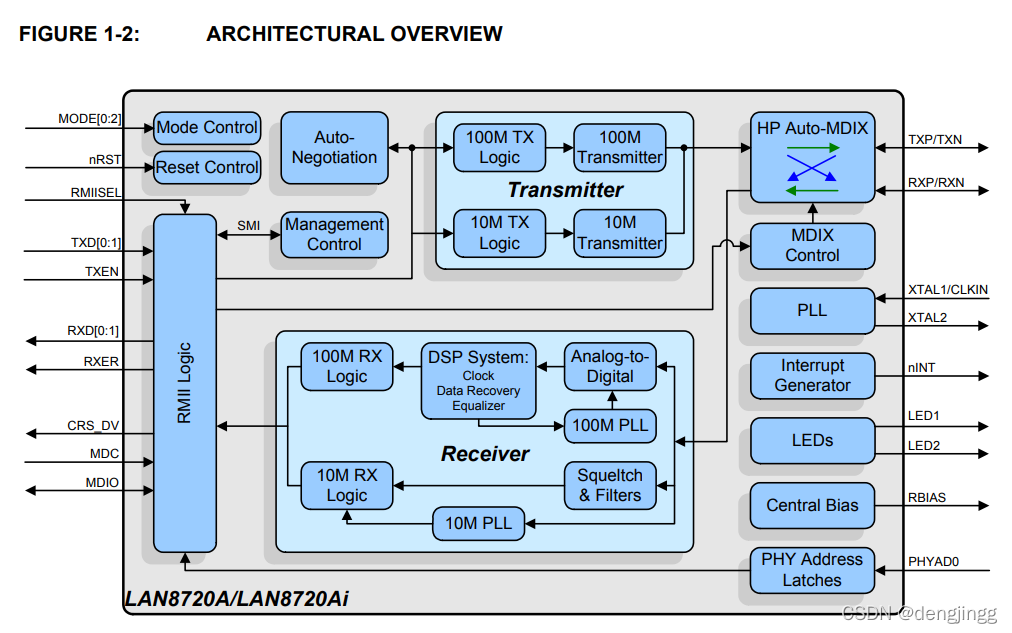

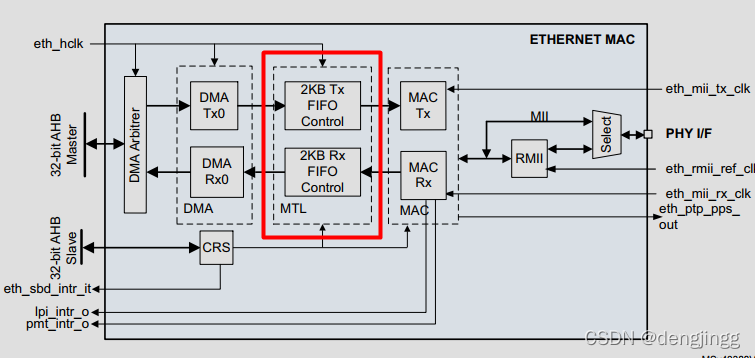

����һ��ͼ ETHER ģ�� �����ʾ ��STM32H743Ϊ��

32 BIt AHBΪ�ڲ��������� D2 ��,MasterΪ���Է����д��AHB������STM32 H743��������� Ϊ240MHz��

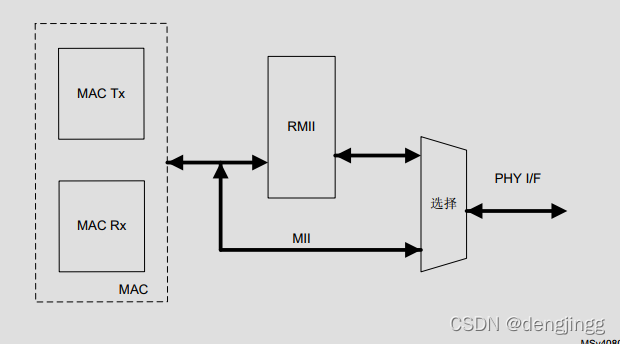

����ӿ�ΪMII/RMII

���ֵڶ���ͼ

Ethernet high-level block diagram

Eth_hclk ETH ģ���ʱ��Դ

Eth_hclk ETH ģ���ʱ��Դ

DMA Arb ��ģ���ⲿ AHB Master���������������ݵĶ�д���������� ����ר��DMA (���ݷ���DMA,���ݽ���DMA)��ֱ����� Tx,Rx FIFO (���Ϊ2K)��FIFO���������������ݼĴ��� MAC Tx,MAC Rx ,������RMII/MII ���������������PYH��

AHB Slave ���ɷ����д,CPUͨ��AHB Slave�ӿ�����CRS���ƼĴ�����������ETH��

1.���߽ӿ� ,�������ݴ��䡣Master ����DMA���ݵ� ����,Slave ����CPU��״̬�Ĵ����Ķ�д��

2.DMA

3.MTL ����FIFO

4.MAC ��̫��MACЭ�鴦��

5.RMII,MII�ӿ�

����������ͼ STM32 ETHģ����Ҫʵ��MAC��

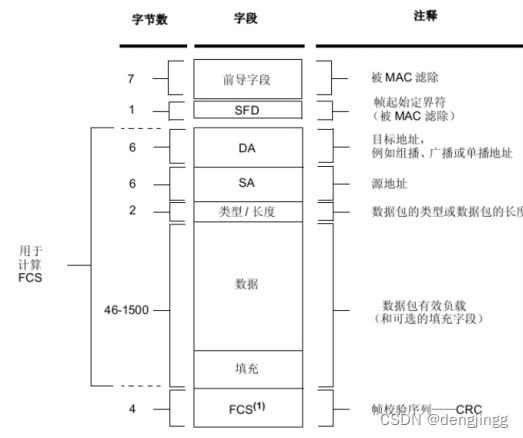

MAC���ݰ���ʽ

IEEE ����̫���ϴ�������ݰ���ʽҲ������ͳһ�涨,�����ݰ�����Ϊ MAC ���ݰ���

MAC ���ݰ���ǰ���ֶΡ�֡��ʼ�������Ŀ���ַ��Դ��ַ�����ݰ����͡������������У�������ɡ�

ǰ���ֶ�,Ҳ�Ʊ�ͷ,����һ�η���,����ʹ�շ��ڵ��ʱ��ͬ��������Ϊ���� 7 ���ֽ�,�� 0x55���ֶκ�֡��ʼ������� MAC �յ����ݰ�����Զ����˵���

? ֡��ʼ����� (SFD):��������ǰ���������ݶε�,����Ϊ 0xD5

? MAC ��ַ: MAC ��ַ�� 48 λ�������,����������������ַ,����̫���������ײ�,���Ǹ��� MAC ��ַ���շ����ݵġ����� MAC ��ַ���ڹ㲥�Ͷಥ,��ͬһ�������ﲻ����������ͬ�� MAC ��ַ�� PC �������ڳ���ʱ�Ѿ����ú��� MAC ��ַ,��Ҳ����ͨ��һЩ������������,��Ƕ��ʽ����̫���������п��ɳ���������á����ݰ��е� DA ��Ŀ���ַ, SA ��Դ��ַ��

? ���ݰ�����:������������������� MAC ���ݰ������� TCP/IP Э���� IP ���� ARP ������ SNMP ��,Ҳ�������������� MAC ���ݰ����ݶεij��ȡ������ֵ�����ô��� 0x0600,�����ڳ�������,��������������������,��ʾ����̫��֡��ص� MAC �ͻ���Э������ࡣ

? ���ݶ�:���ݶ��� MAC ���ĺ�������,���������������� MAC ���ϲ㡣�䳤�ȿ��Դ�0~1500 �ֽڼ�仯��

? ���ݶ�:���ݶ��� MAC ���ĺ�������,���������������� MAC ���ϲ㡣�䳤�ȿ��Դ�0~1500 �ֽڼ�仯��

? �����:����Э��Ҫ������ MAC ���ݰ��ij�������Ϊ 64 �ֽ� (���յ������ݰ��������64 �ֽڻᱻ��Ϊ������ͻ,���ݰ����Զ�����),�����ݶε��ֽ����� 46 �ֽ�ʱ,���������Զ�������Ч����,��ʹ���ݰ����ϳ���Ҫ��

? У�����: MAC ���ݰ���β����У�����,�������� CRC У������,���ڼ����

MII �� RMII �ӿ� ETH ����ӿ�����PHYоƬʵ�������㴫��

ͼ��

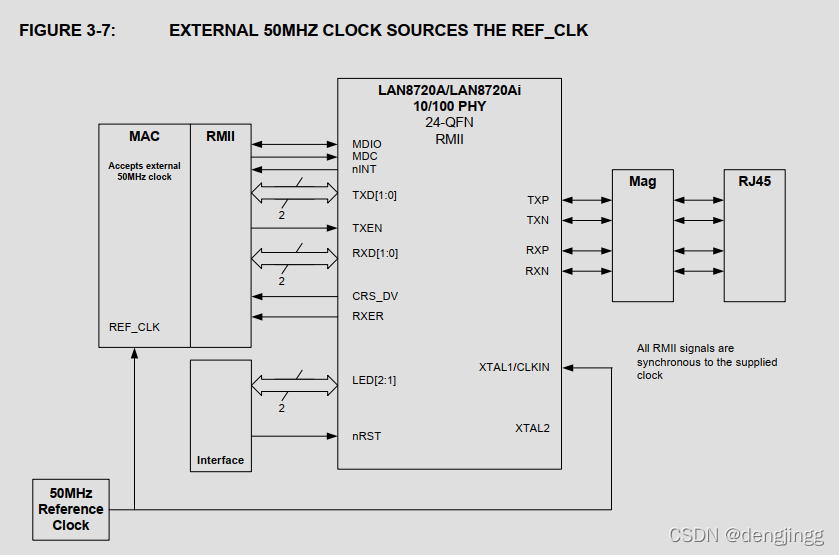

PHY:ʾ�� LAN8720A

ͼ��

�߶ȳ���ͼ����

ģ�����ͼ����

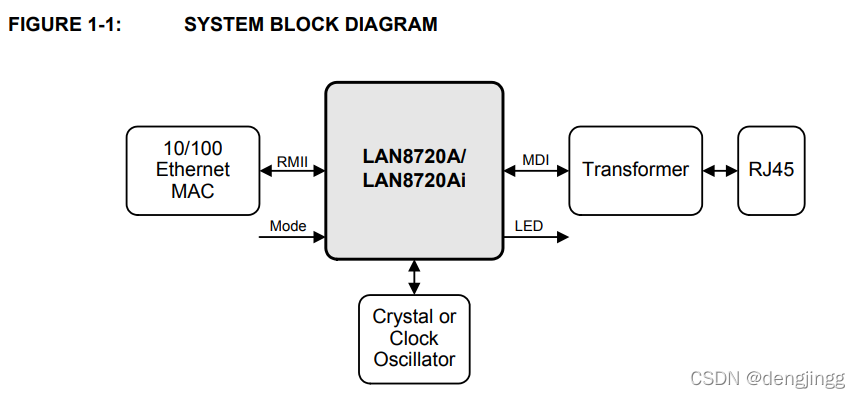

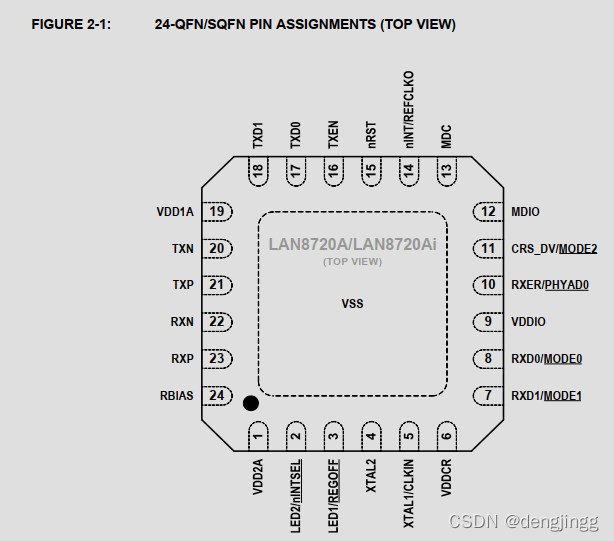

����LAN8720A/LAN8720AI �����ֲ�

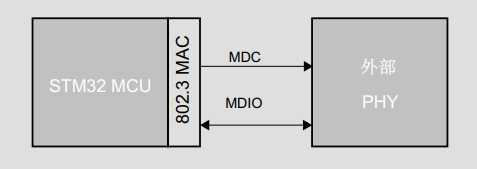

�������Ҫ��RMII�ӿڶԽ�MCUʵ�����ݵ�����,�Լ�LAN8720 �Ĵ������ö˿�MDC,MDIO

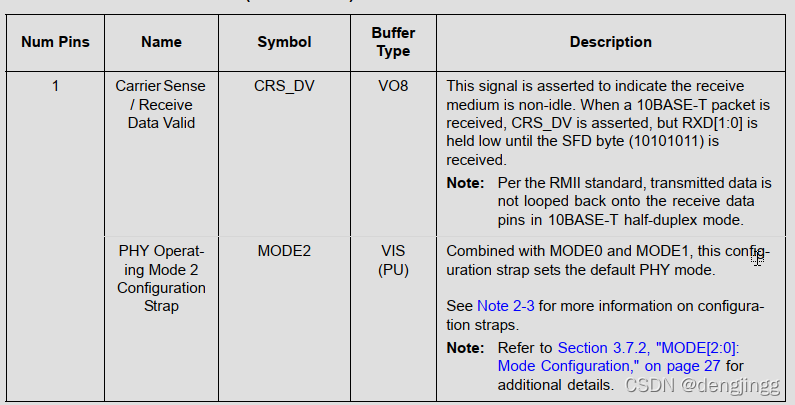

���ұ���PHY���(���ߵ�ƽ���)

�м�����ģ�� RMII���ӿ�,����ģ��,����ģ�顣Ҫ��һ���ij����ӽǡ�

һ���װ��ʽ,С��,������

������ʾ

2. ETH Mode in STM32H743

eth_hclk Digital input AHB clock

eth_hclk Digital input AHB clock

eth_sbd_intr_it Digital output Main Ethernet interrupt

lpi_intr_o Digital output Sideband signal generated when the transmitter or receiver enters or exits the LPI state.

pmt_intr_o Digital output Sideband signal generated when a valid remote wakeup packet is received

eth_mii_tx_clk Digital input MII Tx kernel clock

eth_mii_rx_clk Digital input MII Rx kernel clock

eth_rmii_ref_clk Digital input RMII reference kernel clock

eth_ptp_pps_out Digital output PTP pulse-per-second signal

��̫�������� 4 ����Ҫ����ģ�����:

1 ���ƺ�״̬�Ĵ���ģ�� (CSR),���ڿ���ͨ�� AHB 32 λ�ӽӿڽ��еļĴ�������

2ֱ�Ӵ洢�����ʽӿ� (DMA)

��Ϊ�� DMA ģ��,���� 1 �����ڽ��յ�����ͨ���� 1 �����ڷ��͵�����ͨ������ģ

�����ڿ���ͨ�� AMBA AHB 32 λ���ӿ��� MAC ��ϵͳ�洢��֮����е����ݴ��䡣

3���ʷ��ʿ���ģ�� (MAC),����ʵ����̫��Э��MAC ����� (MTL),�������Ӧ�ú� MAC ֮���������

DMA ������

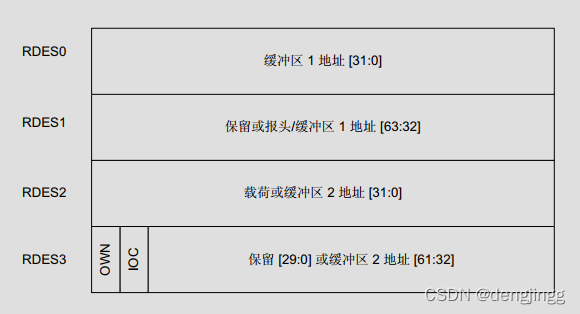

DMA ���ж����ķ��� (Tx) �ͽ��� (Rx) ���档 Tx ���潫���ݴ�ϵͳ�洢�����䵽 MAC ����� (MTL),�� Rx ���潫���ݴ��豸�˿� (PHY) ���䵽ϵͳ�洢����

��̫���������������ٶȿ�,���������²��ʺ�CPU�ĸ�Ԥ,DMA����̫��������Ϊ����ѡ�����ETHģ�����Դ���ר����̫��DMAģ�顣DMAģ�鸺�����ݰ���,���Ը�����̫�����������ص��ر���Ƶ�DAM��

DMA��MAC���յ������ݰ����䵽ϵͳ�ڴ��е�Rx������,��Tx���ݰ���ϵͳ�ڴ��е�Tx�������д����ȥ��פ����ϵͳ�ڴ��е�����������ָ����Щ��������ָ�롣

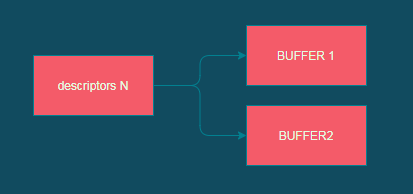

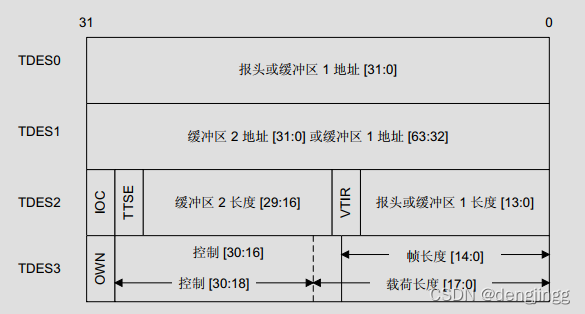

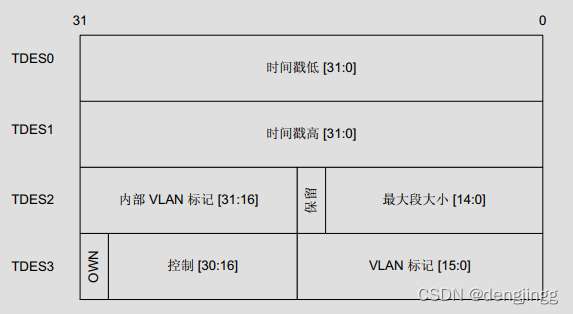

DMA �����ݽṹ ������ descriptors

The base address of each list is written to the respective Tx and Rx registers: Channel Txdescriptor list address register (ETH_DMACTXDLAR)) and Channel Rx descriptor listaddress register (ETH_DMACRXDLAR))

descriptor ��һ���̶���ʽ������,��Ҫȷ��descriptor list �б�����

DMA �������б��е����һ����������,���Զ���ת���б���ַ�Ĵ����е���ʼ������,���γ�һ������������

�������б�λ��Ӧ�õ������洢��ַ�ռ��ڡ�ÿ������������ָ�����������������,��ʹ�ò���������ʽѰַ����������,���Ǵ洢���е�������������

��ָ��Ļ�����(BUFFER1��2) ������Ӧ�ó����С���С���ᳬ��һ������ ��������ֻ�������ݡ�������״̬�������������С�

ÿ������������������������������������ַָ�롣

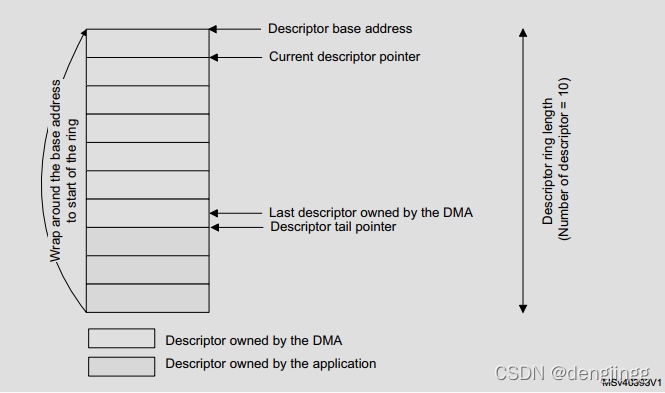

descriptors ��ĵ�ַ���,descriptors����������Ӧ�ļĴ���

descriptors βָ��Ĵ�����ʾ descriptors N DMA ���������ӵ�tailָ�롣��ʵ��ַ��tail �м��descriptors ��DMA���ʵ����䡣

��ͼ��ʾ

base address Ϊdescriptors ��ʼ��ַ�� tailΪDMA�Զ�+1 ��ĩβ��ַ����ǰdescriptors ָ���ʾ����ʱ����ʹ�õ�descriptors ��

����descriptors �����βָ���൱,��ôDMA����ִ��+1,��������״̬Current Descriptor Pointer == Descriptor Tail Pointer;,ӦΪ��δ��Length (descriptors list ����)���Բ������ص���ʼ��ַ��ͨ���ñ�βָ���λ�þͿ��Խ��������Current Descriptor Pointer < Descriptor Tail Pointer;

����һ���������ݰ�,��̫������ DMA ������Ҫһ��descriptors�����������������������ֽڼ�����������������ַָ��֮��,���������������п����ֶ�,�����ֶο����ڰ��������ݰ������� MAC ������

descriptors ���ݽṹ�кܶ���

��ΪTX,RX д,�� ����ο��ֲ�������

�������ǶԷ������ݰ�����Ϣ���м�¼��

The MAC Transaction Layer (MTL)

MAC ����� (MTL) �ṩ FIFO �洢���ӿ�,������͵���Ӧ��ϵͳ�洢���� MAC ֮������ݰ�������������Ӧ��ʱ�Ӻ� MAC ʱ����֮��ʵ�����ݴ��䡣 MTL ��������� 32 λ��������·��:����·���ͽ���·����

����·��

Ӧ�û��ڲ� DMA ����Ӧ�û�ϵͳ�洢���ж�ȡ����̫�����ݰ����뵽 Tx FIFO�����ﵽ������ֵ(��ֵģʽ)���������ݰ����ڶ�����(�洢ת��ģʽ)ʱ,��Ӧ���ݰ������������䵽 MAC������ EOP ��,���� MAC ��ȡ����״̬�����ͻ�Ӧ�û��ڲ�DMA�� Tx ���д�СΪ 2048 ���ֽڡ�

����·��

MTL Rx ģ��� MAC �������ݰ�,���������� Rx ���С������г������õĽ�����ֵ( Rx ���й���ģʽ�Ĵ��� (ETH_MTLRxQOMR) �ж���� RTC λ [1:0])ʱ,�����ڽ��յ��������ݰ���,�Ὣ���е�״̬(��伶��)�����Ӧ�û� DMA�� MTL ��ָʾ������伶��,�Ա� DMA �������ӿڷ���Ԥ���õ�ͻ�����䡣 Rx ���д�СΪ 2048 ���ֽڡ�

MAC

MAC ������̫��Э�鴦�����ڷ���ģʽ��,���� MTL ��������,Ȼ���ٽ��䴫�͵� PHY�ӿڡ��ڽ���ģʽ��, MAC �� PHY �ӿڽ�������,Ȼ���ٽ��䴫�͵� MTL ģ��� RxFIFO��

MAC transmission MAC���ݴ���ʱ��

������������:

- �� MTL Ӧ���� SOP(���ݰ���ʼ)�ź���Ϊ��Ч���������������ʱ,���������͡�

- �� SOP �ź�ʱ, MAC �������ݲ���ʼ�� MII ���͡�

- �� EOP(���ݰ�����)���͵� MAC ʱ, MAC ִ�����²���֮һ:

�C MAC ��ɳ��淢��,���� MTL �ṩ����״̬��

�C ����ڷ����ڼ䷢�������ͻ(��˫��ģʽ��) ,�� MAC �Ὣ����״̬�ṩ�� MTL,

ͬʱ����λ�� 1�� MAC ���ṩ��������,ֱ����������һ������Ϊ��:

���ݰ��ѳɹ�����

�ﵽ���������������������������, MAC ��ֹ���ݰ�����,�����ڹ��ȳ�ͻ����״̬�� MAC ���ܲ��������к�������,ֱ�����յ���һ�� SOP��������MAC ����������(��״̬��)ʱ, MTL ģ��Ӧ�� SOP ���·���ͬһ���ݰ���

�C �������������һ���,�� MAC ����ֹ���ݰ�����:

���ز�(��˫��ģʽ)

�ز���ʧ(��˫��ģʽ)

�����ӳ�(��˫��ģʽ)

�ӳٳ�ͻ(��˫��ģʽ)

MAC ���ܲ��������к�������,ֱ�����յ���һ�� SOP�� - ��������ڼ� MTL �������ṩ����, MAC ����������״̬�� MAC ���ܲ���������

��������,ֱ�����յ���һ�� SOP�� - �� MTL �����������ݰ��ڼ�,��� MAC ��δ���ǰһ���ݰ��� EOP ������½��յ�

SOP,�����Ը� SOP �����µ����ݰ���Ϊǰһ���ݰ���������

MAC reception MAC�����ݽ���

�� MAC �� MII �ϼ� SFD ʱ,���������ղ����� MAC ��ȥ����ͷ�� SFD,Ȼ���ټ����������ݰ�����鱨ͷ�ֶ��Խ��й���, FCS �ֶ�������֤���ݰ��� CRC�����յ����ݰ��洢��dz��������,ֱ��ִ�е�ַ���ˡ�������ݰ�δͨ����ַ������,����� MAC �н��䶪����

������������:

-

MII �Ľ���������Ч�ź� (RxDV) ����ʱ,����״̬�� (RSM) ��ʼѰ�� SFD �ֶ�( MIIģʽ�µ� 0xD ���ֽ�)��

״̬���ᶪ�����յ������ݰ�,ֱ���� SFD�� -

�� SFD ʱ,״̬����ʼ�� RPC ģ�鷢����̫�����ݰ�������,�� SFD ֮��ĵ�һ���ֽ�(Ŀ���ַ)��ʼ���͡�

-

���ʹ���� IEEE 1588 ʱ�������,���� MII �ϼ��κ����ݰ��� SFD ʱ, MAC ��

����ȡϵͳʱ��Ŀ��ա������ MAC �����ڼ�����ݰ�δ������,��ʱ��������ݸ�Ӧ�ó��� MAC �����յ��İ��ֽ�����ת�����ֽ�,������Ч���ݰ�����ת���� RFCģ�顣

-

����״̬�������ڽ��յ���̫�����ݰ��ij���/�����ֶν��н��롣�������/�����ֶ�С�� 1,536 ����Ϊ MAC ������Զ�ȥ�� CRC/Pad( ����ģʽ���üĴ��� (ETH_MACCR) ��λ 20),��״̬�����������ݰ�����(����������������/�����ֶ���ָ��������),Ȼ��ʼ�����ֽ�(���� FCS �ֶ�)��״̬���Գ���/�����ֶν��н��벢��鳤�Ƚ�����

-

������/�����ֶδ��ڻ���� 1,536 ʱ,�����δʹ�ܹ���ģʽ���üĴ��� (ETH_MACCR)λ 21 �е��������ݰ��� CRC ȥ��,�� RPE ģ��Ὣ���н��յ�����̫�����ݰ����ݷ��͵� RFC ģ�顣����,�����ʹ���������ݰ��� CRC ȥ��,��δʹ�ܽ���У��ͼ�

������,�� MAC ��ȥ��������������̫�������ݰ������ 4 ���ֽ�,Ȼ�����ݰ�ת����Ӧ�ó��� -

Ĭ�������,�� MAC ���Ϊʹ�ܿ��Ź���ʱ��,���� RPE ģ���л��жϴ��� 2,048(���ʹ�ܾ������ݰ�,��Ϊ 10,240)�ֽڵ����ݰ�(DA + SA + LT + ���� + PAD + FCS)������,������ʹ�ÿɱ�̿��Ź���ʱ��(���Ź���ʱ�Ĵ��� (ETH_MACWTR) ��λ 16)

���� 2,048 �� 10,240 �ֽڵĹ̶���ʱ�� ��ͨ����̹���ģʽ���üĴ��� (ETH_MACCR)��λ 19 ����ֹ���Ź���ʱ��������,��ʹ��ֹ���Ź���ʱ��,Ҳ�Խ��жϴ��� 32 KB�����ݰ����������Ź���ʱ״̬

Ethernet functional description: MAC ��̫����������

���ݺܶ� ����ο������ֲ�

���ݰ�����

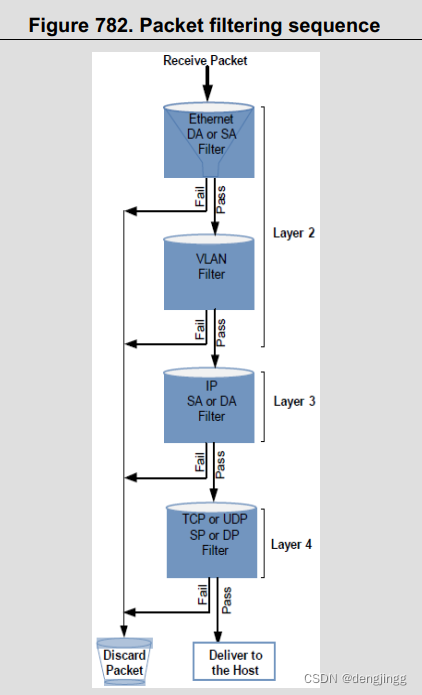

MAC ֧�ֶ� Rx ���ݰ������������͵Ĺ���:

MAC Դ��ַ��Ŀ���ַ����:��ַ����ģ�� (AFM) ���ÿ���������ݰ���Դ��ַ��Ŀ���ַ�ֶΡ�

VLAN ����: MAC ֧�ֻ��� VLAN ��ǵĹ��˺� VLAN ɢ�й��ˡ�

�� 3 ��͵� 4 �����:�� 3 �������ָ IP Դ��ַ��Ŀ���ַ���ˡ��� 4 �������ָԴ�˿ں�Ŀ��˿ڹ��ˡ�

4���©��

IEEE 1588 ʱ���

IEEE 1588 �������˾���ʱ��Э�� (PTP),��Э��֧��ʹ������ͨ�š��������ͷֲ�ʽ����ȼ���ʵ�ֵIJ����Ϳ���ϵͳ�еľ���ʱ��ͬ���� PTP ����������֧�ֶಥ��Ϣ���͵ľ�����(��������������̫��)����ͨ�ŵ�ϵͳ����Э��ɶԷǾ���ϵͳ����ͬ��,����ϵ

ͳ�������о��ȡ��ֱ��ʺ��ȶ��Զ����ϱ仯��ʱ�ӡ���Э��֧�����뷶Χ��ϵͳ��ͬ������,������Ҫ���ٵ�����ͱ���ʱ�Ӽ�����Դ����̫������֧�� IEEE 1588-2002(�汾 1)�� IEEE 1588-2008(�汾 2)�� IEEE 1588-2002֧��ͨ�� UDP/IP ���͵� PTP�� IEEE 1588 2008 ֧��ͨ����̫�����͵� PTP������Ϊ�����ֱ��ṩ�˿ɱ��֧�֡���֧�����й���:

? ֧������ʱ�����ʽ

? �ɻ�ȡ�������ݰ���� PTP �����ݰ��Ŀ���

? �ɻ�ȡ���¼���Ϣ�Ŀ���

? �ɻ���ʱ�����ͻ�ȡ����:��ͨ���߽硢�˶Զ����͵�Ե���

? �ɽ��ڵ�ѡ����ͨ�ͱ߽�ʱ�ӵ����ڵ��ӽڵ�

? ʶ�����ݰ���ֱ��ͨ����̫�����͵� PTP ��Ϣ���͡��汾�� PTP ��Ч����,������״̬

? ֧�����ֻ�����Ƹ�ʽ�IJ������뼶ʱ��

MAC ���ɵ��ж�

MAC �����ڸ����¼��������жϡ���Щ�ж��¼��� DMA �е��¼�������� eth_sbd_intr_it�źš� MAC �ж�Ϊ��ƽ���ж�,���ڱ�Ӧ�ó�����������֮ǰʼ�ձ�����Ч(�ߵ�ƽ)���ж�״̬�Ĵ��� (ETH_MACISR) �����˿��ܵ��� MAC �����жϵ��¼���Ĭ������� MAC

�жϴ���ʹ��״̬����ͨ�����ж�ʹ�ܼĴ��� (ETH_MACIER) �е���Ӧ����λ�� 1,����ֹ�����¼��� eth_sbd_intr_it �ź��ж���Ϊ��Ч���жϼĴ���λ��ָʾ�����¼���ģ�顣�����ȡ��Ӧ��״̬�Ĵ����������Ĵ�����������жϡ�

PHY �ӿ�

ͼʾ�dz�������û��ʲô��˵�ġ�

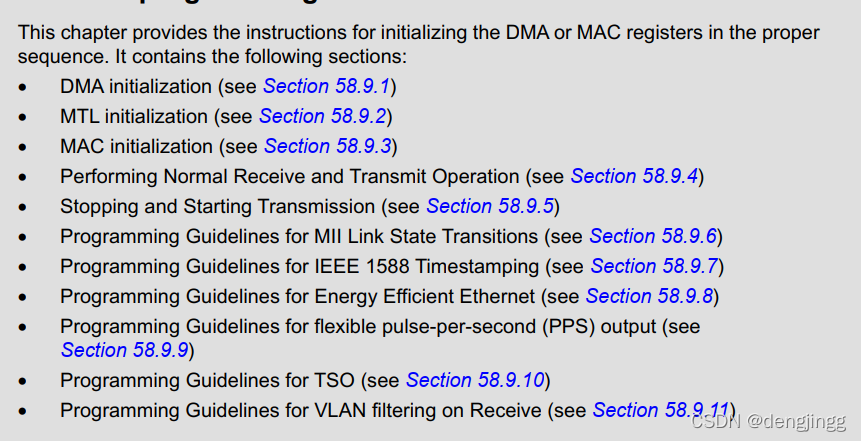

Ethernet programming model

���������̫��ģ��,����Ƚϸ���,��ϸ���̲ο��ֲ�

PHY LAN8720A/LAN8720AI

LAN8720 ����MAC ��RMII�ӿڵ�����

���Ŷ�������ͼ��ʾ

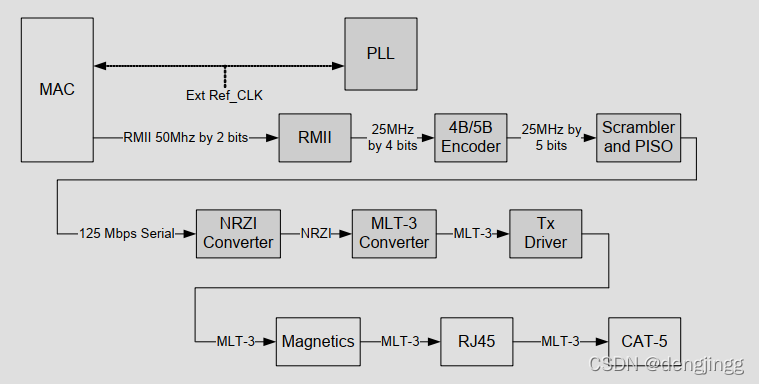

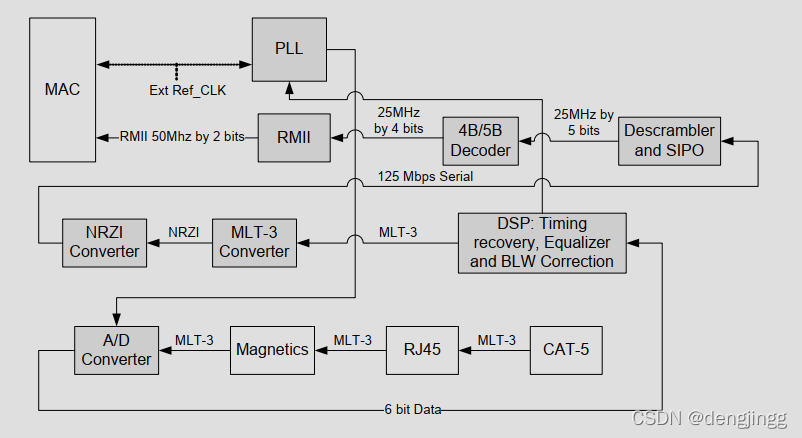

���幦�ܶ�������ͼ��ʾ

����������

Ext Ref clk Ϊ�ⲿʱ�Ӷ���MCU(MAC)��PHY��˵,�ⲿʱ��ͬʱ�����������ṩʱ��Դ��

RMII�ӿ�TX Ϊ2Bit ͨ��RMII�ӿڴ��䵽 4B/5B ������ 50Mhz ˫��2bit�ӿ� ����4bit������Ҫ����ʱ���������� 4bit ����Ƶ��Ϊ 50/2=25MHz��

���չ���������ʾ��