目录

1.命名规则

101基本型,102USB基本型,103增强型,105或107互联型

T:36脚,C:48脚,R:64脚,V:100脚,Z:144脚

C:256K SRAM(储存), D:384K SRAM, E:512K SRAM

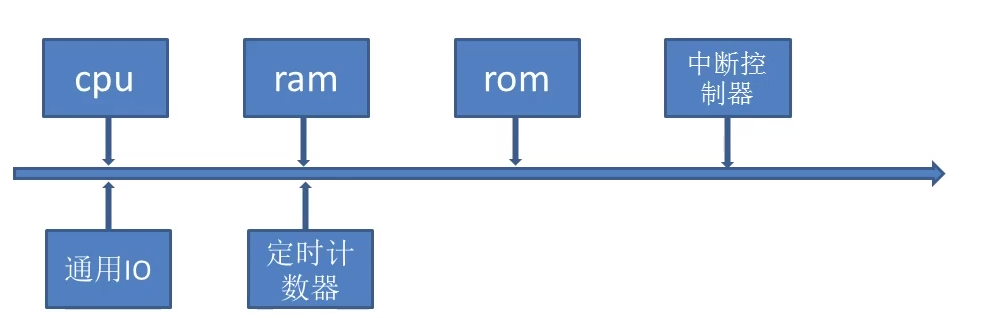

2.STM32大致总结构

CPU+中断控制器然后通过总线连接其他,同时拥有大量外设。

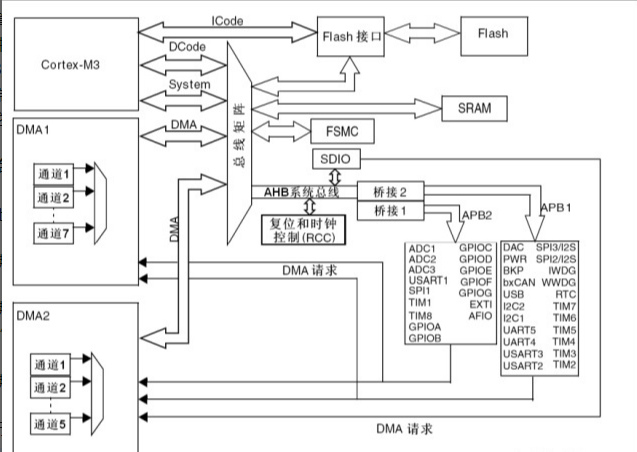

3.驱动单元 :DMA1、DMA2、系统总线以及内核总线。

Icode总线:

写好的程序通过编译变成一条条指令存储在外设的FLASH里面,内核要读取这些指令来执行程序就必须通过Icode总线(专门用来取指)

DCode总线与DMA总线:

常量const 存放在内部FLASH里面,而变量存在内部SRAM里面。这些数据可以由DCode和DMA来读取,为了避免两者同时去读取数据从而造成冲突,所以在两者读取数据的时候会有一个总线矩阵来裁定谁来读取数据

System总线:

读取数据,最主要还是用来访问外设的寄存器,即读写寄存器都是通过这条总线来完成的

DMA总线:

这条总线主要也是用来传输数据的,这个数据可以是某个外设的数据寄存器,可以是SRAM,可以是内部的FLASH

(百度解释:直接存储器存取用来提供在外设和存储器之间或者存储器和存储器之间的高速数据传输。无须CPU的干预,通过DMA数据可以快速地移动。这就节省了CPU的资源来做其他操作)

举个例子:如果我们没有DMA ,现在要从SRAM里读取一个数据到内部的外设数据寄存器DR,首先CPU通过DCode总线将数据从SRAM读到CPU的内部的通用寄存器里来暂存数据,然后在通过DCode总线将数据传到DR,这样通过了CPU作为数据的中转。但是我们现在有了DMA总线,只需要CPU发送命令就可以将SRAM里的数据直接发送到DR

4.被动单元:APB设备、APB桥、内部Flash及SRAM

内部FLASH:

内部闪存存储器,我们编写好的程序通过编译后变成一条条指令存放在这里,Crotex-Mx通过ICode总线访问内部FLASH来取指

内部SRAM:

一个具有静止存取功能的内存,他不像DRAM那样,他不需要刷新电路即能保存它内部存储的数据。每隔一段时间都要对DRAM刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有缺点,它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,所以在主板上SRAM存储器要占用一部分面积。

所以SRAM的优点就是速度快,不必配合内存刷新电路:缺点是集成度低,功耗较大。 像程序的变量,堆栈等等的开销都是基于内部的SRAM,Crotex-Mx通过DCode总线来访问它。

FSMC:

可变静态存储控制器,这是STM32系列采用一种新型的存储器扩展技术,由于通过对特殊功能寄存器的设置,FSMC能够根据不同的外部存储器类型,发出相应的数据/地址/控制信号类型以匹配信号的速度,从而使得STM32系列微控制器不仅能够应用各种不同类型、不同速度的外部静态存储器,而且能够在不增加外部器件的情况下同时扩展多种不同类型的静态存储器,满足系统设计对存储容量、产品体积以及成本的综合要求。

5.图解

以总线矩阵为分界线,左边是驱动单元,右边是被动单元

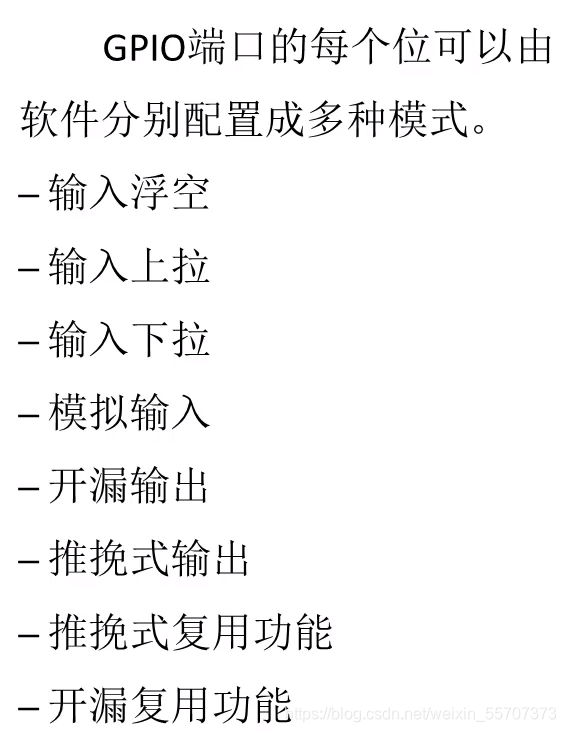

6.GPIO

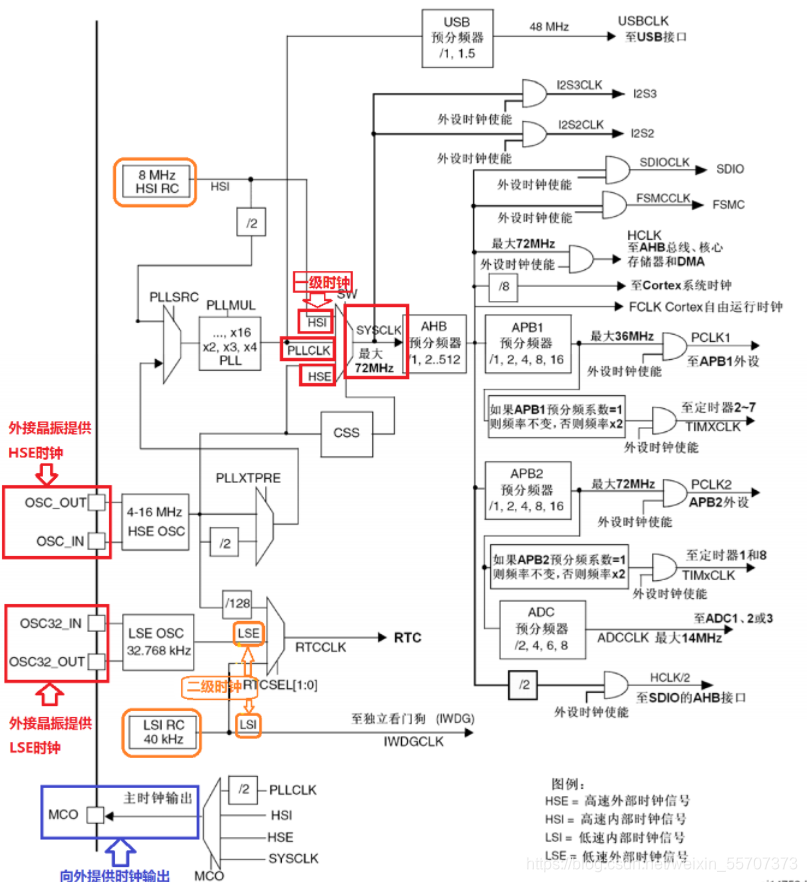

7.时钟树

第一级时钟:

高速内部时钟(HSI)

锁相环时钟(PLLCLK)

高速外部时钟(HSE)

第二级时钟:

低速内部时钟(LSI)

低速外部时钟(LSE)

详解:

1.HSI是高速内部时钟,RC振荡器频率为16MHz,可以直接作为系统时钟或经过二分频后用作PLL的输入

2.HSE是高速外部时钟,可接4~26MHz石英陶瓷谐振器或者接外部时钟源,可以直接作为系统时钟或经过二分频后用作PLL的输入

3.LSE是低速外部时钟,接32.768KHz石英晶体,主要是RTC时钟源

4.LSI是低速内部时钟,RC振荡器,32KHz左右,供独立看门狗和自动唤醒单元使用

5.PLL围锁相环倍频输出,32上面有两个PLL