STM32驱动AD7656程序

AD7656程序源码

我采用的是 并行接口 进行AD7656模块与STM32L431RCT6进行通信

一、AD7656特性:

1.6个独立ADC

2.真双极性模拟输入

3.引脚/软件可选范围:+/-10V、+/-5V

4.高吞吐速率:250KSPS

5.低功耗:140mW(250KSPS,5V电源)

6.高速并行、串行和菊花链接口模式

7.高速串行接口:SPI 、QSPI、 MICROWIRE、 DSP兼容

8.待机模式:最大315uW

9.64引脚LQFP封装

10.内置6个1/14/12位,快速、低功耗逐次逼近型ADC

二、引脚使用

1.DATAR0-DATAR15 并行数据输出引脚

2.ADBUSY 输出繁忙。开始转换时,此引脚变为高电平,并保持高电平直到转换完成,并且转换数据被锁存到输出数据寄存器。如果BUSY信号处于高电平,由于会忽略任何施加的CONVST边沿,因此无法启动新的转换。

3.ADCS 片选。此引脚低电平有效逻辑输入使能数据帧传输。如果CS和RD均处于逻辑低电平,同时选择并行接口,则会使能输出总线,使转换结果被输出在并行数据总线上。如果CS和WR均处于逻辑低电平,同时选择并行接口,则利用DB[15:8]将数据写入片上控制寄存器。当选择串行接口时,利用CS使能串行数据帧传输,并逐个输出串行数据的最高有效位(MSB).

4.ADOE(RD) 读取数据。如果CS和RD均处于逻辑低电平,同时选择并行接口,则会启用输出总线。当选择串行接口时,RD线路应保持低电平。

5.RANGE 模拟输入范围选择,逻辑输入。此引脚的逻辑电平决定模拟输入通道的输入范围。当此引脚在BUSY下降沿为逻辑1时,下一次转换的范围为+/-2VREF。当此引脚在BUSY下降沿为逻辑0时,下一次转换的范围为+/-4VREF。

在硬件选择模式下,在BUSY下降沿检查RANGE引脚。在软件模式(H/S SEL=1)下,可将RANGE引脚和DGND相连,然后由控制寄存器内的RNGA、RNGB、RNGC位决定输入范围

6.ADCOV 转换开始输入A,转换开始输入B和转换开始输入C,这些逻辑输入用来启动ADC对转换。CONVST A用来启动V1和V2同步转换。CONVST B用来启动V3和V4同步转换 CONVST C用来启动V5和V6同步转换。当其中一个引脚从低电平变为高电平时,所选ADC对的取样保持开关从采样切换到保持,然后便启动转换。利用这些输入端,还可让ADC对进行部分省电模式。

7.ADRST 复位输入。设置为逻辑高时,此引脚可复位。

8.ADREFA 基准源去偶电容A

9.ADREFB 基准源去偶电容B

10.ADREFC 基准源去偶电容C

11.ADREF 基准电压输入/基准电压输出。可通过此引脚提供片上基准电压。或者,可禁用内部基准电压,并将外部基准电压施加到此输入端。参见内部/外部基准电压部分。启用内部基准电压时,利用至少一个1uf去偶电容对此引脚去偶。

12.VDD 正电源电压,这是模拟输入部分的正电源电压

13.VSS 负电源电压,这是模拟输入部分的负电源电压

14.V1-V6 模拟信号输入

注意: VDD 和 VSS必须接,否则6路通道采集不到数据

VDD 正电源电压,这是模拟输入部分的正电源电压

VSS 负电源电压,这是模拟输入不得的负电源电压

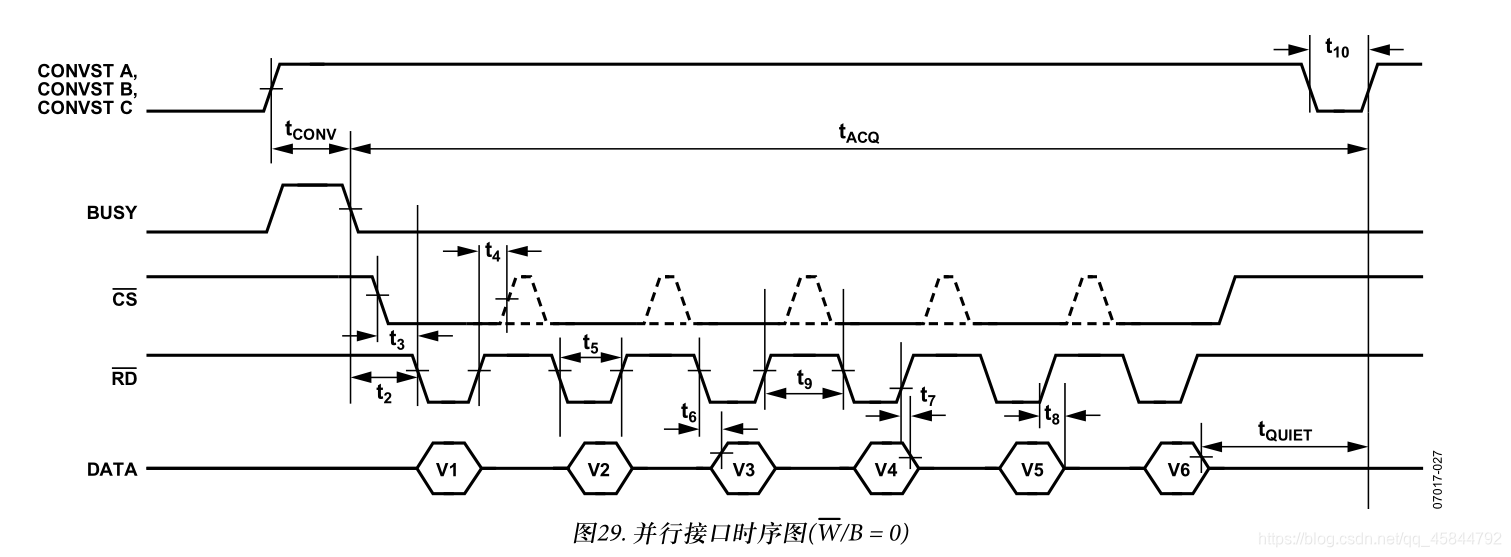

三、并行接口工作原理

采用并行工作模式,首先由CONVST引脚启动转换(CONVST脉冲应包括一个CONVST下降沿随后为一个CONVST上升沿),并保持为高电平。然后由AD7656在启动转换信号后输出BUSY信号,当BUSY信号出现下降沿时,代表AD模块转换已经结束。此时,AD7656内部的寄存器已经保存了转换的数据,可通过控制片选CS和读信号RD来依次读取各个通道的AD转换值。读取转换值后,可改变CONVST为低电平,为下一次转换做好准备。注意:一定要保证AD转换过程中CONVST为高电平。

注意:片选信号CS和读数据信号RD用CPU的引脚模拟时序,把CPU的数据引脚连接到AD7656的数据输出引脚上,同时读取AD7656输出的16位数据,进行转换计算

并行接口时序图

四、AD7656取值范围

-32768 - 32768 第一位是符号位 ;满值是7FFF

程序源码在最上面进行下载