1 ZYNQ���

(1)ZYNQ���

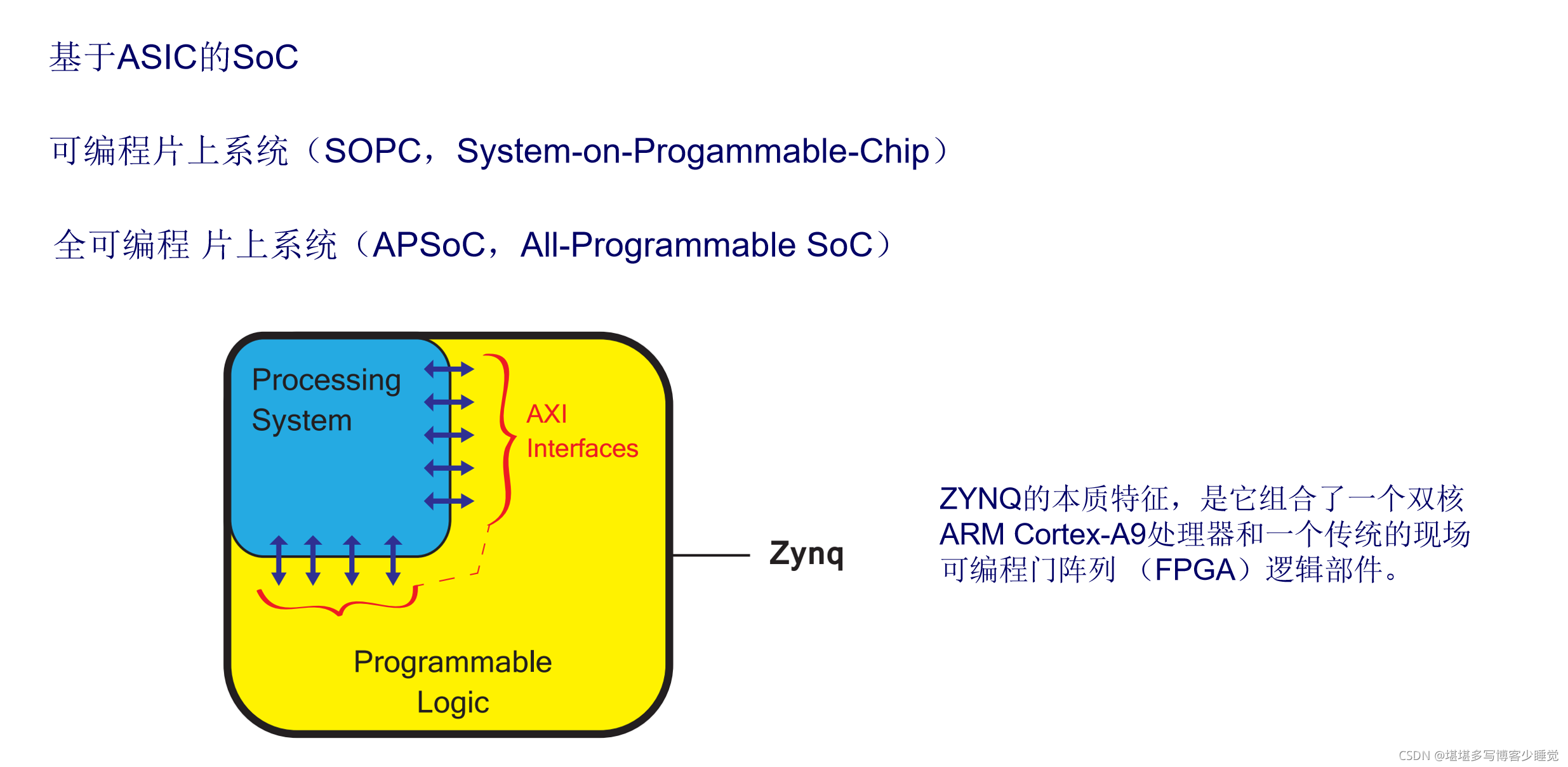

? ZYNQȫ��Zynq-7000 All Programmable SoC,������˼��˾(Xilinx)�Ƴ�����һ��ȫ�ɱ��Ƭ��ϵͳ((APSoC)(ȫ�ɱ��ָ����Ӳ�������������Ա��),ZYNQ �ı�������,���������һ��˫�� ARM Cortex-A9 ��������һ����ͳ���ֳ��ɱ��������(FPGA)�������������������������ɱ������FPGA��Ӳ���ɱ���Խ�����������,���ṩ�����ױȵ�ϵͳ���ܡ�����������չ�ԡ�

? ZYNQּ��Ϊ��Ƶ��ء�������ʻԱ�����Լ������Զ����ȸ߶�Ƕ��ʽӦ���ṩ����Ĵ���������������ܡ�������ARM��������SoC�����㸴��Ƕ��ʽϵͳ�ĸ����ܡ����ĺͶ�˴���������Ҫ��

(2)Ƭ��ϵͳ,����ϵͳ,�ɱ��Ƭ��ϵͳ,ȫ�ɱ����ϵͳ

1.����ϵͳ

? һ���ܹ�ʵ��һ�����ܵĵ�·ϵͳ�ɶ��ģ�鹹��,�紦�������ӿڡ��洢����ģ��ת�����ȵȡ���Щ����ģ������ɷ�����������ʵ��,Ȼ����ӡˢ��·��(PCB)���������,�����γ�����ϵͳ(System-on-a-Board)��

����ͼ��ʾ�İ���ϵͳ��,��ɫ�ľ��δ���ӡˢ��·��(PCB),���������ɫ��С���δ�����ϵͳ�и�������ģ��,��洢���ȡ���Щģ��Ĺ��ܶ���һ���������Ĺ�оƬ�ֱ�ʵ�ֵ�,����֮��ͨ�� PCB �� �Ľ�����������,���չ���һ��������ϵͳ��

2.Ƭ��ϵͳ(SOC)

? ��**Ƭ��ϵͳ(System-on-Chip)**ָ�����ڵ�����оƬ�Ϳ���ʵ������ϵͳ�Ĺ��ܡ�

? ����ͼ��ʾ,Ƭ��ϵͳ SoC ��һ��оƬ���ʵ���˴洢�����������ͽӿڵȸ�������ģ��,�����������ϵͳ����,��Ҫ�ü�����ͬ������оƬ��ʵ�֡������ϵͳ���,SoC �Ľ�������ɱ�����,���ڲ�ͬ��ϵͳ��Ԫ֮��ʵ�ָ������ȫ�����ݴ���,���и��ߵ�����ϵͳ�ٶȡ����͵Ĺ��ġ���С�������ߴ���õĿɿ��ԡ�

? �ڹ�ȥ,SoC ������ﳣ����ָר�ü��ɵ�·(Application Specific Integrated Circuit,ASIC)������ ASIC�� SoC �Ĵ��������Ӱ����� PC��ƽ��������ֻ���ʹ�õĴ�����,�绪Ϊ�콢�ֻ��е�����ϵ��оƬ����Щ���������͵��������������������ˡ��洢����ͼ�δ��������ӿں���������ģ����������ġ����� ASIC�� SoC ����Ҫȱ��������:1���������ڳ��ҳɱ���;2��ȱ������ԡ����� ASIC ʱ�������õĹ���Ͷ���Ǿ��,ʹ������ SoC ����ֻ�ʺ��ڴ����������������IJ�Ʒ�С�ASIC SoC �ľ����Ե������Dz������ںܶ�Ӧ��,�ر��ǵ�����Ͷ���г�����������Ժ����������Ѿ���Ϊ��Ҫ�Ĺؼ����ء�����С�������������IJ�Ʒ,ASIC SoC Ҳ���ǺõĽ��������

3.�ɱ��Ƭ��ϵͳ(SOPC)

? �ɱ��Ƭ��ϵͳ(SOPC,System-on-Progammable-Chip)Ϊ����Ӧ���ṩ��һ�������Ľ������:һ���ڿɱ�̡����������õ�оƬ��ʵ�ֵ� SoC������,�ɱ�̵�оƬָ�ľ��� FPGA��FPGA �����������ʹ����Ա�������������������,��ʵ�ֲ�ͬϵͳ�Ĺ���,����Ƕ��ʽ����������ʹ�� ASIC ��ʵ�� SoC���,FPGA �ܹ��ɸ�Ϊ��������ƽ̨,����ϵͳ��������

4.ȫ�ɱ����ϵͳ(APSoC)

? **ȫ�ɱ����ϵͳ(APSoC,All-Programmable SoC)**���������������ɱ������ FPGA ��Ӳ���ɱ���Խ�����������,���ṩ�����ױȵ�ϵͳ���ܡ�����������չ�ԡ�ZYNQ ����������Ҫ������ɵ�:һ����˫�� ARM Cortex-A9 Ϊ���Ĺ��ɵĴ���ϵͳ(PS Processing System),��һ���ȼ���һƬ FPGA �Ŀɱ����(PL,Programmable Logic)���֡�ZYNQ �ܹ��ļ�ģ������ͼ��ʾ:

? ����ͼ��,PS ���й̶��ļܹ�,�����˴�������ϵͳ�Ĵ洢��;�� PL ��ȫ������,���������һ�顰�հ��������������Ƶ����衣�� ZYNQ ��,ARM Cortex-A9 ��һ��Ӧ�ü��Ĵ�����,�������� Linux �����IJ���ϵͳ,���ɱ�����ǻ��� Xilinx 7 ϵ�е� FPGA �ܹ���ZYNQ �ܹ�ʵ���˹�ҵ���� AXI �ӿ�,��оƬ����������֮��ʵ���˸ߴ��������ӳٵ����ӡ�����ζ�Ŵ������������ָ��Զ����Է�����ѵ���;,�����������������������֮��Ľӿڿ��������ͬʱ,���ܻ��ϵͳ����Ϊ��һоƬ�������ĺô�,���������ߴ������ɱ��Ľ��͡�

(3)PL���

1.�������������ּ��ɵ�·�����ܶ��ǹ̶�����ġ�Ҫ��ı�����������,�ͱ���ı��ڲ�����Ԫ��·֮�������,�����������ڼ��ɵ�·�����������Ѿ��̶������ˡ�

2.�����û��������ڲ����ӵļ��ɵ�·:�ɱ��������(Programmable Logic Device)�C����ZYNQ��FPGA����

1��PLD�ڲ��ĵ�·�ṹ����ͨ��д��������������;

2��д��PLD�ı�����ݻ����Բ�����д;

PLD�������ܿ�����ʹ����ͨ��������趨��

3.���õĿɱ��������:

CPLD:���ӿɱ��������(Complex Programmable Logic Device)

FPGA:�ֳ��ɱ��������(Field Programmable Gate Array)

���ʲ���:��·�ṹ��ͬ��

CPLD:���ڡ��˻�������������

FPGA:���ڡ����ұ���(LUT,Look UP Table)��CLB����

�� FPGA �����ṹ�� 6 �������,�ֱ�Ϊ�ɱ������/�����Ԫ�������ɱ������Ԫ��Ƕ��ʽ��RAM���ḻ�IJ�����Դ���ײ�Ƕ�빦�ܵ�Ԫ����Ƕר��Ӳ�˵�,����ͼ��ʾ:

PL�Ľӿڲ��ֻ�����FPGA�IJ���,����������

(4)PS���

ZYNQ ʵ������һ���Դ�����Ϊ���ĵ�ϵͳ,PL ֻ������һ�����衣Zynq-7000 ϵ�е����������������������� ARM ������ϵͳ,�Ҵ�����ϵͳ�м������ڴ�������ʹ���������,ʹ Cortex-A9 ������������ȫ�����ڿɱ������Ԫ������ʵ������ ZYNQ ��,PL �� PS �����ֵĹ����·�Ƕ�����,���� PS �� PL ���ֲ���ʹ�õĻ��Ϳ��Ա��ϵ硣

FPGA ���������Ƕ��ʽ������,�� Xilinx �� MicroBlaze ���������� Altera �� Nios II ��������������ʹ�� FPGA �Ŀɱ������Դ��Ĵ��������dz�֮Ϊ�����ˡ�������,�����������ڴ������������Լ�ʵ�ַ�ʽ������ԡ��� ZYNQ �м��ɵ���һ�š�Ӳ�ˡ�������,���ǹ�оƬ��ר���Ҿ����Ż���Ӳ����·,Ӳ�˴������������������Ի����Խϸߵ����ܡ�����,ZYNQ �е�Ӳ�������������˴�����������ͻ,������ȫ����ʹ�� PL ������Դ�һ�� Microblaze ���˴�����,���� ARM Ӳ�˴�����Эͬ��������Ҫע�����,Zynq ������ϵͳ�ﲢ��ֻ�� ARM ������,����һ����صĴ�����Դ,�γ���һ��Ӧ�ô�������Ԫ(Application Processing Unit,APU),�������չ����ӿڡ�cache �洢�����洢���ӿڡ������ӿں�ʱ�ӷ�����·�ȡ�

ZYNQ ������ϵͳ(PS)ʾ��ͼ������ʾ,���к�ɫ��������Ϊ APU��

1.APU

? ����ͼ��ʾ�� APU �ļ�ͼ��APU ��Ҫ�������� ARM ����������ɵ�,ÿ����������һЩ�ɼ���ĵ�Ԫ:һ�� NEONTM ý�崦������(Media Processing Engine,MPE)���㵥Ԫ(Floating Point Unit,FPU);һ���ڴ������Ԫ(Memory Management Unit,MMU);��һ��һ�� cache �洢��(��Ϊָ���������������)��APU �ﻹ��һ������ cache �洢��,�����»���Ƭ�ϴ洢��(On Chip Memory,OCM),��Щ������ ARM ���������õġ����,��һ��һ���Կ��Ƶ�Ԫ(Snoop Control Unit,SCU)�� ARM �˺Ͷ��� cache �� OCM �洢��֮���γ��������ӡ�SCU �����ָ����� PL �Խ�,ͼ��û�б������ӿڡ�

2).�ⲿ�ӿ�

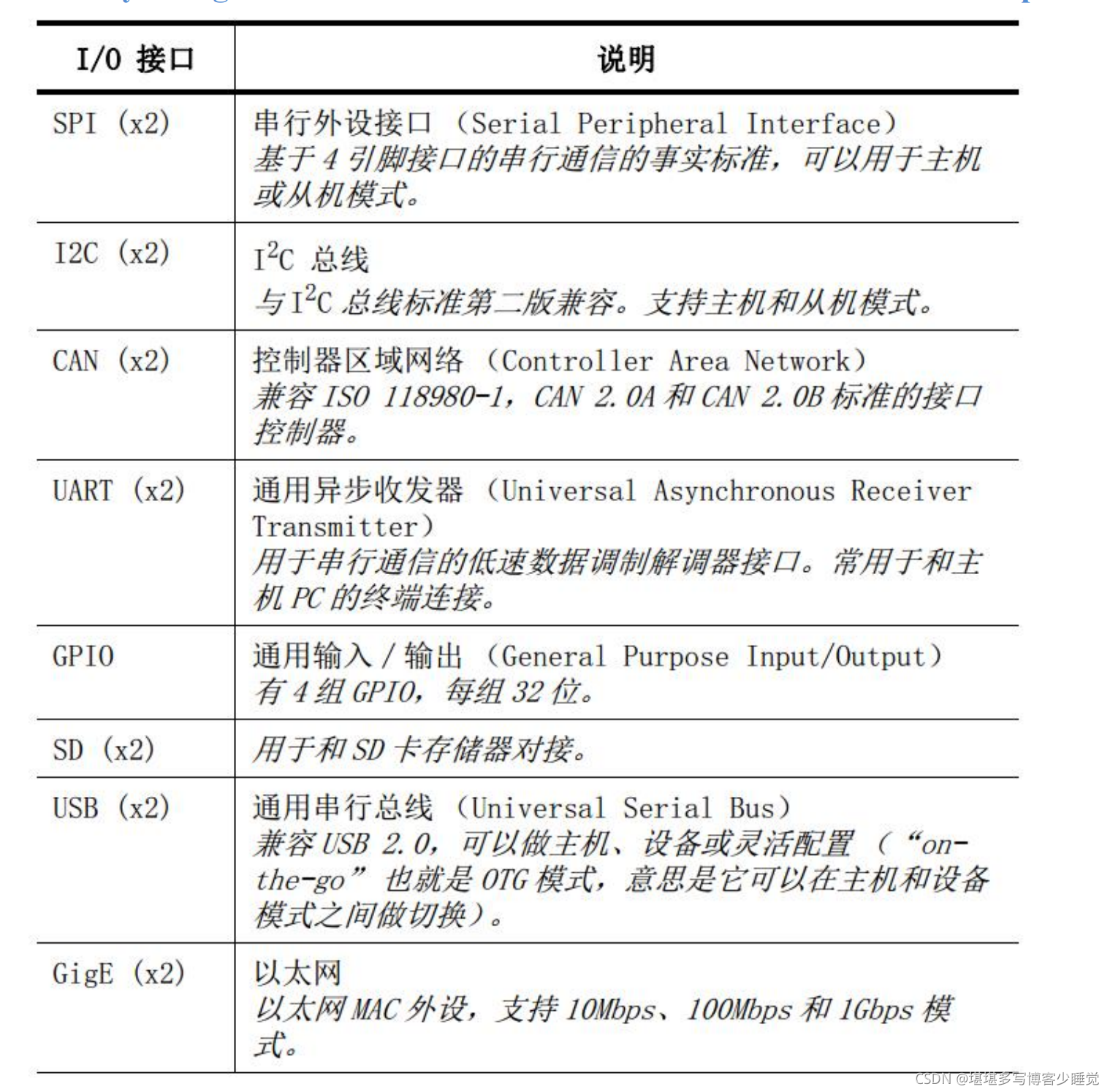

? ��ͼ 1.4.1 ��ʾ,Zynq PS ʵ�����ڶ�ӿ�,���� PS �� PL ֮���,Ҳ�� PS ���ⲿ����֮��ġ�PS ���ⲿ�ӿ�֮���ͨ����Ҫ��ͨ�����õ�����/���(Multiplexed Input/Output,MIO)ʵ�ֵ�,���ṩ�˿���������õ� 54 ������,������ⲿ�豸������֮���ӳ���ǿ����趨��ġ�����Ҫ��չ���� 54 �����ŵ�ʱ�����ͨ����չ MIO(Extended MIO,EMIO)��ʵ��,EMIO ������ PS ���ⲿ����֮���ֱ��ͨ·,����ͨ�������� PL �� I/O ��Դ��ʵ�ֵġ�PS �п��õ� I/O ������ͨ�Žӿں�ͨ������/���(General Purpose Input/Output,GPIO),GPIO ��������������;,�����İ�ť�����غ� LED������ͼ��ʾ:

3.�洢���ӿ�

? Zynq-7000 APSoC �ϵĴ洢���ӿڵ�Ԫ����һ����̬�洢���������ͼ�����̬�洢���ӿ�ģ�顣��̬�洢���������������� DDR3��DDR3L��DDR2 �� LPDDR2����̬�洢��������֧��һ�� NAND ����ӿڡ�һ�� Quad-SPI ����ӿڡ�һ�������������ߺͲ��� NOR ����ӿڡ�

4. Ƭ�ϴ洢��

? Ƭ�ϴ洢������ 256kB �� RAM(OCM)�� 128kB �� ROM(BootROM)��OCM ֧������ 64 λ AXI �ӻ��ӿڶ˿�,һ���˿�ר����ͨ�� APU SCU �� CPU/ACP ����,����һ������ PS �� PL ���������е����������������ġ�BootROM �� ZYNQ оƬ�ϵ�һ�����ʧ�Դ洢��,�������� ZYNQ ��֧�ֵ�����������������BootROM �����û��Dz��ɼ���,ר�ű�����ֻ���������Ĺ��̡�

5.AXI �ӿ�

? ZYNQ �������� ARM Cotex-A ϵ�д������������ FPGA �ڵ�оƬ�ڽ��ܽ��,Ϊ��ƴ��������С������ġ�������Ʒ���,�����������Ե�����ŵ㡣�ڽ���ͬ���������Ĵ������� FPGA �ں���һ��оƬ��֮��,Ƭ�ڴ������� FPGA ֮��Ļ���ͨ·�ͳ��� ZYNQ оƬ��Ƶ�����֮�ء���� Cotex-A9 ��FPGA ֮������ݽ�����Ϊƿ��,��ô�������� FPGA ��ϵ��������ƾͲ��ܷ��ӳ�����Xilinx �� Spartan-6 �� Virtex-6 ϵ�п�ʼʹ�� AXI Э�������� IP �ˡ��� 7 ϵ�к� ZYNQ-7000 AP SoC ������,Xilinx �� IP ���м���ʹ�� AXI Э�顣AXI ��Ӣ��ȫ���� Advanced eXtensible Interface,��������չ�ӿ�,���� ARM ��˾������� AMBA(Advanced Microcontroller Bus Architecture)Э���һ���֡�AXI Э����һ�ָ����ܡ��ߴ��������ӳٵ�Ƭ������