时钟配置

时钟树

一般使用外设高速时钟HSE,经过锁相环PLL产生最大72MHz的系统时钟:

?然后,各路外设从系统时钟分频。

可以将系统时钟输出。

时钟流

使用STM32Cube配置的结果:

?时钟配置结果

在KEIL-MDK中看到的结果:

?

GPIO配置

GPIO原理框图

GPIO输入工作原理框图

?说明:

- 此时输出控制回路是断开的。

- 输入信号可以配置为上拉或者下拉。

GPIO输入功能配置项

| 配置项 | 配置内容 | 相关寄存器名称 | 寄存器说明 |

| 端口时钟 | 使能 | 外设时钟使能 RCC_APB2ENR | |

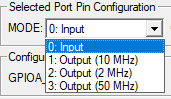

| 端口模式 | 输入模式 | 端口x的模式 GPIOx_CR.MODEy | 00=输入模式 01=中速输出模式(10MHz) 10=低速输出模式(2MHz) 11=高速输出模式(50MHz) |

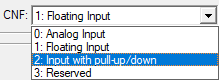

| 端口配置 | 上下拉输入模式 | 端口x的配置位 GPIOx_CR.CNFy | 00=模拟输入模式 01=浮空输入模式 10=上拉/下拉输入模式 11=保留 |

| 端口上下拉 | 上拉或者下拉 | 端口输出数据寄存器 GPIOx_ODR | 0=下拉 1=上位 |

| GPIO锁定 | 配置完成后锁定 | 端口配置锁定寄存器 GPIOx_LCKR |

GPIO输出工作原理框图

?说明:

- 用作输出时,输入回路无需断开,可以读取当前的输出状态。

- 输出控制可以配置为推挽或者开漏。

GPIO输出功能配置项

| 配置项 | 配置内容 | 相关寄存器名称 | 寄存器说明 |

| 端口时钟 | 使能 | 外设时钟使能 RCC_APB2ENR | |

| 端口模式 | 输出模式 | 端口x的模式 GPIOx_CR.MODEy | 00=输入模式 01=中速输出模式(10MHz) 10=低速输出模式(2MHz) 11=高速输出模式(50MHz) |

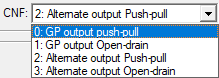

| 端口配置 | 上下拉输入模式 | 端口x的配置位 GPIOx_CR.CNFy | 00=通用推挽输出模式 01=通用开漏输出模式 10=复用功能推挽输出模式 11=复用功能开漏输出模式 |

| GPIO锁定 | 配置完成后锁定 | 端口配置锁定寄存器 GPIOx_LCKR | |

| 端口控制 | 高电平或者低电平 | 端口输出数据寄存器 GPIOx_ODR | 0=输出低 1=输出高 |

调试过程

可以查看输入状态和输出状态:

| 项目 | 相关寄存器名称 |

| 输入状态 | 端口输入数据寄存器GPIOx_IDR |

| 输出状态 | 端口输出数据寄存器GPIOx_ODR |

端口模式选择:

?作为输入时的配置:

?作为输出时的配置:

?

外设的GPIO配置

定时器TIM1/TIM8

?USART

?

?SPI

??

I2C

?

BxCAN

?

ADC端口配置

ADC输入引脚必须配置为模拟输入。

?

?

外部中断输入?

外部中断配置

外部中断原理框图

?

外部中断功能配置项

| 配置项 | 配置内容 | 相关寄存器名称 | 寄存器说明 |

| 端口时钟 | 使能 | 外设时钟使能 RCC_APB2ENR | |

| AFIO时钟 | 使能 | 外设时钟使能 RCC_APB2ENR | bit0:AFIOEN |

| GPIO口配置 | 输入模式 | 参见6.2节 | |

| 中断线映射 | 将GPIO口与中断线映射起来 | 外部中断配置寄存器 AFIO_EXTICR | 0000=PA[x] 0001=PB[x] …… |

| 中断配置 | 上升沿触发、下降沿触发、中断屏蔽 | 中断屏蔽EXTI_IMR 上升沿触发选择EXTI_RTSR 下降沿触发选择EXTI_FTSR | |

| NVIC中断优先级 | 抢占优先级、子优先级 | NVIC->IP NVIC->ISER |

调试过程

可以查看:

| 项目 | 内容 | 相关寄存器名称 | 寄存器说明 |

| 中断挂起状态 | 是否有中断发生 | EXTI_PR | 0=没有发生触发请求 1=发生了触发请求 |

PWM输出配置

通过定时器原理框图

?PWM输出原理

?

?

捕获/比较通道的输出部分

死区设置

?可以使用高级定时器中自带的互补输出和死区插入功能:

?

PWM输出配置项

| 配置项 | 配置内容 | 相关寄存器名称 | 寄存器说明 |

| 外设时钟 | 使能 | 外设时钟使能 RCC_APB1ENR RCC_APB2ENR | 使能定时器外设时钟 使能端口外设时钟 |

| 端口配置 | 输出模式 | 参见6.3节 | 输出口配置为:复用推挽输出 |

| 时钟源 | 选择时钟源 | 使用内部时钟 | |

| 分频器 | 预分频器 | 预分频器TIMx_PSC | 计数器的时钟频率CK_CNT等于f CK_PSC /(PSC[15:0]+1)。 |

| 计数模式 | 向上计数/向下计数/中央对齐计数 | 控制寄存器 TIMx_CR1.CMS | 00=边沿对齐模式(DIR决定向上或向下计数) 01/10/11=中央对齐模式 |

| 计数方向 | 向上/向下计数 | 控制寄存器 TIMx_CR1.DIR | 边沿对齐模式下: 0=向上计数 1=向下计数 中央对齐模式下:硬件控制 |

| 计数周期 | 计数上限 | 自动重装载寄存器 TIMx_ARR | |

| 计数器控制 | 使能 | 控制寄存器 TIMx_CR1.CEN | 0=关闭计数器 1=使能计数器 |

| 工作模式选择 | 比较输出模式 | 捕获/比较模式寄存器 TIMx_CCMR1.CC1S | 00=通道配置为输出 01/10/11=通道配置为输入 |

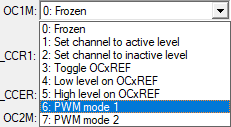

| 输出比较模式 | PWM模式 | 捕获/比较模式寄存器 TIMx_CCMR1.OC1M | 000=冻结 …… 110=PWM模式1:CNT<CCR时为有效电平 111=PWM模式2:CNT<CCR时为无效电平 |

| PWM脉宽 | 输出比较值 | 捕获/比较寄存器 TIMx_CCRy | 当前捕获/比较寄存器参与同计数器TIMx_CNT的比较,并在OCy端口上产生输出信号。 |

| 输出极性 | 有效电平 | 捕获/比较使能寄存器 TIMx_CCER.CCyP | 0=OCy高电平有效 1=OCy低电平有效 |

| 输出使能 | 使能 | 捕获/比较使能寄存器 TIMx_CCER.CCyE | 0=关闭,OCy禁止输出 1=开启,OCy信号输出到对应的输出引脚 |

标准OCx通道的输出控制位:

?连接到标准 OCx 通道的外部 I/O 引脚状态,取决于 OCx 通道状态和 GPIO 以及 AFIO 寄存器。

调试过程

捕获/比较寄存器:

?

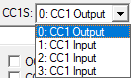

捕获/比较选择:

?

输出比较模式:

?

基本定时器配置

原理框图

?基本定时器配置项

| 配置项 | 配置内容 | 相关寄存器名称 | 寄存器说明 |

| 外设时钟 | 使能 | 外设时钟使能 RCC_APB1ENR | bit4=TIM6EN |

| 时钟源 | 选择时钟源 | 基本定时器只能使用内部时钟 | |

| 分频器 | 预分频器 | 预分频器TIMx_PSC | 计数器的时钟频率CK_CNT等于f CK_PSC /(PSC[15:0]+1)。 |

| 计数周期 | 计数上限 | 自动重装载寄存器 TIMx_ARR | |

| 计数器控制 | 使能 | 控制寄存器 TIMx_CR1.CEN | 0=关闭计数器 1=使能计数器 |

| 定时器中断 | 使能 | DMA/中断使能寄存器 TIMx_DIER.UIE | 0=禁止更新中断 1=使能更新中断 |

| NVIC中断 | 使能及优先级 |

调试过程

可查看:

| 项目 | 内容 | 相关寄存器名称 | 寄存器说明 |

| 计数值 | 定时器计数器 | TIMx_CNT | |

| 状态 | 更新中断标志(Update interrupt flag) | TIMx_SR.UIF | 计数器产生上溢或者下溢 |

ADC转换配置

ADC原理框图

?ADC转换配置项

| 配置项 | 配置内容 | 相关寄存器名称 | 寄存器说明 |

| 外设时钟 | 使能 | 外设时钟使能 RCC_APB2ENR | 使能ADC外设时钟 使能端口外设时钟 |

| 端口配置 | 输入模式 | 参见6.2节 | 输入口配置为:模拟输入 |

| 时钟分频 | ADC分频系数 | 时钟配置寄存器 RCC_CFGR.ADCPRE | ADC时钟最大14M 使用6分频,工作频率为12M |

| ADC复位 | 通过时钟复位 | 外设时钟使能 RCC_APB2ENR.ADC1EN | 先使能再禁止 |

| 初始化 | 独立工作模式,转换通道,触发源,数据对齐方式 | ADC控制寄存器 1 ADC_CR1 ADC控制寄存器2 ADC_CR2 | |

| ADC控制 | 使能 | ADC控制寄存器2 ADC_CR2.ADON | 0:关闭ADC转换/校准,并进入断电模式; 1:开启ADC并启动转换。 注:如果在这个寄存器中与ADON一起还有其他位被改变,则转换不被触发。这是为了防止触发错误的转换。 |

| 校准 | 先复位校准, 再开启校准 | ADC控制寄存器2 ADC_CR2. RSTCAL ADC_CR2. CAL | 软件置1,硬件清0. |

调试过程

可查看:

| 项目 | 内容 | 相关寄存器名称 | 寄存器说明 |

| 转换动作 | 转换动作是否完成 | ADC状态寄存器 ADC_SR | STRT:规则通道开始 JSTRT:注入通道开始 JEOC:注入通道转换结束 EOC: (规则或注入通道)转换结束 AWD:模拟看门狗标志 |

| 转换结果 | ADC转换后的码值 | ADC规则数据寄存器ADC_DR ADC注入数据寄存器ADC_JDR |

配置寄存器项目:

?

ADC转换触发源

可以是外部触发,也可以是软件触发。

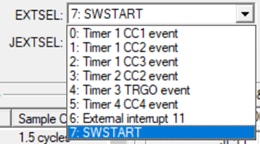

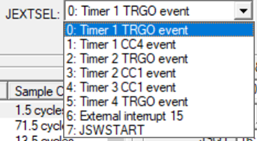

ADC1的规则组触发源:ADC 控制寄存器 2,选择启动规则通道组转换的外部事件(ADC_CR2.EXTSEL)

?

选择触发源后,触发源是否要激活,则由 ADC 控制寄存器ADC_CR2 的 EXTTRIG 和 JEXTTRIG 这两位来激活。

如果是选择软件触发,则写入ADC_CR2寄存器中的SWSTART及JSWSTART位开启转换。由软件设置该位以启动转换,转换开始后硬件马上清除此位。

?

ADC转换时间

ADC使用若干个ADC_CLK周期对输入电压采样,采样周期数目可以通过ADC_SMPR1和ADC_SMPR2寄存器中的SMP[2:0]位更改。每个通道可以分别用不同的时间采样。

总转换时间如下计算:

T conv = 采样时间+ 12.5个周期

其中Tconv为ADC总转换时间,当ADC_CLK=14Mhz的时候,并设置1.5个周 期的采样时间,则Tcovn=1.5+12.5=14个周期=1us。

端口重映射

端口重映射列表

?端口重映射配置项

| 配置项 | 配置内容 | 相关寄存器名称 | 寄存器说明 |

| 端口重映射 | 使用非默认端口 | 复用重映射和调试I/O配置寄存器 AFIO_MAPR | 00=没有重映像 01=部分映像 10=部分映像 11=完全映像 或者 0=没有重映像 1=重映像 |

调试端口重映射配置

?

DMA配置

原理框图

?

DMA1通道

DMA2通道

?

DMA功能配置项

| 配置项 | 配置内容 | 相关寄存器名称 | 寄存器说明 |

| 外设时钟 | 使能 | AHB 外设时钟使能寄存器 RCC_AHBENR.DMA1EN | |

| 外设DMA控制 | 使能 | 参见各外设的配置 | |

| 外设基地址 | 地址 | DMA通道x 外设地址寄存器 DMA_CPARx | |

| 存储器基地址 | 地址 | DMA 通道x 存储器地址寄存器 DMA_CMARx | |

| 数据传输方向 | 从外设到存储器 或 从存储器到外设 | DMA 通道x 配置寄存器 DMA_CCRx.DIR | 0=从外设读 1=从存储器读 |

| 传输数量 | 缓冲区大小 | DMA 通道x 传输数量寄存器 DMA_CNDTRx | |

| 外设地址递增 | 外设地址增量模式 | DMA 通道x 配置寄存器 DMA_CCRx.PINC | |

| 存储器地址递增 | 存储器地址增量模式 | DMA 通道x 配置寄存器 DMA_CCRx.MINC | |

| 外设数据宽度 | 8位/16位/32位 | DMA 通道x 配置寄存器 DMA_CCRx.PSIZE | 00:8位 01:16位 10:32位 11:保留 |

| 存储器数据宽度 | 8位/16位/32位 | DMA 通道x 配置寄存器 DMA_CCRx.MSIZE | 同上 |

| 循环模式 | 单次还是循环 | DMA 通道x 配置寄存器 DMA_CCRx.CIRC | 0:不执行循环操作 1:执行循环操作 |

| 通道优先级 | 优先级 | DMA 通道x 配置寄存器 DMA_CCRx.PL | 00=低;01=中; 10=高;11=最高 |

| 存储器到存储器 | 是否存储器到存储器模式 | DMA 通道x 配置寄存器 DMA_CCRx.MEM2MEM | 0:非存储器到存储器模式; 1:启动存储器到存储器模式。 |

| 中断配置 | 传输过半中断、 传输完成中断、 传输错误中断 | DMA 通道x配置寄存器 DMA_CCRx.HTIE/TCIE/TEIE | |

| NVIC中断优先级 | 抢占优先级、子优先级 | NVIC->IP NVIC->ISER | |

| DMA控制 | 使能 |

调试过程

可查看:

| 项目 | 内容 | 相关寄存器名称 | 寄存器说明 |

| 中断挂起状态 | 是否有中断发生 | DMA 中断状态寄存器 DMA_ISR |

片内看门狗配置

独立看门狗原理图

?

独立看门狗配置项

| 配置项 | 配置内容 | 相关寄存器名称 | 寄存器说明 |

| LSI时钟 | 使能 | ||

| 允许访问 | 允许配置 | 键寄存器(IWDG_KR) | 写入0x5555表示允许访问IWDG_PR和IWDG_RLR寄存器 |

| 预分频 | 分频 | 预分频寄存器 (IWDG_PR) | 000=4分频 …… 111=256分频 |

| 计数值 | 重装载的值 | 重装载寄存器 (IWDG_RLR) | 低12位有效。 |

| 重装载 | 把重装载寄存器的值放到计数器中 | 键寄存器(IWDG_KR) | 写入0xAAAA |

| 使能看门狗 | 使能 | 键寄存器(IWDG_KR) | 写入0xCCCC |