вЛЁЂUARTЛљБОИХФю

????????ЭЈгУвьВНЪеЗЂДЋЪфЦї(Universal Asynchronous Receiver/Transmitter),ЭЈГЃГЦзїUARTЁЃЫќНЋвЊДЋЪфЕФзЪСЯдкДЎааЭЈаХгыВЂааЭЈаХжЎМфМгвдзЊЛЛ,ПЩгУгкЕЅЦЌЛњжЎМфЁЂЕЅЦЌЛњгыPCжЎМфЪ§ОнЭЈаХ,вВОЭЪЧЮвУЧГЃЫЕЕФДЎПкЁЃ

ЖўЁЂДЎПкавщ

? ? ? ? етРяЫљЫЕЕФДЎПкавщАДееЮвЕФРэНт,ЪЧеыЖдЁАжЁЁБетИіЕЅЮЛРДЫЕЕФ,ЦфНсЙЙШчЯТЭМЫљЪОЁЃ

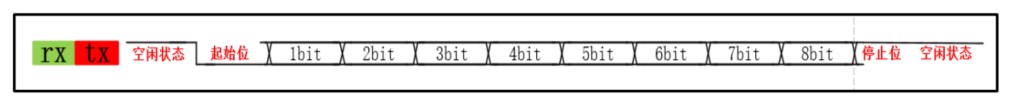

?????????дквЛжЁжа,ЦфЛљБОЕЅЮЛЪЧЁАЮЛЁБ,вВОЭЪЧbitЁЃвЛжЁЪ§ОнАќКЌЦ№ЪМЮЛЁЂЪ§ОнЮЛЁЂаЃбщЮЛ(ПЩгаПЩЮо)КЭЭЃжЙЮЛЁЃвђЮЊДЎПкЭЈаХЪЧвьВНЭЈаХ,УЛгаЭЌВНЪБжгаЕї,ЫљвдЮвУЧдкНгЪеЪ§ОнЪБ,вЊжЊЕРвЛжЁЕФжЁЭЗЪЧДгФФПЊЪМЕФ,ЫљвдашвЊвЛИіЦ№ЪМЮЛ,дкЪ§ОнЯпПеЯазДЬЌЯТ,ЭЈаХЯпЕчЦНЪМжеЮЊИп,ЕБвЛжЁЪ§ОнЗЂРДЪБ,ЦфЦ№ЪМЮЛЮЊЁЎ0ЁЏ,ЫљвдЛсВњЩњвЛИіЯТНЕби,ЮвУЧЭЈЙ§ХаЖЯетИіЯТНЕбиОЭПЩвджЊЕРвЛжЁЪ§ОнЕНРДЁЃ

Ъ§ОнЮЛЮЊ8ЮЛ,вВОЭЪЧвЛИізжНк,ЗЂЫЭЫГађЮЊДгЕЭЮЛЕНИпЮЛвРДЮЗЂЫЭЁЃ

ШЛКѓЪЧаЃбщЮЛ(ПЩгаПЩЮо)ЁЃзюКѓЪЧЭЃжЙЮЛ,ЭЃжЙЮЛНЋжиаТРЛиИпЕчЦН,ШЛКѓДІгкПеЯазДЬЌ,ЕШД§ЯТвЛжЁЪ§ОнЕНРДЁЃ

Ш§ЁЂFPGA&VerilogЪЕеН

????????1ЁЂЫМТЗећРэ

? ? ? ? ? ? ? ? ећИіФЃПщПЩвдЗжЮЊСНВПЗж,НгЪеВПЗжКЭЗЂЫЭВПЗж,ШчЭМЫљЪОЁЃ

?????????ЗжЮЊСНВПЗжКѓ,КѓајЪЙгУСщЛю,УПВПЗжЕФЙІФмгжПЩвдЯИЗжЮЊВЈЬиТЪВњЩњЁЂЗЂЫЭ/НгЪеЪ§ОнЁЂВњЩњБъжОЮЛ(ЗНБуЗТецЗжЮі)ЁЃ

?

????????2ЁЂДњТыБраД

? ? ? ? ? ? ? ? СНИіФЃПщЙІФмКмЯрЫЦ,ЮвУЧЯШаДНгЪеФЃПщЁЃ

????????(1)НгЪеФЃПщ

module uart_rx

#(

?? ?parameter BAT = 'd9600? ? ? ? //ВЈЬиТЪ9600

)

(

?? ?input wire ?? ??? ??? ?clk?? ??? ?,? ? ?//ЪБжг50MHZ

?? ?

?? ?input wire ?? ??? ??? ?rst?? ??? ?,? ? ? //ИДЮЛаХКХ,ЕЭгааЇ

?? ?

?? ?input wire ?? ??? ? ?? ?rx?? ??? ?,? ? ? //НгЪеЖЫ

?? ?

?? ?output reg [9:0]?? ?rx_data,? ? ? //НгЪеЛКДц

?? ??? ??? ??? ?

?? ?output reg ?? ??? ??? ?rx_flag? ? ? ?//НгЪеЭъГЩБъжО

);parameter?? ?BAT_CNT = 'd50_000_000 / BAT;? ? ? ? //ИљОнВЈЬиТЪМЦЫуМЦЪ§жЕ

parameter?? ?IDLE? ? ?= 4'b0001,

?? ??? ??? ??? ?????START? = 4'b0010,

? ? ? ? ? ? ? ? ? ? DATA? ? = 4'b0100,

? ? ? ? ? ? ? ? ? ? STOP? ?= 4'b1000;

?? ??? ??? ??? ?

reg [3:0] ?? ?state,next_state;

reg [3:0] ?? ?rx_cnt;

reg ?? ??? ??? ?bat_flag;

reg [12:0] ??cnt;

reg ?? ??? ??? ?rx_dely1,

? ? ? ? ? ? ? ? ? rx_dely2;//rx_dely1:rxДђвЛХФ

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?rx_dely1 <= 0;

?? ?else

?? ??? ?rx_dely1 <= rx;

?? ??? ?

//rx_dely2:rxДђСНХФ

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?rx_dely2 <= 0;

?? ?else

?? ??? ?rx_dely2 <= rx_dely1;//cnt:ВЈЬиТЪЦЕТЪМЦЪ§

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?cnt <= 0;

?? ?else if(cnt == BAT_CNT-1 || state == IDLE)

?? ??? ?cnt <= 0;

?? ?else

?? ??? ?cnt <= cnt + 1'b1;//bat_flag:ВЈЬиТЪМЦЪ§БъжО

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?bat_flag <= 0;

?? ?else if(cnt == BAT_CNT/2-1'b1)? ? ? ? //дкУПbitжмЦкжаМфЮЛжУВњЩњБъжОаХКХ

?? ??? ?bat_flag <= 1'b1;? ? ? ? ? ? ? ? ? ? ? ? ? ?//ДЫЪБВЩМЏЕФЪ§ОнПЩППадИп

?? ?else

?? ??? ?bat_flag <= 0;//rx_cnt:ЪфШыЪ§ОнМЦЪ§?? ??? ?

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?rx_cnt <= 0;

?? ?else if((rx_cnt == 'd9 && cnt == BAT_CNT/2) || state == IDLE)

?? ??? ?rx_cnt <= 0;

?? ?else if(cnt == BAT_CNT-1'b1)? ? ? ? ? ? ?

?? ??? ?rx_cnt <= rx_cnt + 1'b1;

?? ??? ?

//state:зДЬЌИФБф

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?state <= IDLE;

?? ?else

?? ??? ?state <= next_state;

?? ??? ?

//next_state:ДЮЬЌИФБф

always@(*)

?? ?case(state)

?? ??? ?IDLE ?: next_state <= (~rx_dely1 & rx_dely2)?START:IDLE;

?? ??? ?START : next_state <= DATA;

?? ??? ?DATA ?: next_state <= (rx_cnt == 'd8 && cnt == BAT_CNT-1'b1)?STOP:DATA;

?? ??? ?STOP ?: next_state <= (cnt == BAT_CNT/2)?IDLE:STOP;

?? ??? ?default : next_state <= IDLE;

?? ?endcase

?? ?

//rx,rx_data:ЪфШыЪ§Он

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?rx_data <= 0;

?? ?else if(bat_flag == 1'b1)

?? ??? ?rx_data[rx_cnt] <= rx_dely2;? ? ? ??//БЃДцЦ№ЪМЮЛЁЂЪ§ОнЮЛЁЂЭЃжЙЮЛЙВ10bitЪ§Он

?? ??? ?

//rx_flag:ЪфГіЭъГЩБъжО

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?rx_flag <= 0;

?? ?else if(state == STOP && cnt == BAT_CNT/2)

?? ??? ?rx_flag <= 1'b1;

?? ?else

?? ??? ?rx_flag <= 0;? ? ? ??

?? ??? ?

?? ??? ?

endmodule

????????(2)ЗЂЫЭФЃПщ? ? ? ??

module uart_tx

#(

?? ?parameter BAT = 'd9600

)

(

?? ?input wire ?? ??? ??? ?clk?? ??? ?,

?? ?

?? ?input wire ?? ??? ??? ?rst?? ??? ?,

?? ?

?? ?input wire?? ??? ??? ?rx_flag?? ?,

?? ?

?? ?input wire [9:0] ?? ?rx_data?? ?,

?? ?

?? ?output reg ?? ??? ??? ?tx?? ??? ??? ?,

?? ??? ??? ??? ?

?? ?output reg ?? ??? ??? ?tx_flag

);parameter?? ?BAT_CNT = 'd50_000_000 / BAT;

parameter?? ?IDLE? ? ?= 4'b0001,

? ? ? ? ? ? ? ? ? ? START? = 4'b0010,

? ? ? ? ? ? ? ? ? ? DATA? ? = 4'b0100,

? ? ? ? ? ? ? ? ? ? STOP? ?= 4'b1000;

?? ??? ??? ??? ?

reg [3:0] ?? ?state,next_state;

reg [3:0] ?? ?in_cnt;

reg ?? ??? ??? ?bat_flag;

reg [12:0]? ?cnt;

reg [9:0]? ? ?data;//data:Ъ§ОнЛКДц

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?data <= 0;

?? ?else if(rx_flag == 1'b1)? ? ? ? //НгЪеЕНrxФЃПщЗЂРДЕФНгЪеЭъГЩБъжО

?? ??? ?data <= rx_data;? ? ? ? ? ? ?//НЋЪ§ОнДгЪ§ОнЛКДцЖСГі

?? ?else

?? ??? ?data <= data;

?? ??? ?

//cnt:ВЈЬиТЪЦЕТЪМЦЪ§

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?cnt <= 0;

?? ?else if(cnt == BAT_CNT-1 || state == IDLE)

?? ??? ?cnt <= 0;

?? ?else

?? ??? ?cnt <= cnt + 1'b1;//bat_flag:ВЈЬиТЪМЦЪ§БъжО

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?bat_flag <= 0;

?? ?else if(cnt == BAT_CNT-2)

?? ??? ?bat_flag <= 1'b1;

?? ?else

?? ??? ?bat_flag <= 0;//in_cnt:ЪфГіЪ§ОнМЦЪ§?? ??? ?

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?in_cnt <= 0;

?? ?else if((in_cnt == 'd9 && cnt == BAT_CNT - 1'b1) || state == IDLE)

?? ??? ?in_cnt <= 0;

?? ?else if(bat_flag == 1'b1)

?? ??? ?in_cnt <= in_cnt + 1'b1;

?? ??? ?

//state:зДЬЌИФБф

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?state <= IDLE;

?? ?else

?? ??? ?state <= next_state;

?? ??? ?

//next_state:ДЮЬЌИФБф

always@(*)

?? ?case(state)

?? ??? ?IDLE ?: next_state <= (rx_flag)?START:IDLE;

?? ??? ?START : next_state <= DATA;

?? ??? ?DATA ?: next_state <= (in_cnt == 'd8 && cnt == BAT_CNT-1'b1)?STOP:DATA;

?? ??? ?STOP ?: next_state <= (cnt == BAT_CNT/2)?IDLE:STOP;

?? ??? ?default : next_state <= IDLE;

?? ?endcase

?? ?

//tx,rx_data:ЪфГіЪ§Он

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?tx <= 1'b1;

?? ?else if(state == STOP && cnt == BAT_CNT/2)

?? ??? ?tx <= 1'b1;

?? ?else if(state != IDLE)

?? ??? ?tx <= data[in_cnt];? ? ? ? //ЗЂЫЭЪ§Он,НЋВЩМЏЕНЕФЪ§ОндЗтВЛЖЏЗЕЛи

?? ??? ?

//tx_flag:ЪфГіЭъГЩБъжО

always@(posedge clk or negedge rst)

?? ?if(!rst)

?? ??? ?tx_flag <= 0;

?? ?else if(state == STOP && cnt == BAT_CNT/2)

?? ??? ?tx_flag <= 1'b1;

?? ?else

?? ??? ?tx_flag <= 0;endmodule

?

????????(3)ЖЅВуФЃПщ

module uart

(

?? ?input wire ?? ?clk?? ??? ?,

?? ?

?? ?input wire ?? ?rst?? ??? ?,

?? ?

?? ?input wire ?? ?rx?? ??? ??,

?? ?

?? ?output? ? ? ? ? ?tx? ? ? ? ?,

?? ?

?? ?output? ? ? ? ? ?rx_flag?,? ? ? ? //ЗХЕНЖЫПкРяЪЧЮЊСЫЗНБуЗТец

?? ?

?? ?output? ? ? ? ? ?tx_flag

);wire [9:0] ?? ?rx_data;

uart_rx?

#(9600)

uart_rx_inst

(

?? ?.clk? ? ? ? ?(clk? ? ? ? ?),

?? ?.rst? ? ? ? ?(rst? ? ? ? ? ),

?? ?.rx? ? ? ? ? (rx? ? ? ? ? ?),?? ?

?? ?

?? ?.rx_data??(rx_data?),

?? ?.rx_flag?? (rx_flag?? )

);

?? ??

uart_tx?

#(9600)

uart_tx_inst

(

?? ?.clk? ? ? ? ? ?(clk? ? ? ? ),

?? ?.rst? ? ? ? ? ?(rst? ? ? ? ?),

?? ?.rx_flag? ? (rx_flag??),

?? ?.rx_data?? (rx_data?),

?? ?

?? ?.tx? ? ? ? ? ? (tx? ? ? ? ? ?),

?? ?.tx_flag?? ?(tx_flag???)

);endmodule

????????3ЁЂЗТецЗжЮі

????????(1)БраДTestbenchЮФМўНјааЗТец

`timescale 1ns/1ns

module tb_uart();

reg ?? ?clk;

reg ?? ?rst;

reg ?? ?rx?? ?;wire ?? ?tx;

wire ?? ?rx_flag;

wire ?? ?tx_flag;initial?

?? ?begin

?? ??? ?clk <= 0;

?? ??? ?rst <= 0;

?? ??? ?rx <= 1'b1;

?? ??? ?#20

?? ??? ?rst <= 1;?? ?

?? ?endalways #10 clk <= ~clk;

initial

?? ?begin

?? ??? ?#80

?? ??? ??? ?begin

?? ??? ??? ??? ?rx <= 0;? ? ? ? ? ?//Ц№ЪМЮЛ

?? ??? ??? ??? ?#104166;? ? ? ? //ЖдгІВЈЬиТЪ9600ЕФЕЅbitжмЦкЪБМф

?? ??? ??? ??? ?rx <= 0;

?? ??? ??? ??? ?#104166;

?? ??? ??? ??? ?rx <= 1;

?? ??? ??? ??? ?#104166;

?? ??? ??? ??? ?rx <= 1;

?? ??? ??? ??? ?#104166;

?? ??? ??? ??? ?rx <= 0;

?? ??? ??? ??? ?#104166;

?? ??? ??? ??? ?rx <= 0;

?? ??? ??? ??? ?#104166;

?? ??? ??? ??? ?rx <= 1;

?? ??? ??? ??? ?#104166;

?? ??? ??? ??? ?rx <= 1;

?? ??? ??? ??? ?#104166;

?? ??? ??? ??? ?rx <= 0;

?? ??? ??? ??? ?#104166;

?? ??? ??? ??? ?rx <= 1;? ? ? ? ? ?//ЭЃжЙЮЛ

?? ??? ??? ??? ?#105000;?? ?

?? ??? ??? ?end

?? ?end

uart uart_inst

(

?? ?.clk? ? ? ? ?(clk?? ??? ?),

?? ?.rst? ? ? ? ?(rst?? ??? ?),?? ?

?? ?.rx? ? ? ? ? (rx? ? ? ? ?),

?? ?

?? ?.tx? ? ? ? ? ?(tx? ? ? ? ?),

?? ?.rx_flag?? (rx_flag?),

?? ?.tx_flag?? (tx_flag??)

);endmodule

?

????????(2)ModelsimЗТец

????????ПЩвдПДЕН,ЗТецНсЙћКЭдЄЦкЕФаЇЙћЯрЭЌ,ЪЕбщГЩЙІЁЃ

?ЫФЁЂзмНс

? ? ? ? змЬхРДЫЕ,етИіЯюФПВЛЪЧКмФб,жЛвЊРэЧхГўЦфТпМКЭЪБађ,аДГЬађОЭКмЗНБуСЫ,ЭђБфВЛРыЦфзкЁЃашвЊзЂвтЕФЪЧ,дкНгЪеФЃПщжДааЪБ,НгЪеЕНЭЃжЙЮЛКѓВЛБиЕШД§ЭЃжЙЮЛжмЦкЭъШЋНсЪјОЭПЩвдЭЃжЙНгЪеСЫ,жБНгЗЕЛиПеЯазДЬЌЕШД§ЯТвЛжЁЪ§ОнЕНРД,етбљдкЖрзжНкСЌајЗЂЫЭЪБПЩвдБмУтЪ§ОнвХТЉ,ЖСЕНДэТыЁЃ

? ? ? ? PS:зїепЪЧFPGAГѕбЇеп,ЫЎЦНгаЯо,аДЕФВЛЪЧКмЯъЯИ,НізїЮЊвЛИіМђЕЅЕФзмНс,гаЮЪЬтЕФЕиЗНЛЙЧыДѓМвЖрЖржИГі,аЛаЛ~