1 ����IP��

��vivado PGѧϰ��1 PG168:7 Series FPGAs Transceiversѧϰ�ʼ���4.1 ����IP���������������IP��,����ÿһҳ����ϸ����ѡ��ĺ��塣

��10G 64/66BΪ��,�������ù��̿��Բο�ʦ�ִ��еIJ���xilinx IP������,һ��һ����֤Xilinx Serdes GTX���8.0Gbps��

�����ټ�¼һ��:

1.1 Page1:GT Selection:

GT Type:

�շ�������Ӳ������,��ɶ��ѡɶ��

Shared Logic:

����ѡ����,����QPLL,������,��λ���ȷ���IP ������IJο�����ļ���,�������á�

1.2 Page2:Line Rate,RefClk Selections:

Protocol:

�����Э��ָ����һЩԤ�����Э���IP��Ĭ������,����ɲݰ������ʡ�Э�����8/10b,64/66b�ȡ�����ѡ�հ�ʼStart from scratch����,��������ҲҪ�Լ�����һЩѡ�

Line Rate:

ѡ10G���������з�Χ�ġ�

����Χ:

���ġ�DS182:Kintex�\7 FPGAs Data Sheet: DC and AC Switching Characteristics��

��Ч��Χ:

Vivado Lab Tools

��ѡ�Ļ������Զ���һЩILA��VIO IP��,�������Լ������鷳���Թ�,�����Զ��ӵ�λ�����źŸ������ܲ��Ǻ����⡣�ر��ǻ�Ӻܶ������Ӱ˵�wire,��

PLL Selection

������С�ڵ���6.6Gbps�Ϳ���ѡ��QPLL(Quad PLL)��CPLL(Channel PLL),�����ʴ���6.6Gbps��ֻ��ѡQPLL�ˡ�

TX/RX Reference Clock(MHz)��Use GTX XxYx��TX/RX Clock Source�⼸��ѡ���Ӳ���й�,��Ҫ�ο������ĵ�:

-

PCB��ԭ��ͼ��

-

��UG476:7 Series FPGAs GTX/GTH Transceivers��APPX.A Placement Information by Package�½ڡ�

//--------------------���÷���-------------------begin

- �� ���ĵ���

- �� �ҵ�Ŀ�������ϵ�С�

- �� �ҵ�Ŀ���������

- �� �ҵ�ԭ��ͼ�϶�Ӧ��GTXλ�á������ҵ�ԭ��ͼ�Ϲ�ڵ��źŽӵ���

MGTXT(R)XP(N)0_115,���Ҿ�Ҫѡ�����½�ͼ������GTX_X0Y0,Ȼ��ѡUse GTX X0Y0. - �� �ҵ���ѡ��GTX��Ӧ��Quad�IJο�ʱ�ӡ�����ԭ��ͼ��

MGTREFCLK1P(N)_115����156.25MHz��ʱ������,����TX/RX Reference Clock(MHz)��Ҫѡ156.25MHz,TX/RX Clock Source��ҪѡREFCLK1 Q0(REFCLK11����MGTREFCLK1P(N),Q0���� 115 bank)�������Quadû����Ҫ��ʱ��,Ҳ����ѡ����Quad�IJο�ʱ�ӡ�

//--------------------���÷���-------------------end

1.3 Page3:Encoding and Clocking:

External Data Width(Bits)

�����ⲿ����λ��,Ҳ��������Ҫ���͵����ݵ�λ��,����ѡ32bit��

DRP/System Clock Frequency

�����IP�ⲿһЩ֧��ģ��(QPLL,��λ��)�Ĺ���ʱ��,�������ⲿMMCM��PLL������ʱ�ӻ����ⲿ���������ʱ��,������ֱ���õ��ⲿʱ��,Ƶ��Ϊ25MHz��

Enable T(R)X Buffer

����ʹ�����뻺��������Ȼʱ�ӱȽ��Ѷ��롣����ԭ��������/�������������ԭ��

EnCoding/Decoding

���ñ��뷽ʽ�����м���������ģʽ,����ѡ��64B/66B with Int Seq Ctr 64B/66B����,�ڲ����м���������ģʽ������ԭ�����������м���������ԭ��

Option Ports

���ǹ���8B/10B��һЩ�˿�,����϶�ȫ��ȡ������

Synchronization and Clocking : Option Ports

��ȡ����ȫȡ����,�˿ڡ�

����/�������������ԭ��

//-------------����/�������������ԭ��-----------------begin

TX Buffer

Ϊ����������Buffer������,����ҪѧϰTx��ʱ����

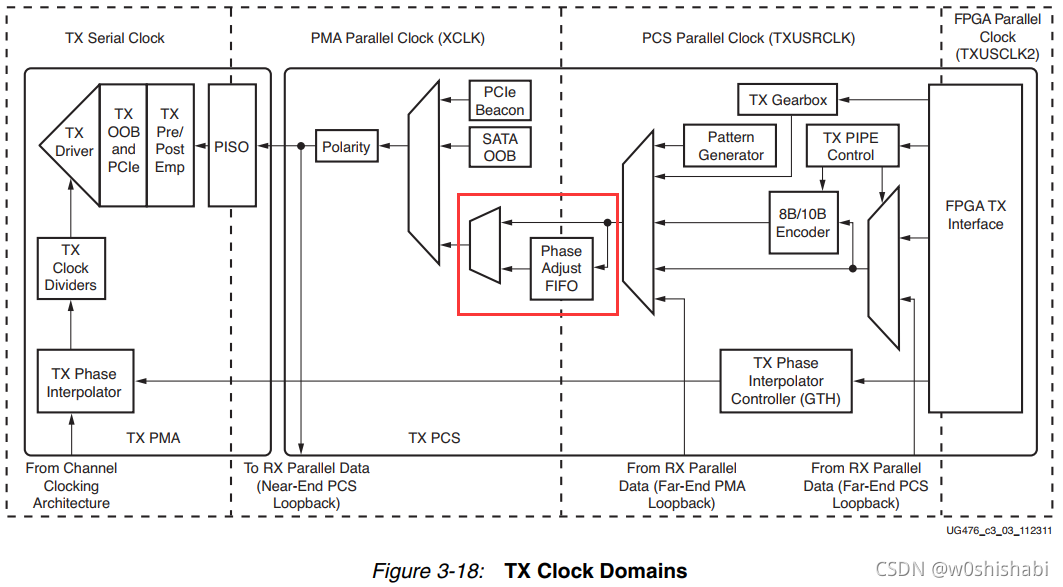

GTX/GTH�շ���TX����·����PCS���������ڲ�����ʱ����:PMA����ʱ����(XCLK)��TXUSRCLK��Ϊ�˴�������,XCLK���ʱ���ƥ��TXUSRCLK����,���ұ�����������֮���������λ�

��GTX/GTH����������TX buffer��TX��λУ����·,�Խ��XCLK��TXUSRCLK��֮�����λ���TX buffer���ƹ�(TX Buffer Bypass)ʱ,ʹ��TX��λУ����·������TX����ͨ·����ʹ��TX buffer��TX��λУ����·������ �� ��λ���� ֮���Ȩ��:

| TX Buffer | TX Phase Alignment | |

|---|---|---|

| ������ | ����ʹ��TX buffer������,���ڲ����� | ��λУ����һ��������,��Ҫ��������Ͷ����ʱ��Դ���ơ�TXOUTCLKSEL����ѡ��GTX/GTH�շ����ο�ʱ����ΪTXOUTCLK����TXUSRCLK��Դ |

| ��ʱ | ������ӳ��ǹؼ�,������ƹ�TX buffer | ��λУ����TX����·����ʹ�ø��ٵļĴ�����ʵ�ָ��͵�ȷ�����ӳ١� |

| TX �����ߵĿ�ƫб | TX��λУ����·�����ڼ��ٶ�����GTX/GTH�շ���֮���ƫб��������ص�GTX/GTH�շ�������ʹ����ͬ����·���ʡ� |

��֮,û�и�ͨ��֮���ͬ�������Ǿͱ�Ϲ��,ʹ��Buffer�������ˡ�

TX Buffer��ʹ��:

��TXBUFSTATUS��ʾoverflow��underflow״̬ʱ,Ӧ������TX buffer��TX buffer����ͨ��ʹ�������źŸ�λ:GTTXRESET, TXPCSRESET,��TXBUF_RESET_ON_RATE_CHANGE = TRUEʱGTX/GTH�շ����ڲ������Ķ����ʱ仯��TX buffer��λ�źš�����GTTXRESET�ᴥ��һ������,����GTX/GTH����������������Щ��������ʹTX buffer���XCLK��TXUSRCLK��֮�����λ��:

- TXBUF_EN = TRUE

- TX_XCLK_SEL = TXOUT

�ƹ�Buffer

����:

�ƹ�TX��������7ϵ��GTX/GTH�շ����ĸ����ܡ�TX��λУ����·���ڵ���PISO����ʱ������TX XCLK��֮�����λ��,�����ݴ�PCS���䵽PISO������ͨ�����ϵ���TXUSRCLK�������¶Ⱥ͵�ѹ�仯��ִ��TX�ӳ�У��������TX��λ���ӳ�У��������GTX�շ����Զ�ִ�л����û��ֶ����ơ�����GTH�շ���,������ܱ������û��ֶ����ơ�

�ƹ�TX Buffer�Ĺ���ģʽ

TX��λУ��������һ��ͨ��(��ͨ��)����һ��TXOUTCLK(��ͨ��)��һ��ͨ����ִ�С�����GTX�շ���,TX Buffer Bypass ֧�� single-lane �Զ�(Auto)ģʽ�� multi-lane �ֶ�( Manual)ģʽ��

| Tx Buffer Bypass | GTX �շ��� | GTH �շ��� |

|---|---|---|

| single-lane | �Զ����ֶ� | �ֶ� |

| multi-lane | �ֶ� | �ֶ� |

��Ϊ���������ﲻչ��˵����������ö˿ں����Կ��Կ���UG476:7 Series FPGAs GTX/GTH Transceivers��

���뻺����������������ơ�

//-------------����/�������������ԭ��-----------------end

�������м���������ԭ��

//-------------�������м���������ԭ��-----------------begin

������64B/66B���뷽ʽΪ��,��64B/66B with Int Seq Ctr �� 64B/66B with Ext Seq Ctr ����ģʽ��

����: ����Tx Gearbox�����ֲ���ģʽ���ⲿ���м�����(Ext Seq Ctr)����ģʽ�������û�����ʵ�����м��������ڶ���ģʽʹ���ڲ����м�����(Int Seq Ctr)��GTH�շ�����֧���ڲ����м�����ģʽ��TX������֧��2�ֽڡ�4�ֽں�8�ֽڽӿڵ�FPGA����

�ⲿ���м���������ģʽ:

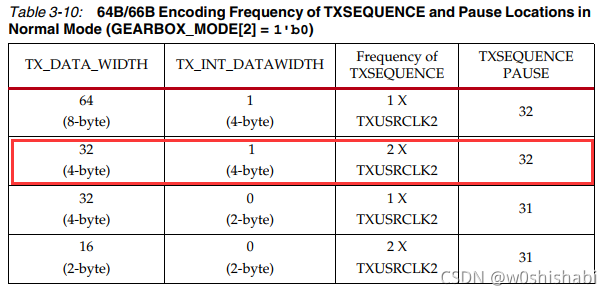

��gearbox��������ģʽ(GEARBOX_MODE[2] = 1��b0)ʱ��ҪTXSEQUENCE [6:0], TXDATA[63:0], �� TXHEADER[2:0] �������롣�û�����Ҫһ�������Ƽ���������IP�˵�TXSEQUENCE�˿ڡ�����64B/66B����,��������0-32ѭ������(ֵ��ע���������ָ����64/66B,���64/67B,����0-66ѭ������)�����Ұ�δʹ�õ�λTXSQUENCE [6] �� TXHEADER [2] ��Ϊ0��**ѭ�������ķ�Χ������λ���ء�**Ȼ��,��ʹ��TX_DATA_WIDTH��TX_INT_DATAWIDTH��ͬ��ģʽ(����,һ��4�ֽڵĽӿ�(TX_DATA_WIDTH = 32)��һ��4�ֽڵ��ڲ����ݿ���(TX_INT_DATAWIDTH= 1)ʱ,����������ÿ����TXUSRCLK2��������һ�Ρ�������Ϊ32λ����λ��ÿ64�����ݵȴ���������,����ÿ����ʱ�����ڼ�һ��

��TX_DATA_WIDTH��TX_INT_DATAWIDTH��ͬ��ģʽ��,ÿ64������������TXUSRCLK2���ڵ�������ͣ,��TX_INT_DATAWIDTH��TX_DATA_WIDTH��������ģʽ��,ÿ64��������һ��TXUSRCLK2���ڵ�������ͣ��

��������ΪTX_DATA_WIDTH = 32,TX_INT_DATAWIDTH = 1(1��),����TXSEQUENCE����Ƶ��Ϊ2*TXUSRCLK2,�ڼ���Ϊ32ʱ��ͣ����(��������Ҳ������)��

������TX_DATA_WIDTH = 64,TX_INT_DATAWIDTH = 1(1��)��ʱ��ͼ,���ǵĹ���ģʽҲ�����Ƶ�,ֻ��������Ƶ��Ϊ����:

�ⲿ���м�������������ģʽ(GEARBOX_MODE[2] = 1��b0)����64/66 ����ʱ(TX_DATA_WIDTH = 32,TX_INT_DATAWIDTH = 1(1��))����������:

- Ӧ�� GTTXRESET Ȼ��ȴ���λ������ɡ�

- �������ڼ�,��TXSEQUENCEӦ��6��h00,�ʵ���ͷ����TXHEADER,��ʼ���ݵ�TXDATA������״̬���������ڵر���,ֱ�����ݴ�����������

- ����0ʱ,���������ݵ�TXDATA,ͷ��Ϣ��TXHEADER������һ��4�ֽڽӿ�(TX_DATA_WIDTH = 32),�����ڶ���4�ֽڵ�TXDATA,��������ȻΪ0��

- ����TXDATA����������ʱ,���м���������Ϊ1��

- Ӧ��8�ֽڵ����ݺ�,���������ӵ�2��TXDATA�ϵ����������ݺ�TXHEADER�ϵ�ͷ��Ϣ��

- ����32ʱ,ֹͣ���ݴ��͡�

�ڲ����м���������ģʽ(ֻ��GTX�շ���֧��):

���������ڲ����м���������ģʽʱ,��ҪTXSTARTSEQ������ TXGEARBOXREADY ������Լ���������ص� TXDATA �� TXHEADER ���롣���ģʽû��TXSEQUENCE,������һ��TXGEARBOXREADY��������ⲿ���м�����ģʽ���ơ�

TXSTARTSEQ����ָʾTX gearbox,����λ�����Ч���ݵĵ�һ���ֽڡ�

���ڸ�λ����֮��Ӧ����Ч���ݵĵ�һ���ֽ�ʱ,TXSTARTSEQ����Ϊ�ߡ�TXDATA��TXHEADER��������ڸ�λ���ȶ�,TXSTARTSEQ���뱣��Ϊ��ֱ�������������롣��λ���֮��ȴ���һ����Ч���ݵ�ʱ��û�й涨,�ɳ��ɶ̡�TXSTARTSEQ����Ч���ݵ�ǰ2��4��8�ֽ�(Ҳ����ָ��ͬλ���ĵ�һ������)����Ϊ��,����֮ǰ�������ߡ������ݵĵ�һ���ֽ�֮��,TXSTARTSEQ����Ϊ����ֵ��

������������(ֱ����Ҫ��ͣ�����ݸ���,32��64��)��,TXGEARBOXREADY������������TXUSRCLK2�����б���Ϊ��,��ȡ����TX_DATA_WIDTH��TX_INT_DATAWIDTH,����TX_DATA_WIDTH��TX_INT_DATAWIDTH��������ģʽ,TXGEARBOXREADY������TXUSRCLK2���ں���Ϊ�͡����ھ�����ͬTX_DATA_WIDTH��TX_INT_DATAWIDTH��ģʽ,��������TXUSRCLK2���ں���Ϊ�͡�

��TXGEARBOXREADY����Ϊ��ʱ,����������һ��TXUSRCLK2����(D_j)������,Ȼ��ͱ���ֹͣ�������롣1�����ӳ��ǹ̶���,���ܸ��ġ�����һ����ʱ����(D_k1)��,���ݱ��뱣�ֵ�TXGEARBOXREADY��Ϊ��(D_k2),Ȼ��Ϳ���������������(D_l)���������ֲ���ģʽ,���ݵ�������ʹ���ⲿ���м�����ģʽΪ64B/67B��64B/66Bʱ��ͬ������Ҫע�����ǵ�ģʽ���������ڵ���ʱ��

GTX �շ��� �ڲ����м���������ģʽ���������:

- ����

TXSTARTSEQΪ�͵�ƽ�� - ʹ��һ��

GTTXRESET��λȻ��ȴ���λ������ɡ� TXGEARBOXREADY�ᱻIP�����ߡ�- �ڸ�λ�ڼ�,���ʵ���ͷ���ݷ���TXHEADER��,��ʼ���ݷ���TXDATA������״̬���������ڵر����Ա����ݴ��䡣

- ����

TXSTARTSEQ,������һ����Ч��ͷ��Ϣ����TXHEADER��,���ݷ���TXDATA�ϡ� - ��������ͷ��Ϣ������,ֱ��

TXGEARBOXREADY��IP�����͡� - ��

TXGEARBOXREADY��Ϊ��ʱ,��������2��4��8�ֽڵ�����(Ҳ�������һ������)�ͱ�ͷ��Ϣ�� - ����

TX_DATA_WIDTH��TX_INT_DATAWIDTH����,���ݱ���һ��������TXUSRCLK2���ڵġ� - ����һ��

TXUSRCLK2������,����TXDATA�ϵ��������롣TXGEARBOXREADY��ǰһ����TXUSRCLK2�����ϱ���Ϊ�ߡ�

//-------------����ϵ�м���������ԭ��-----------------end

1.4 page4: Comma Alignment and Equalization

Comma Detection

һЩ�ж��ָ�����ѡ��,�ָ���Ҳ��Ĭ�ϵ�,����Ĭ�Ͼͺá�

Optional Ports

�����ò���,����ȫ��ȡ����ѡ,�˿ڡ�

RX Equalization

���ý��ն˵ľ���ģʽ����������ѡ��DFEģʽ��ѡ��IJο���LPM��DFEģʽ֮���ѡ��

����ģʽ

//-------------����ģʽ����ԭ��-----------------begin

RX ������(DFE��LPM)

����:

������·������(bit error rate,BER)�����Ƿ�����������ý��ͽ������Ĺ�ϵ����������ý����ŵ����д������Ƶ�,ͨ�������ź��ܵ�˥����ʧ�档

���������͵�����Ӧ�˲�������GTX/GTH������,��ȡ���ڹ��ʺ�����֮���ϵͳˮƽȨ�⡣

GTX/GTH���������е��ĵ�����Ӧģʽ,������ģʽ(low-power mode,LPM)��

Ϊ�˾�����ĸ�����ŵ�,����ʹ��DFEģʽ����ʹ�����Ծ��������,DFEͨ���ṩ���ӽ����˲�����������,���Ը��õز��������ŵ���ġ�Ȼ��,DFE����ɾ������λ��ǰ���( pre-cursor),��ֻ�������α�(post cursor)�����Ծ���������ǰ���ͺ������档GTX/GTH RX DFEģʽ��һ����ɢʱ������Ӧ��ͨ�˲�����DFE��TAPֵ������Ӧ�㷨���õ��˲���ϵ����

����ģʽ:

DFEģʽ:

GTXʹ�õ�ģʽ

-

LPM��DFEģʽ֮���ѡ��

LPMģʽ�Ƽ�������·���ʸߴ�11.2Gb/s���̾���Ӧ��,��С��NyquistƵ�����ŵ����Ϊ12dB����١�

DFEģʽ�Ƽ������г���Ӧ��,�ŵ������ο�˹��Ƶ�����ΪΪ8db���ϡ�DFE�����ڲ��Ŵ������ʹ��ŵ�����¾����ŵ����ŵ㡣DFE�����Ծ���GTX�շ���ǰ5�����α����ŵ�����������ķ��䡣�ڵ�bit��Ӧ������,�����Ǵ��Ż�ʶ����ʱ,DFEģʽ����õ�ѡ��

��8B/10BӦ�ó����ʹ����������(data scrambling)��Ӧ�ó�����,������ϸ����DFEģʽ��Ϊ�˸��õ���Ӧ����,DFEģʽ�µ�����ӦҪ���������������������,��XAUIӦ�ó�����,�û���Ч���������ǷǼ��ܵ�,���Ҳ���8B/10B���롣��Ȼ�û���Ч����ͨ���������,�����ݵ�Ƶ�������ڱ������ܵ����������,����Э����û�ж����ֹ�ظ�pattern���������ݡ���Щ�ظ���pattern�ᵼ������Ӧ�㷨ƫ������ľ������á�������PRBS7(����߶���ʽ)����������ģʽ�����㹻�������,�Ա�������Ӧ�ʵ���ѡ����ȷ�ľ������á�����LPMģʽ�µ�8B/10BӦ�ó���,����Ӧ�����п���ʹ�ô������ҵ��ظ�pattern(����ģʽ)�� -

LPMģʽ��ʹ��

GTX LPM��DFEģʽ���ò�ͬ��CTLEģ�顣����,GTX�շ�����һ������Ư��������·����GTX�շ�����,LPMģʽ�µ�CTLE�ͻ���Ư����������ȫ����Ӧ��,����Ҫ�ֶ����������������á�

ͨ����RXLPMEN�˿�����Ϊ1��b1��ѡ��LPMģʽ�� -

DFEģʽ��ʹ��

DFEģʽ����AGC��CTLE��DFE�ͻ���Ư�Ƶ����������ŵ���Ӱ�졣

ͨ����RXLPMEN�˿�����Ϊ1��b0��ѡ��DFEģʽ��

AGC��DFE�ͻ���Ư������������Ӧ�ġ�����ͨ�������ض����价·��HOLD�˿����������䡣

GTX��GTH�շ���: LPM��DFEģʽ֮�������ʱ�л�

�ڶ�����Ӧ�ó�����,������Ҫ��LPM(�ϵ͵�������)��DFE(�ϸߵ�������)֮������л���Ӧ�ð������²�����LPM��֮������л�:

- ��תRXLPMEN�ĵ���ֵ(RXLPMEN = ~RXLPMEN)��

- ͨ������RXPMARESET���ý�������PMA��

//-------------����ģʽ����ԭ��-----------------end

1.5 page5: PCIe,SATA,PRBS

Optional Ports:

LOOPBACK����ѡһ��,���㻻�ز��Դ���,�����ݲ�ͨʱ,������ѡ��ģʽ���ų���������⡣

����ȫ��ȡ����ѡ��

����ģʽ

//-------------����ģʽ����ԭ��-----------------begin

��������:

����ģʽ���շ�������·������������,������������������Դ��ͨ��,����һ���ض���������ģʽ,Ȼ��Ƚϼ�����ͼ2-26չʾ�����ֲ�ͬ����ģʽ�Ļ��ز������á�

���ز���ģʽ��Ϊ������:

- ����(Near-end )����ģʽ��������������������շ����з������ݡ�������˳�����PMA���غ���ҪGTRXRESET��

- Զ��(Far-end)����ģʽ��·�������ݷ��ص���·��Զ���շ�����

���ز��Կ������ڿ����ڼ����������н��й��ϸ����Ų顣��ʹ�õ�������ģʽ������Ӧ�ó���������ģʽ,Ҳ������ר�ŵ�α����������С�ÿ��GTX/GTH�շ�����һ�����õ�PRBS�������ͼ������

ÿ��GTX/GTH�շ������м�������ģʽ,�Է������:

-

Near-End PCS����

��������RX elastic buffer ,����Ϊ�˽���pcs���ع�������RX_XCLK_SEL��������ΪRXREC�����ڽ���pcs����,RX XCLK����TX PMA����ʱ��(TX XCLK)���������RXOUTCLK����FPGA��ʱ��,��������ʱRXOUTCLKSEL����ΪRXOUTCLKPMA,����GTX/GTH�շ����������PCS����ʱ,���������������һ��:- ����RXOUTCLKSELѡ��RXOUTCLKPCS

- ����RXCDRHOLD = 1��b1

-

Near-End PMA����

��������PMA���غ���ҪGTRXRESET�� -

Far-End PMA����

Far-End��TX buffer��������,Ϊ��PMA���ع�������TX_XCLK_SEL��������ΪTXOUT ������Զ��PMA����,TX buffer��д������RX PMA����ʱ��(RX XCLK)����������ͨ����TXPIPPMEN�˿�����Ϊ1��b0��TXPIPPMSEL�˿�����Ϊ1��b0������TX��λ�ڲ���PPM��������������˳�Far-End PMA ���غ���ҪGTTXRESET�� -

Far-End PCS����

�����ʹ��ʱ��У��,Զ��PCS�����е��շ�������ʹ����Ϊ��������Դ���շ�����ʹ�õ���ͬ�IJο�ʱ�ӡ������Ƿ�ʹ��ʱ��У��,TXUSRCLK�˿ں�RXUSRCLK�˿ڱ�������ͬ��ʱ����Դ(BUFG��BUFR��BUFH)������ gearbox���ջ�ͨ�������õ�ʱ��֧��Զ��PCS���ء�

���÷���:

//-------------����ģʽ����ԭ��-----------------end

1.6 page6: CB and CC Sequence

Clock Correction

�������ǹ�ѡUse Clock Corrrection, Ȼ���������г���Ϊ4�����þ������С�

PPM Offeset +/-����ĺ����Ƿ���ʱ�Ӻͽ���ʱ��֮���PPMƫ�Ĭ�Ͼͺá�

����ʱ��У��

//-------------����ʱ��У������ԭ��-----------------begin

���ȿ���������Ҫģ�鼰ʱ����:

����:

RX elastic buffer����Ƴ���������ͬ��ʱ����RXUSRCLK��XCLK֮�����,��CDR(ʱ�����ݻָ�,RX clock data recovery)�ָ���ʱ�ӡ���ʹ��RXUSRCLK��XCLK����ͬ��ʱ��Ƶ��������,�����к�С��Ƶ�ʲ��ΪXCLK��RXUSRCLK������ȫ��ͬ,���Ƕ�����о���,������ۻ����쵼��RX elastic buffer������������硣Ϊ������У��,ÿ��GTX/GTH�շ���TX���ڷ���һ�����������ַ�,����GTX/GTH�շ���RXɾ��������Щ�����ַ���ͨ����RX elastic buffer����ʱɾ���ַ�,��RX elastic buffer����ʱ�����ַ�,���Է�ֹoverflow�� underflow ��

ʹ��ʱ��У��

-

ʹ��Clock Correction

ÿ��GTX/GTH�շ�������һ��ʱ��У����·,ͨ������RX���Ի�������ָ����ִ��ʱ��У����Ҫʹ��ʱ��У��,RXBUF_EN����ΪTRUE�Դ�RX���Ի�����,CLK_CORRECT_USE����ΪTRUE�Դ�ʱ��У����·��

��RX���Ի����ӳٹ������ʱ����ʱ��У��,ʱ��У����·��ƥ�����С�Ҫʹ��ʱ��У��,��������ʱ��У����·��������Щ��:- RX elastic buffer��Χ��

- Clock correction����

-

����RX elastic buffer��Χ

RX���Ի���������ʹ��CLK_COR_MIN_LAT(��С�ӳ�)��CLK_COR_MAX_LAT(����ӳ�)����RX���Ի������е��ֽ����½���CLK_COR_MIN_LAT����ʱ,ʱ��У����·дһ�������CLK_COR_SEQ_LEN�ֽ�,������ƥ��ĵ�һ��ʱ��У������,�Է�ֹ������underflow�����Ƶ�,��RX���Ի������е��ֽ�������ʱCLK_COR_MAX_LAT,ʱ��У����·����ƥ��ĵ�һ��ʱ��У��������ɾ��CLK_COR_SEQ_LEN�ֽ�,�����еĵ�һ���ֽڿ�ʼ�� 7ϵ��fpga�շ�����ѡ���������CLK_COR_MIN_LAT��CLK_COR_MAX_LAT�����Բ���Ҫ�Լ��衣��ΪCLK_COR_MIN_LAT�������ó�ʼRX���Ի������ӳ�,�����뱻ALIGN_COMMA_WORD��������,�Ա���ͨ�����Ի�������comma���롣CLK_COR_MIN_LAT��ֵ�������RX_INT_DATAWIDTH��ALIGN_COMMA_WORD���������ʾ��

- ����Clock correction����

ʱ��У������ʹ��CLK_COR_SEQ_1_*����(��ӦIP�������еľ�������ֵ)��CLK_COR_SEQ_LEN����(��ӦIP�������е� Sequence length ѡ�� )��ÿ��CLK_COR_SEQ_1_*���Զ�Ӧһ��ʱ��У������1�е������С�CLK_COR_SEQ_LEN��������Ҫƥ������������������ʹ��40λ��20λ���ڲ�����·��,��ʱ��У����·ƥ��ÿ�������е�����10λ�����ʹ��16λ��32λ�ڲ�����·��,��ֻʹ��ÿ�����������ұߵ�8λ��

��ͨ�����ü����ʱ����������CLK_COR_SEQ_2_USEΪTRUE����ӦIP�����õ�Use Two Clock Correction Sequencesѡ���һ���͵ڶ������й����������á���һ�͵ڶ�����ʹ�ò�ͬ��������ֵ����ƥ�䡣����CLK_COR_SEQ_2_*����������ڶ������е�������ֵ��

��ʹ��8B/10B����(RX8B10BENΪ��)ʱ,����CBCC_DATA_SOURCE_SELΪ DECODED ������8B/10B�������������Ѱ������ƥ��,�����Ƿǽ������ݡ���������·Ѱ�Ҿ��������Ӳ��8λֵ,����K�ַ�����ͨ�ַ����ֿ�������CBCC_DATA_SOURCE_SEL����ΪDECODED,�ԡ�RX8B10BEN��Ϊ��High��Ϊ������ʱ�������ֽڵ����á����б����봫���ԭʼ������ȫƥ�䡣��RX_DISPERR_SEQ_MATCH����ΪFALSEʱ,CLK_COR_SEQ_x_y[9]������ƥ�䡣

��������û��8B/10B����,����ע��

һЩЭ��ʹ�ò����������е�ʱ��У�����С�ʱ��У����·�ɱ��ʶ����Щ����ʹ��CLK_COR_SEQ_1_ENABLE CLK_COR_SEQ_2_ENABLE�������е�����λΪLowʱ,����ֵ��ʲô,���ֽڶ�����Ϊƥ�䡣ʱ������������ʱ����������ʹ��λ�Ķ�Ӧ��ϵ��ͼ4-52��ʾ��

ʱ��У��ѡ��

CLK_COR_REPEAT_WAIT���ڿ���ʱ��У��Ƶ��(��ӦIP�������е� Periodicity of CC Sequence(bytes) ѡ��)�����ֵ������Ϊʱ��У���¼�֮���������СRXUSRCLK������������������Ϊ0���������κ�ʱ�����ʱ��У����һЩЭ���������κ�ʱ�����ʱ��У��,��Ҫ�����ʱ��У����·ɾ������,������һ�����б��������С������д�Ҫ���Э��,CLK_COR_KEEP_IDLE����ΪTRUE��

//-------------����ʱ��У������ԭ��-----------------end

1.7 Summary

���,���ǿ���������һ�����öԲ��ԡ�

����TXUSRCLK(2)=312.5MHz,�������õ��ⲿ����λ��Ϊ32λ���ڲ�λ��Ϊ1��,���ڲ�ʱ�� TXUSRCLK = (line Rate) / (internal Data Width) = 10G / 32 = 312.5M�� �ⲿʱ�� TXUSRCLK2 = (line Rate) / (External Data Width) = 10G / 32 = 312.5M������ͬ����

2 ʹ��IP��

2.1 ������

���IP����ҪһЩ�������õ��ⲿ������Դ�Լ��Ƚϸ��ӵĸ�λ��������һ�������̵Ļ����Ͻ��п�����

������:

���̵��ļ��ṹ:

ÿ���ļ��Ĺ��ܼ���vivado PGѧϰ��1 PG168:7 Series FPGAs Transceivers�ٷ����÷���ѧϰ�ʼ���5.3 �� �����ļ��ṹ��

2.2 ʹ������

GTX��λ������Ҫ��һ��ϵͳʱ�ӵ�Լ��:

���Կ��������GTX��λ�úͲο�ʱ�ӽ�����Լ��,����GTX��λ�����Ӧ������ӳ���ϵ,���Բ���Ҫ�ٶ�RXN(P)_IN��TXN(P)_OUT�˿ڽ������Ű�

����Ҫ�ĵľ��Ǹ����Լ����õIJο�ʱ����Դ����DRP_CLK_IN_P(N)��Լ����Ĭ����KC705 demo���Լ���������ҵIJο�ʱ�����ⲿ25MHz��������,���Խӵ�DRP_CLK_IN_P,Ȼ��ʱ�����ڸij�create_clock -name drpclk_in_i -period 40.0 [get_ports DRP_CLK_IN_P] ���С����ѡ�����ⲿMMCM��PLL�����ʱ��,������Ű�ɾ�����ɡ�

�����Է�����˵�����̵�Ӧ�á�

����gtwizard_0_exdesģ����һЩ������Ҫע��һ��:

EXAMPLE_SIM_GTRESET_SPEEDUP: ����Ƿ�����Ϊ��TRUE��,�����ʵ��Ӧ����Ϊ��FALSE����STABLE_CLOCK_PERIOD: ϵͳ�ο�ʱ��,��DRP_CLK_IN_P�����ڡ�

����һ��ע�����Ƿ��͵�����gt0_txdata_iҪ��������ģ��scrambler_0_i��������gt0_scrambled_data_i��

���յ�����gt0_rxdata_iҪ����������ģ��descrambler_0_i�ָ�������gt0_unscrambled_data_i��

��������ץ�źŵ�ʱ��Ҫע����ץһ�½�����������,��Ȼ�����ж������Ƿ�������

2.2.1 ����ʱ��

����ѡ��Ĺ���ģʽ��:64B/66B with Int Seq Ctr,ǰ���Ž��ܹ����ֹ���ģʽ���������롣����������˵������ģ���кܶ�˿�,���Ǵ���һЩ������ƶ˿�,ʵ�ʼ��շ�Ӧ��ʱ,�ص��ע�������г����ļ����źž��С�

������:

- ��λ

�������ǿ��Կ�����������λ�ź�gt0_txfsmresetdone_i �� gt0_txresetdone_i:

- gt0_txfsmresetdone_i : ��Ӧ��λ״̬����ɸ�λ���źš�

- gt0_txresetdone_i : �ײ��GTXE2_CHANNELģ������������ķ������Կ���

gt0_txresetdone_i�Ǹ��˸�λ״̬���ġ�Ӧ�ö�Ӧ���Ǹ�λ״̬���е�TXPMARESET��TXPCSRESET��λ��ɵ��źš�

����Ҳ��Ӧ��ʱ����gt0_txresetdone_i����ɸ�λ,Ȼ��λ״̬��gt0_txfsmresetdone_i����ɸ�λ��

TX��ʼ����λ

//-------------TX��ʼ����λԭ��-----------------begin

��λ��״̬��:

չ��IP��,���Կ���:

����gtwizard_0_init_iģ������tx��λ״̬����ģ������:

gtwizard_0_TX_STARTUP_FSM #

(

.EXAMPLE_SIMULATION (EXAMPLE_SIMULATION),

.STABLE_CLOCK_PERIOD (STABLE_CLOCK_PERIOD), // Period of the stable clock driving this state-machine, unit is [ns]

.RETRY_COUNTER_BITWIDTH (8),

.TX_QPLL_USED ("TRUE"), // the TX and RX Reset FSMs must

.RX_QPLL_USED ("TRUE"), // share these two generic values

.PHASE_ALIGNMENT_MANUAL ("FALSE") // Decision if a manual phase-alignment is necessary or the automatic

// is enough. For single-lane applications the automatic alignment is

// sufficient

)

gt0_txresetfsm_i

(

.STABLE_CLOCK (sysclk_in),

.TXUSERCLK (gt0_txusrclk_in),

.SOFT_RESET (soft_reset_tx_in),

.QPLLREFCLKLOST (gt0_qpllrefclklost_in),

.CPLLREFCLKLOST (tied_to_ground_i),

.QPLLLOCK (gt0_qplllock_in),

.CPLLLOCK (tied_to_vcc_i),

.TXRESETDONE (gt0_txresetdone_i),

.MMCM_LOCK (tied_to_vcc_i),

.GTTXRESET (gt0_gttxreset_t),

.MMCM_RESET (),

.QPLL_RESET (gt0_qpllreset_t),

.CPLL_RESET (),

.TX_FSM_RESET_DONE (gt0_tx_fsm_reset_done_out),

.TXUSERRDY (gt0_txuserrdy_t),

.RUN_PHALIGNMENT (),

.RESET_PHALIGNMENT (),

.PHALIGNMENT_DONE (tied_to_vcc_i),

.RETRY_COUNTER ()

);

//-------------TX��ʼ����λԭ��-----------------end

- ��������

���Կ�����PMA��PCS��λgt0_txresetdone_i��ɺ�, gearbox��ready�ź�gt0_txgearboxready_i���Ѿ�������, �����ʱ���ܸ�����,��Ϊ��λ״̬����û����ɸ�λ��

�ȸ�λ״̬����λgt0_txfsmresetdone_i���, ���ҵ�һ������gt0_scrambled_data_i�Ϳ���λgt0_txheader_r�Ѿ��ȶ���,�Ϳ���gt0_txstartseq_r����,��������еĵ�һ������,��Ϊ�˸�����ʹ��ģ��ʱͬ���õġ�

���Կ���gt0_txstartseq_r���ߵ�204.8ns��,Ҳ����64������֮��,gt0_txgearboxready_i��Ϊ��,��ʱ�ȴ�����ʱ�����ڡ�Ȼ����������ݡ�ʱ��������64B/66B with Int Seq Ctr����ģʽԭ�����ܵ�һ�¡�ÿ64�����ݵȴ�����ʱ�����ڡ�

����Ҫע��Ҫ���͵�����gt0_txdata_iҪ�Ⱦ���һ���������ģ���������gt0_scrambled_data_i��

2.2.2 ����ʱ��

����ʱ��Ƚϼ�

����ע��һ�����gt0_rxheader_i, ���Կ���RX gearbox�Ĺ���������:

���Կ���ÿ���һ������������Header����,����������Ч�ź�gt0_rxdatavalid_iҲ�Ǽ��һλ�ġ����Կ���������������gt0_unscrambled_data_i�뷢�͵�HeaderҲ�Ƕ�Ӧ�ġ�