1. 单片机的片内结构

- 1个8位CPU

- 一个片内振荡器和时钟电路

- 4KB ROM 128B RAM

- 两个16位定时/计数器

- 21个特殊功能寄存器

- 4个并行IO口、一个可编程全双工串行口

- 5个中断源

2. 单片机最小系统

电源、时钟、复位电路

复位分为上电复位和按键复位

单片机的复位引脚RST是高电平有效,当上电的瞬间,由于电容的电压不能产生突变,故RST引脚为高电平,单片机复位,随着电容不断充电,RST引脚的电平值逐渐降低。当按下按键,电容被短路,RST同样为高电平,单片机复位。

复位后:

PC-0000H

SP-07H

P口-FFH(当P口在工作时必须先写入1,在复位后,P口的每一端线为1,为用作输入做了准备,也正因如此,P口用作输出,宜用低电平驱动,以免在复位时造成误操作)

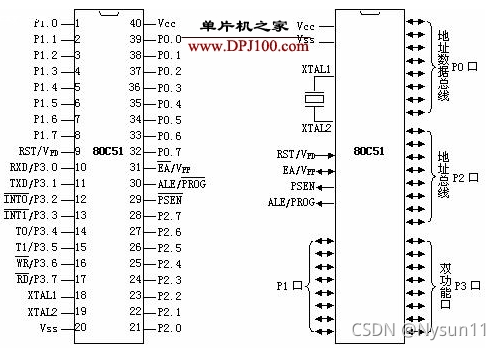

3. 单片机引脚功能

- 电源

40-VCC 20-VSS - 时钟

XTAL1 、XTAL2 - 控制线

EA: 内外ROM选择 当EA=1 时先访问内在访问外 EA=0时 只访问外

PSEN:外ROM读选通信号

ALE:地址允许锁存端

RST:复位 - I/O

P0口为三态,分时传送低8位地址信号和8位数据信号

P1口为用户使用

P2口传送高8位地址

P3口具有第二功能 3.0-RXD 3.1-TXD 3.2-INT0 3.3-INT1 3.4-T0 3.5-T1 3.6-WR(外RAM写选通信号) 3.7-RD(外RAM读选通信号)

==Tips:==用作输入时必须先写1(根据P口结构,其内部有两个场效应管,在输入时,必须保证其中的一个场效应管截止,否则单片机将读不到输入的信号)在用作输出时,必须将P0口外接上拉电阻。

4. 单片机存储空间(哈弗结构)

- 64KB ROM(程序存储器)

- 片内4KB

- 片外60KB

- 64KB 外RAM(数据存储器)

- 256B 内RAM

- 低128B内RAM

- 高128B特殊功能寄存器

ROM空间用MOVC指令实现只读功能操作,由PSEN信号选通读外ROM

外RAM空间用MOVX指令实现读写功能 由WR\RD 选通

内RAM(包括特殊功能寄存器)用MOV指令实现读写

4.1 内RAM

广义上内RAM 256B 分为低128B内RAM 和高128B 为21个特殊功能寄存器

128B内RAM 中:

- 00H-1FH 为工作寄存器区分为0123四个区

- 20H-2FH 为位寻址区

- 30H-7FH 为数据缓冲区

21个特殊功能寄存器:

- 累加器ACC

- 寄存器B

- 程序状态字寄存器PSW(用来存放当前指令的状态和有关标志)

- 四个io口 P0 P1 P2 P3

- 数据指针 DPTR(DPH DPL) 16位 存放一个16位的地址,作为访问外RAMROM的地址指针

- 串行数据缓冲器 SBUF

- 串行控制寄存器SCON

- 中断优先级控制寄存器 IP

- 中断允许控制寄存器 IE

- 定时/计数器控制寄存器 TCON

- 定时/计数器方式选择 TMOD TH0 TL0 TH1 TL1

- 堆栈SP

- 电源控制和波特率选择寄存器 PCON

4.2. 读外RAM 过程

首先CPU从程序寄存器PC 取出当前ROM的地址,由P0口和P2口输出,当ALE信号有效时,由地址锁存器锁存低8位地址,与P2口输出的高8位地址一起组成16位地址加到外ROM地址输入端,当PSEN信号选通时,从ROM中将相应的地址单元中的数据传输到数据总线(P0),由CPU读入后存入指定单元。

4.3 读外RAM过程

外RAM16位地址分别由P0口和P2口输出,当ALE信号有效时,由地址锁存器锁存低8位地址,与P2口输出的高8位地址一起组成16位地址加到外RAM地址输入端,当RD信号有效时,外RAM 将相应存储单元中的数据放置数据总线(P0),由CPU完成读入存入指定单元。

4.4 写外RAM 过程

外RAM 16位地址分别由P0口(低8位)和P2口(高8位)同时输出,当ALE信号有效时,由地址锁存器锁存低8位的地址与P2口的高8位组成16位地址加到外RAM地址输入端,接着CPU将要写入的数据放置P0口,此时P0口充当数据总线的作用,当WR信号有效时,P0口上的数据写入外RAM相应的存储单元中。

5. 时钟周期、机器周期、状态周期、指令周期

- 时钟周期:是80C51单片机内部振荡器产生的时钟脉冲频率的倒数,最小的定时信号。

- 状态周期:是将时钟脉冲二分频后得到的脉冲信号。

- 机器周期:在计算机中,为了便于管理,通常将一条指令的执行分为几个步骤,每个步骤完成一个 工作,例如取指令、存储器读、存储器写,每个工作称为一个基本操作,将完成一个基本操作所用的时间称为机器周期。

- 指令周期:CPU完成一条指令所用的时间,通常用机器周期描述,一般有单机周、双机周和四机周指令,无三机周指令,乘除运算为四机周指令。

6. 中断

6.1 什么是中断

中断是CPU中断正在执行的程序转去执行请求中断的那个外设或事件的服务程序,等待处理完成后继续返回执行原来中止的程序叫中断

6.2 为什么要设置中断?

- 提高CPU工作效率,CPU工作速度快,外设工作速度慢,形成CPU等待,效率降低

- 具有实时处理能力 当某些参数发生变化时,可以通过中断实时处理

- 具有故障处理能力 例如电源断电时,可设置中断保存数据

- 实现分时操作当多外设同时工作时,有的外设有定时需求,此时即可设定定时中断

6.3 中断源(5个)

- INT0 P3.2 0003H

- INT1 P3.3 00BH

- T0 P3.4 0013H

- T1 P3.5 001BH

- 串行中断(串行发送中断TI和串行接受中断RI) 0023H

6.4 中断处理过程

- 中断请求:由中断源向CPU发出中断请求信号

- 中断响应:在满足中断响应条件下(开中断,CPU此时没有响应同级或更高级中断)响应中断,保存断点地址,撤除中断请求标志,关闭同级中断,将中断入口地址存入PC

- 中断执行:保护现场,执行中断服务子程序,完成规定的操作,恢复现场

- 中断返回:恢复断点地址,开放同级中断

6.5 中断控制寄存器

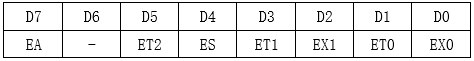

-

IE (中断允许寄存器 )

- EA :总中断允许位;EA=1允许中断

- ET2 :T2中断允许位;ET2=1允许中断

- ES :串行中断允许位;ES=1允许中断

- ET1 :T1中断允许位;ET1=1允许中断

- EX1 :INT1中断允许位;EX1=1允许中断

- ET0 :T0中断允许位;ET0=1允许中断

- EX0 :INT0中断允许位;EX0=1允许中断

-

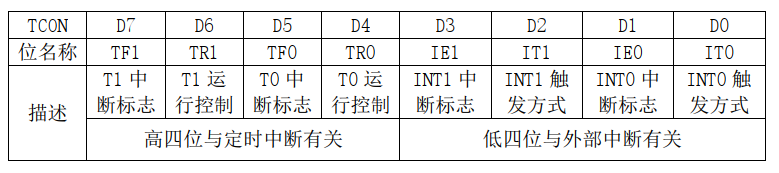

TCON(定时/计数控制寄存器)

- TF1:T1溢出中断请求标志,当定时计数溢出时,由CPU自动置1,TF1=1表示T1有中断产生

- TR1 :TR1=1表示T1开始运行

- TF0 :TF0=1表示T0有中断产生

- TR0 :TR0=1表示T0开始运行

- IE1 :IE1=1表示INT1有中断产生,外部中断1入口P3.3信号有效时置1

- IT1 :IT1=1表示INT1为下降沿触发,IT1=0表示INT1为低电平触发

- IE0 :IE0=1表示INT0中断产生

- IT0 :IT0=1表示INT0为下降沿触发,IT0=0表示INT0为低电平触发

-

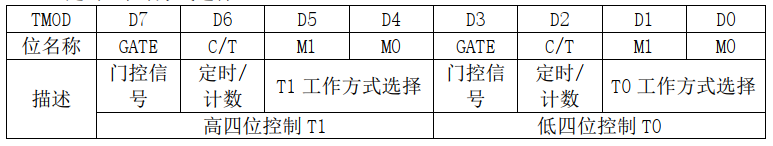

TMOD(定时/计时方式选择)

GATE―门控信号

GATE=1时,定时/计数器的运行同时受TR1、TR0和外部中断的双重控制

GATE=0时,定时/计数器的运行只受TR0、TR1控制

工作方式选择:

| 工作方式 | 描述 |

|---|---|

| 方式0 | 13位 TL0低5位和TH0的8位组成,TL0的低5位计满时不向第六位进位,而是向TH0进位,13位计满溢出。 最大计数值 2^13=8192 |

| 方式1 | 16位 TH08位+TL08位 最大计数值 2^16=65536 |

| 方式2 | 8位 仅用TL0计数 能自动恢复定时/计数初值 |

| 方式3(仅适用于T0,T1无方式3) | T0被拆成两个独立的8位计数器TH0、TL0,其中TH0不能作为计数器 |

C/T :定时/计数模式切换,C/T=0时为定时模式,C/T=1时为计数模式。

7. IIC 通信

二线制(SDA,SCL)串行总线,同步通信,半双工,多主多从

7.1 总线的驱动能力

总线上的扩展的器件数不受制于电流驱动能力,而是受制于电容的负载量,iic总线的电容负载能力为400pf,每一器件的输入端都相当于一个等效电容,由于iic总线扩展方式位并联,所以没扩展一个器件,相当于加上电容,总等效电容相当于每一器件电容之和,等效电容的存在会造成传输信号波形的畸变,超出范围就会出错。

7.2器件寻址方式

IIC根据器件地址字节SLA完成寻址

SLA:4位固有地址编码 + 3位器件引脚地址 + (1位数据传送方向)

3位器件引脚地址用于器件固有地址编码相同时的识别

7.3 iic 的总线基本信号

- 起始信号:SCL处于高电平期间,拉低SDA

- 终止信号:SCL处于高电平期间,拉高SDA

- 应答信号:SCL处于高电平,SDA为低电平

- 应答非信号:SCL处于高电平,SDA为高电平

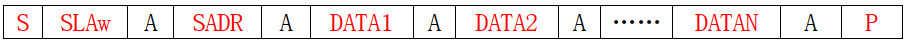

7.4 读写操作格式

写操作

- 主机首先产生启动S信号

- 然后紧跟着发送一个从机地址(SLA),这个地址共有7位,紧接着的第8位是数据方向位(W)

- 主机发送地址时,总线上的每个从机都将这7位地址码与自己的地址进行比较,若相同,则认为自己正在被主机寻址,根据R/T位将自己确定为发送器和接收器

- 这时候主机等待从机的应答信号(A)

- 当主机收到应答信号时,发送要访问从机的那个地址(SADR), 继续等待从机的应答信号(A)

- 当主机收到应答信号时,发送N个字节的数据,继续等待从机的N次应答信号(A)

- 主机产生停止信号(P),结束传送过程

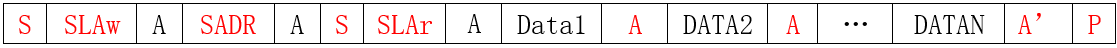

读操作

读之前首先要写入读出的单元子地址

- 主机首先产生启动S信号

- 然后紧跟着发送一个从机地址(SLA),这个地址共有7位,紧接着的第8位是数据方向位(W)

这时候主机等待从机的应答信号(A) - 当主机收到应答信号时,发送要访问的地址(SADR),继续等待从机的应答信号(A)

- 当主机收到应答信号后,主机要改变通信模式,所以主机重新发送一个开始S信号,然后紧跟着发送一个从机地址(SLA),紧接着的第8位是数据方向位(R)

- 这时候主机等待从机的应答信号,当主机收到应答信号时,就可以接收1个字节的数据,当接收完成后,主机发送非应答信号(A’),表示不在接收数据

- 主机产生停止信号(P),结束传送过程

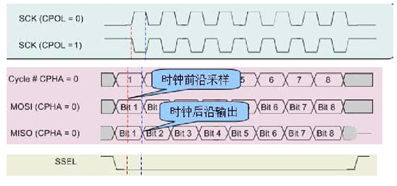

8. SPI通信

同步通信 全双工

MOSI(主机输出从机输入) MISO(主机输入从机输出) SCK(时钟) CS(片选)

模式选择:

- CPOL(时钟极性)

CPOL=1 高电平空闲

CPOL=0 低电平空闲 - CPHA(时钟相位)

CPHA=1 第一个边沿数据输出 第二个边沿数据采样

CPHA=0 第一个边沿数据采样 第二个边沿数据输出

UART IIC SPI 的比较:

9.UART

9.1 串行通信与并行通信

串行通信是数据各位依次逐位发送或接收,并行通信是数据的每位同时发送或接收8位数据并行传输至少需要8条数据线和一条地线,其传输速率快但长距离传输时成本较高串行通信只需要两根数据线,长距离通信时比较经济但速率慢。

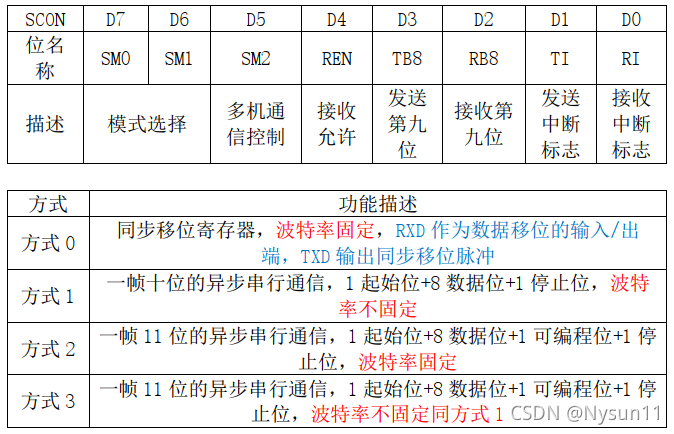

9.2 串行控制寄存器SCON

-

SM2:多机通信控制位,主要用于方式2和方式3

- 若SM2 = 1;则允许多机通信。第9位数据(D8)为1,说明本帧数据为地址帧;若第9位数据为0,则本帧数据为数据帧。当一个89c51(主机)与多个89c51(从机)通信时,所有从机的SM2位都置1,主机首先发送的一帧数据为地址,即某从机号,其中第9位为1,所有的从机接收数据后,将其中第9位数据装入RB8中。各个从机根据接收到的第9位数据(RB8中)的值来决定从机是否再接收主机的信息、若(RB8)= 0,说明是数据帧,则使接收中断标志位RI = 0,信息丢失,若RB8 = 1,说明是地址帧,数据装入SBUF并置RI = 1,中断所有从机,被寻址的目标从机清除SM2,以接收主机发来的一帧数据,其它从机仍然保持SM2 = 1。

- 若SM2 = 0,即不属于多机通信情况,则接收完一帧数据后,不管第9位数据是0还是1,都置RI = 1,接收到的数据装入SBUF中。在方式0时SM2必须置0。在方式1时,若SM2 = 1,则只有接收到有效停止位时,RI才置1,以便接收下一帧数据。

-

REN:允许接收控制位,由软件置1或清0

REN = 1时,允许接收,相当于串行接收的开关

REN = 0时,禁止接收

在串行通信接收控制过程中,如果满足RI = 0和REN = 1的条件,就允许接收。 -

TB8:发送数据的第9位(D8)装入TB8中。在方式2或方式3中,根据发送数据的需求由软件置位或复位。在许多通信协议中可用作奇偶校验位,也可以在多机通信中作为发送地址帧或者数据帧的标志位。

-

RB8:接收数据的第9位,原理同TB8

-

TI:发送中断标志位,在一帧数据发送完时被置位。在串行发送到停止位的开始时由硬件置位,可用软件查询。它同时也申请中断。TI置位意味着向CPU提供“发送缓冲器SBUF已空”的信息,CPU可以准备发送下一帧数据。串行口发送中断被响应后,TI不会自动清0,必须软件清0.

-

RI:接收中断标志,在接收到一帧数据后由硬件置位。当RI = 1时,申请中断,表示一帧数据接收结束,并已装入接收SBUF中,要求CPU取走数据,CPU响应中断,取走数据。RI位也必须由软件来清0。

-

Tips:为何单片机的晶振频率设定为11.0592MHZ?

当串行口工作在方式1/3时,其波特率不确定,需要根据公式计算,当波特率需要按规范取1200,2400,12500……时,若采用12MHZ的晶振,按公式计算出的定时初值不是整数,产生波特率误差从而影响通信性能,故只有改变单片机的晶振频率,通常采用11.0592MHZ

9.3 串行缓冲寄存器SBUF有什么作用?简述串行口接受和发送数据的过程

串行缓冲寄存器逻辑上有两个,分别是串行发送缓冲寄存器和串行接收缓冲寄存器,但在物理上只有一个SBUF且地址都是99H,接收缓冲寄存器还有双缓冲结构,其前有一个移位寄存器,防止接受帧出现重叠错误。在完成串口初始化之后,发送时只需将要发送的数据输入SBUF,CPU将自动启动和完成串行数据发送,接收时,CPU自动将接受到的数据存入SBUF,用户只需从SBUF中取出数据。

9.4 如何判断串行发送和接收一帧完毕?

串行发送一帧完毕,CPU会自动将SCON寄存器中的发送中断标志位TI自动置1,用户通过查询TI的状态即可知道是否发送完毕。