���

Ŀ��

�˽�I.MX6U��Դ��Cortex-A7�ܹ���

�Ķ�����

��Ϥ�������

����˵��

- windows10

�����

- ԭ���ĵ�:I.MX6ULL����ָ�� ������

- NXP�ٷ��ĵ�:I.MX6ULL�ο��ֲᡢ�����ֲ�

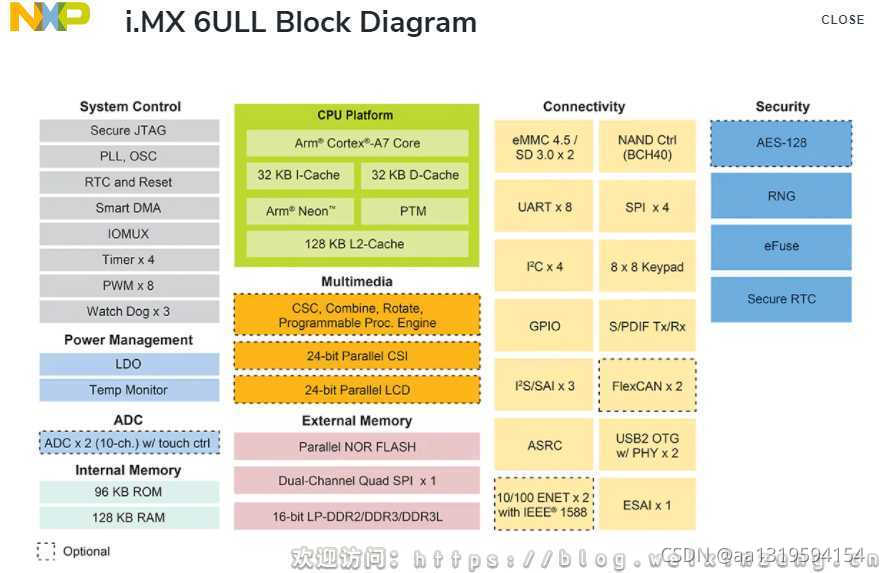

I.MX6ULLоƬ���

NXP��Ʒ��,528~900MHz��Cortex-A7�ں˵�MPU��

��������ֹ���

�����ֹ�����I.MX6ULL����������,�����ֲᡢ�ο��ֲ�ȵȡ�

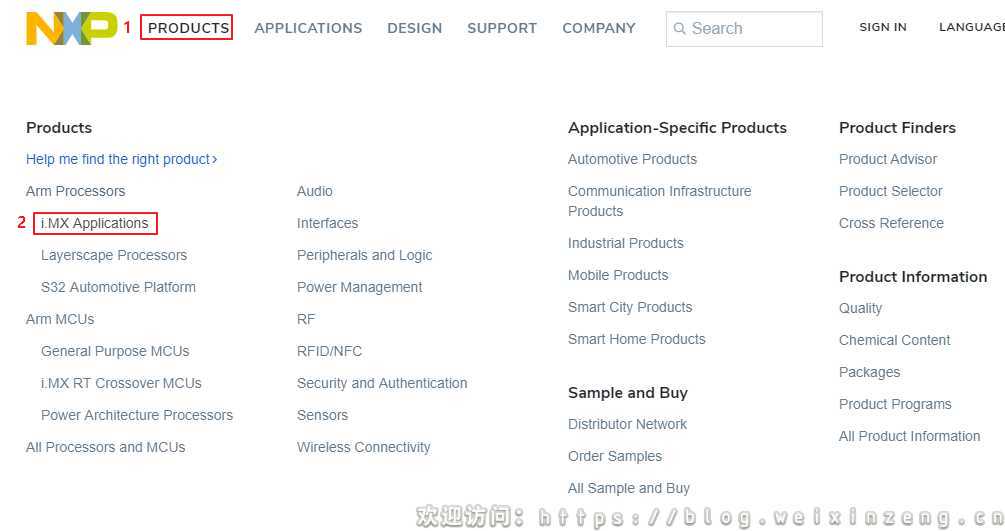

������ӽ�������ֹ���������ͼ:

���PRODUCTS�C��i.mx Applications������ͼ:

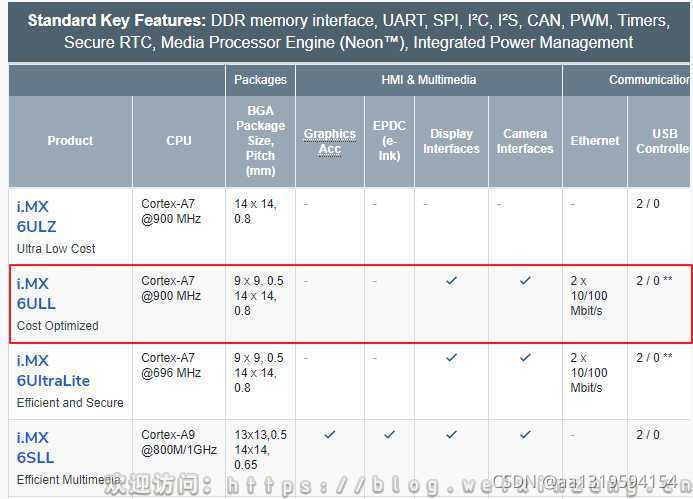

���i.MX6 Series������ͼ:

�鿴i.MX6ULL��������

���i.MX6ULL������ͼ:

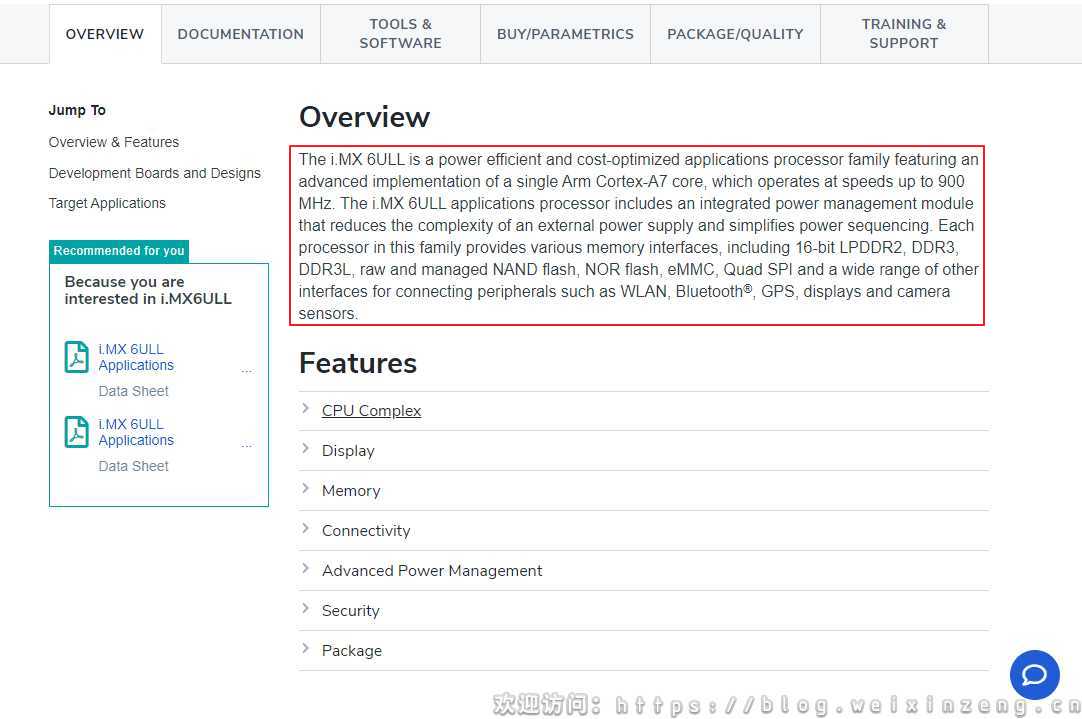

i.MX6ULL��顣����ͼ:

i.MX6ULL��Դ������ͼ:

�鿴i.MX6ULL��ϸ����

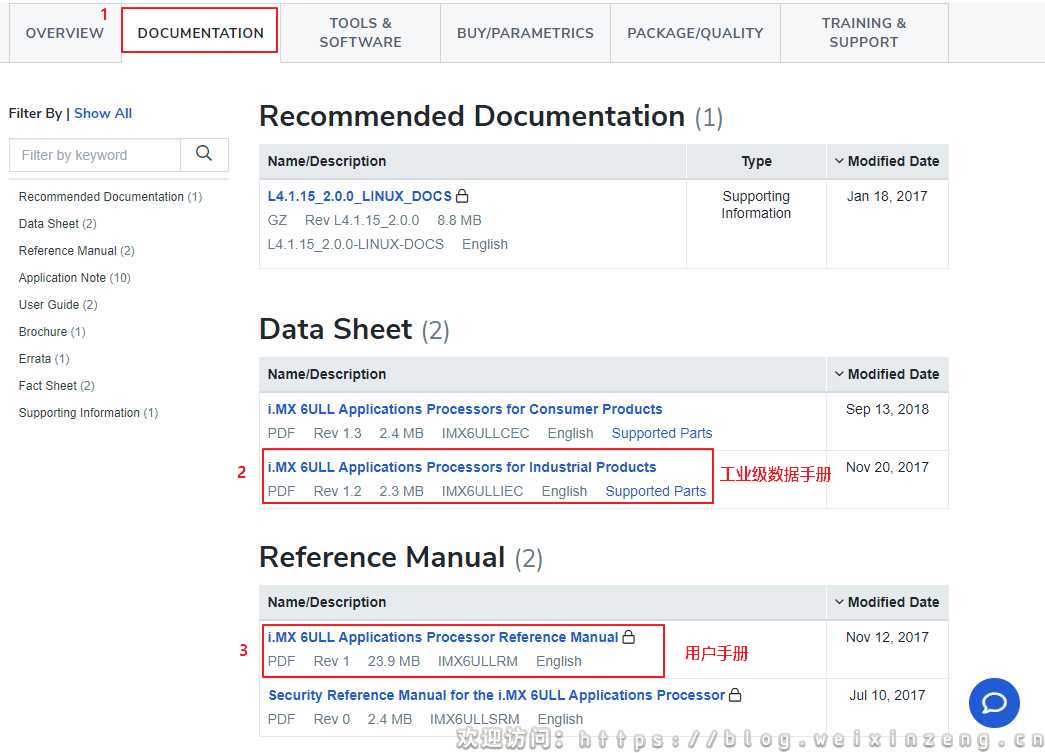

���DOCUMENTATION�C������i.MX 6ULL Applications Processors for Industrial Products�C������i.MX 6ULL Applications Processor Reference Manual��

ע��:���زο��ֲ�,��Ҫע��һ���˺š�

������ɡ�

Cortex-A7�ܹ����

I.MX6UL ʹ�õ��� Cortex-A7 �ܹ�,�������ҽ���һ�� Cortex-A7 �ܹ���һЩ����֪ʶ���˽��� Cortex-A7 �ܹ��Ժ����������Ǻ����ѧϰ,��Ϊ�����кܶ������漰�� Cortex-A7�ܹ������֪ʶ,���紦����ģ�͡�Cortex-A7 �Ĵ�����ȵ�,���� Cortex-A7 �ܹ����Ӵ�,Զ����һ�¾��ܽ����,���Ա���ֻ�Ƕ� Cortex-A7 �ܹ��������Ľ���,��Ҫ��Ϊ���Ǻ���������������

�ο��ˡ�Cortex-A7 Technical ReferenceManua.pdf���͡�ARM Cortex-A(armV7)����ֲ�V4.0.pdf���������ĵ�,�������ĵ����� ARM �ٷ����ĵ�,��ϸ�Ľ����� Cortex-A7 �ܹ���ARMv7-A ָ���

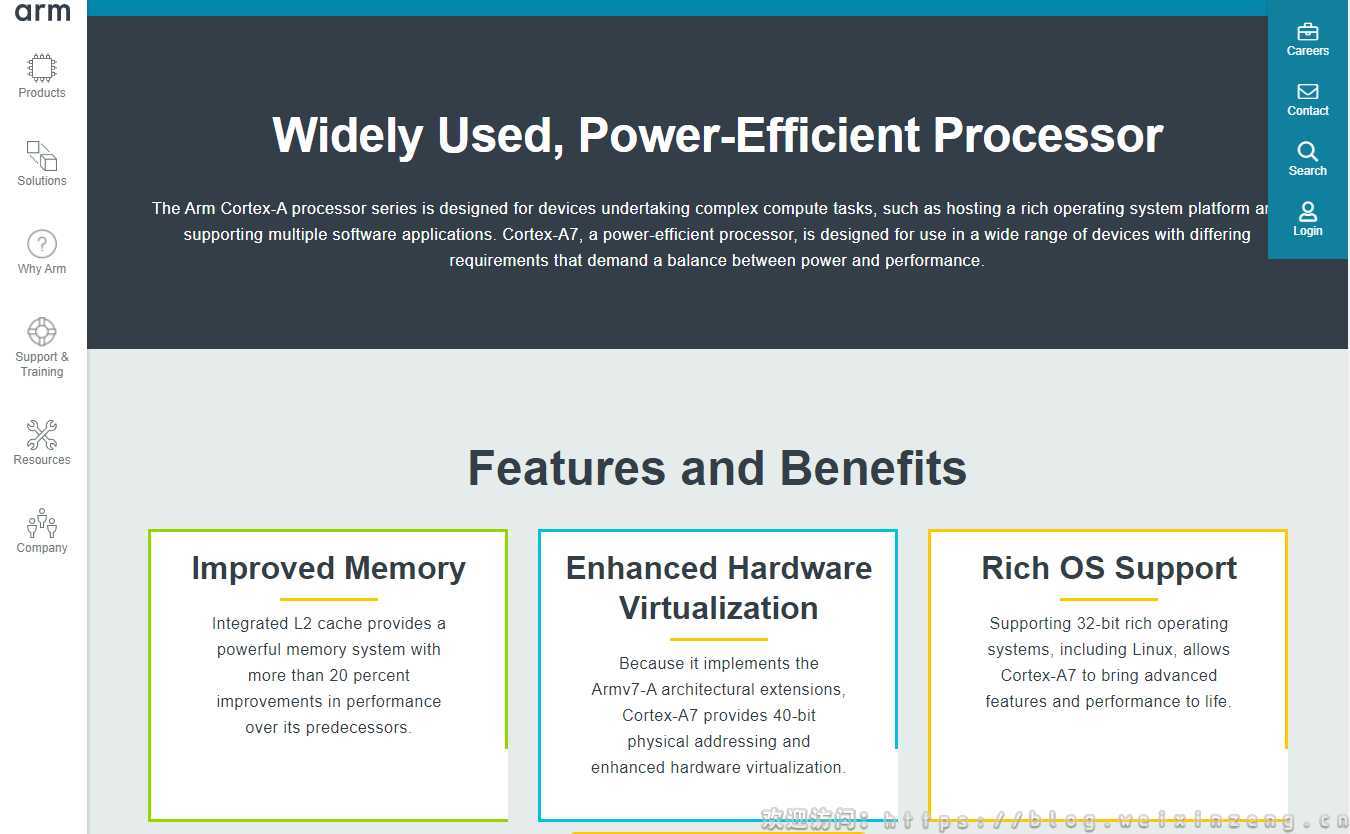

����ARM����

ARM������Cortex-A7�ܹ������ϡ�

���Products�C��CPUs������ͼ:

�����в�Ʒ��ɸѡ��Cortex-A7�C�����Cortex-A7������ͼ:

�鿴i.MX6ULL��������

�鿴i.MX6ULL��ϸ����

����վ������������ϡ����Cortex-A7 Technical Reference Manual������ͼ:

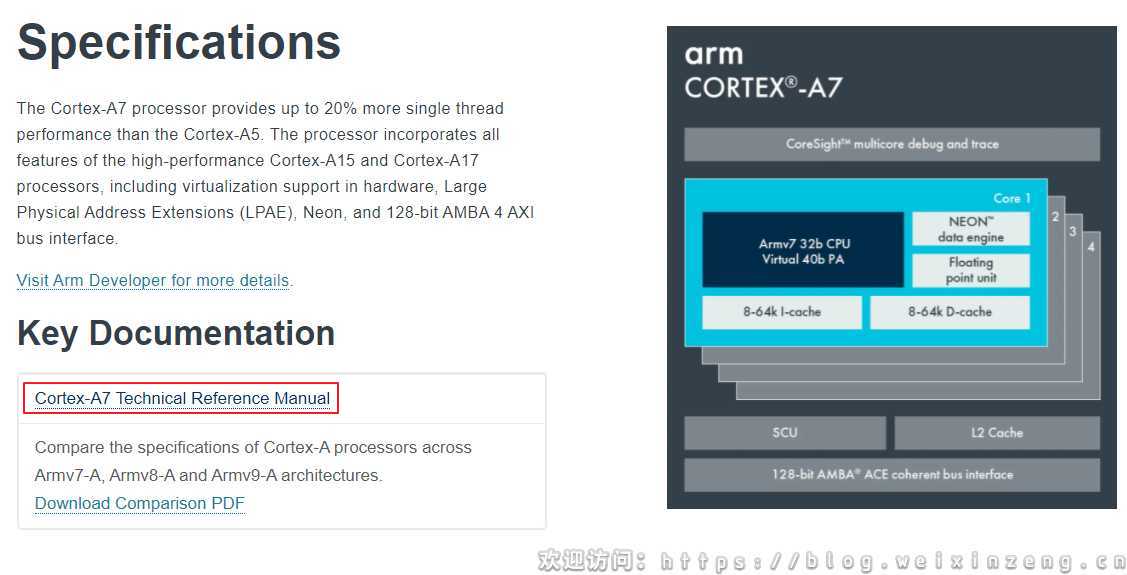

���صIJ������ϡ�����ͼ:

Cortex-A7 MPCore

Cortex-A7 MPcore ������֧�� 1~4 ��,ͨ���Ǻ� Cortex-A15 ��� big.LITTLE �ܹ�,Cortex-A15 ��Ϊ��˸������������,��������Ϸɶ��,Cortex-A7 ������ͨӦ��,��Ϊ Cortex-A7 ʡ����

Cortex-A7 ��������Ҳ����,��Ҫ�������� Cortex-A7 ���������DZ� Cortex-A8 ����Ҫǿ��,���Ҹ�ʡ�硣ARM �������� Cortex-A7 ��˵������:

���� 28nm ������,Cortex-A7 ���������� 1.2~1.6GHz,���ҵ������������ 0.45mm2(���и��㵥Ԫ��NEON �� 32KB �� L1 ����),�ڵ��ͳ����¹���С�� 100mW.

��ʹ�����dz��ʺ϶Թ���Ҫ���ϸ���ƶ��豸,����ζ�� Cortex-A7 �ڻ���� Cortex-A9 �������ܵ������,�书�ĸ�������

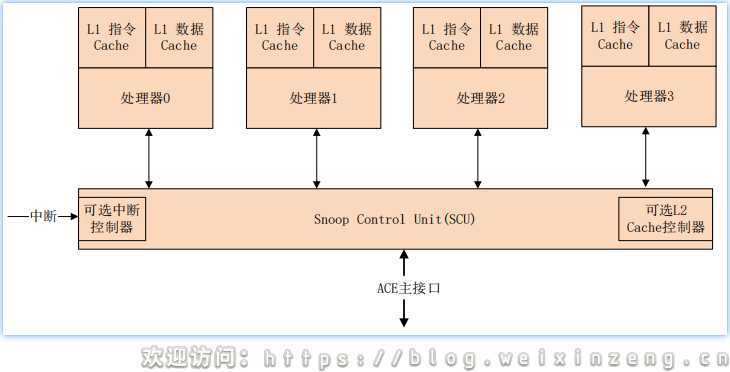

Cortex-A7 MPCore ֧����һ����������ѡ�� 1~4 ���ں�,Cortex-A7 MPCore ���������ͼ��ʾ:

Cortex-A7 MPCore �� L1 ��ѡ�� 8KB��16KB��32KB��64KB,L2 Cache ���Բ���,Ҳ����ѡ�� 128KB��256KB��512KB��1024KB��I.MX6UL ������ 32KB �� L1 ָ�� Cache �� 32KB ��L1 ���� Cache,�Լ� 128KB �� L2 Cache��Cortex-A7MPCore ʹ�� ARMv7-A �ܹ�,��Ҫ��������:

- SIMDv2 ��չ���κ�������������

- �ṩ���� ARM VFPv4 ��ϵ�ṹ���ݵĸ����ܵĵ�˫���ȸ���ָ��,֧��ȫ���ܵ�IEEE754��

- ֧�ִ�������չ(LPAE),��߿��Է��� 40 λ�洢��ַ,Ҳ������߿���֧�� 1TB ���ڴ档

- ֧��Ӳ�����⻯��

- ֧�� Generic Interrupt Controller(GIC)V2.0��

- ֧�� NEON,���Լ��ٶ�ý����źŴ����㷨��

Cortex-A ����������ģ��

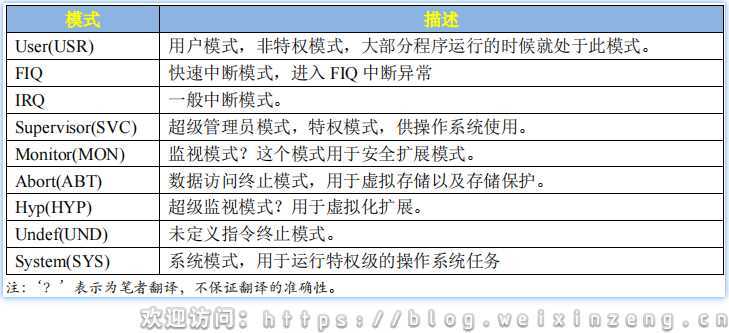

��ǰ�� ARM �������� 7 ������ģ��:User��FIQ��IRQ��Supervisor(SVC)��Abort��Undef�� System,���� User �Ƿ���Ȩģʽ,���� 6 �ж�����Ȩģʽ��

���µ� Cortex-A �ܹ�������TrustZone ��ȫ��չ,���Ծ��¼���һ������ģʽ:Monitor,

�µĴ������ܹ���֧�����⻯��չ,����ּ�������һ������ģʽ:Hyp,���� Cortex-A7 �������� 9 �ִ���ģʽ,�����ʾ:

�ڱ���,���� User(USR)�û�ģʽ����,���� 8 ������ģʽ������Ȩģʽ���⼸������ģʽ����ͨ���������������л�,Ҳ����ͨ���жϻ����쳣�������л���

������ij����������û�ģʽ,�û�ģʽ���Dz��ܷ���ϵͳ������Դ��,��Щ��Դ������,Ҫ�������Щ������Դ�ͱ������ģʽ�л��������û�ģʽ�Dz���ֱ�ӽ����л���,�û�ģʽ����Ҫ�����쳣�����ģʽ�л�,��Ҫ�л�ģʽ��ʱ��,Ӧ�ó�����Բ����쳣,���쳣�Ĵ�����������ɴ�����ģʽ�л���

���жϻ����쳣�����Ժ�,�������ͻ���뵽��Ӧ���쳣ģʽ��,ÿһ��ģʽ����һ��Ĵ������쳣��������ʹ��,������Ŀ����Ϊ�˱�֤�ڽ����쳣ģʽ�Ժ�,�û�ģʽ�µļĴ������ᱻ�ƻ�

���ѧ�� STM32 �� UCOS��FreeRTOS �ͻ�֪��,STM32 ֻ����������ģʽ,��Ȩģʽ�ͷ���Ȩģʽ,���� Cortex-A ���� 9 ������ģʽ

Cortex-A �Ĵ�����

��������Ҫ������ Cortex-A ���ں˼Ĵ�����,ע�ⲻ��оƬ������Ĵ���,������Ҫ�ο���ARM Cortex-A(armV7)����ֲ� V4.0.pdf���ġ��� 3 �� ARM Processor ModesAnd Registers����

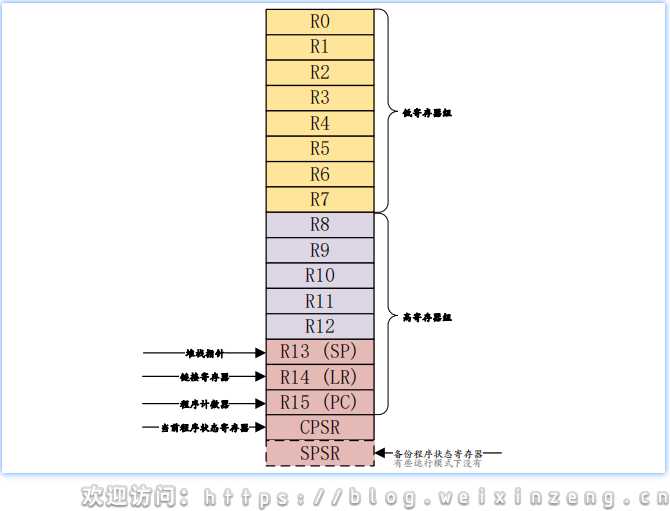

ARM �ܹ��ṩ�� 16 �� 32 λ��ͨ�üĴ���(R0~R15)������ʹ��,ǰ 15 ��(R0~R14)��������ͨ�õ����ݴ洢,R15 �dz�������� PC,�������潫Ҫִ�е�ָ�

ARM ���ṩ��һ����ǰ����״̬�Ĵ��� CPSR ��һ�����ݳ���״̬�Ĵ��� SPSR,SPSR �Ĵ������� CPSR �Ĵ����ı��ݡ��� 18 ���Ĵ�����ͼ��ʾ:

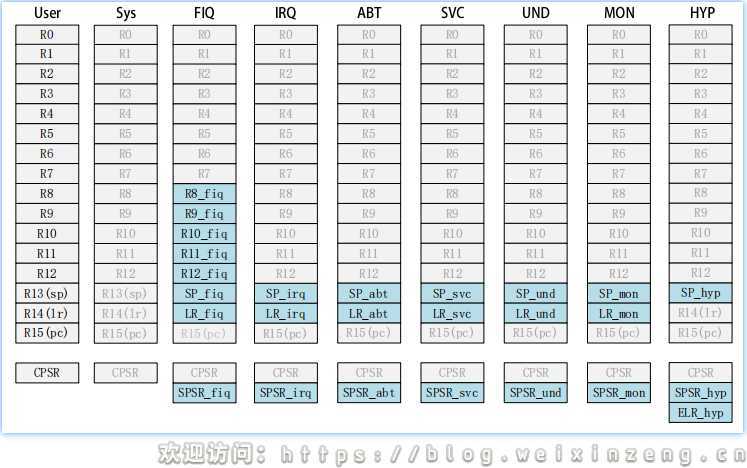

��һС�����ǽ��� Cortex-A7 �� 9 ������ģʽ,ÿһ������ģʽ����һ����֮��Ӧ�ļĴ�������ÿһ��ģʽ�ɼ��ļĴ������� 15 ��ͨ�üĴ���(R0~R14)��һ��������״̬�Ĵ�����һ����������� PC������Щ�Ĵ�����,��Щ������ģʽ�����õ�ͬһ�������Ĵ���,��һЩ�Ǹ�ģʽ�Լ�������ӵ�е�,����ģʽ��ӵ�еļĴ��������ʾ:

��ͼ��dzɫ��������� User ģʽ�����еļĴ���,����ɫ�������Ǹ���ģʽ�����еļĴ�����

���Կ���,�����е�ģʽ��,�ͼĴ�����(R0~R7)�ǹ���ͬһ�������Ĵ�����,ֻ��һЩ�Ĵ������ڲ�ͬ��ģʽ���Լ����еļĴ���,���� FIQ ģʽ�� R8~R14 �Ƕ����������Ĵ���������ij�������� FIQ ģʽ�·��� R13 �Ĵ���,����ʵ�ʷ��ʵ��ǼĴ��� R13_fiq,��������� SVC ģʽ�·��� R13 �Ĵ���,����ʵ�ʷ��ʵ��ǼĴ��� R13_svc��

�ܽ�һ��,Cortex- A �ں˼Ĵ����������:

�١�34 ��ͨ�üĴ���,���� R15 ���������(PC),��Щ�Ĵ������� 32 λ�ġ�

�ڡ�8 ��״̬�Ĵ���,���� CPSR �� SPSR��

�ۡ�Hyp ģʽ�¶���һ�� ELR_Hyp �Ĵ�����

ͨ�üĴ���

R0~R15 ����ͨ�üĴ���,ͨ�üĴ������Է�Ϊ��������:

�١�δ���ݼĴ���,�� R0~R7��

�ڡ����ݼĴ���,�� R8~R14��

�ۡ���������� PC,�� R15��

�ֱ�����һ��������Ĵ���:

δ���ݼĴ���

δ���ݼĴ���ָ���� R0~R7 �� 8 ���Ĵ���,��Ϊ�����еĴ�����ģʽ���� 8 ���Ĵ�������ͬһ�������Ĵ���,�ڲ�ͬ��ģʽ��,�� 8 ���Ĵ����е����ݾͻᱻ�ƻ��������� 8 ���Ĵ�����û�б�����������;��

���ݼĴ���

���ݼĴ����е� R8~R12 �� 5 ���Ĵ��������������Ĵ������ڿ����ж�ģʽ��(FIQ)���Ƕ�Ӧ��Rx_irq(x=8~12)�����Ĵ���,����ģʽ�¶�Ӧ�� Rx(8~12)�����Ĵ�����

FIQ �ǿ����ж�ģʽ,�����־���֪������ж�ģʽҪ�����ִ��! FIQ ģʽ���жϴ����������ʹ�� R8~R12�Ĵ���,��Ϊ FIQģʽ�µ� R8~R12 �Ƕ�����,����жϴ���������Բ���ִ�б���ͻָ��ж��ֳ���ָ��,�Ӷ������жϵ�ִ�й�����

���ݼĴ��� R13 һ���� 8 �������Ĵ���,����һ�����û�ģʽ(User)��ϵͳģʽ(Sys)���õ�,ʣ�µ� 7 ���ֱ��Ӧ 7 �ֲ�ͬ��ģʽ��

R13 Ҳ���� SP,������Ϊջָ�롣������ÿ��ģʽ����һ���Լ��� R13 �����Ĵ���,Ӧ�ó�����ʼ�� R13,ʹ��ָ���ģʽר�õ�ջ��ַ,����dz�˵�ij�ʼ�� SP ָ����

���ݼĴ��� R14 һ���� 7 �������Ĵ���,����һ�����û�ģʽ(User)��ϵͳģʽ(Sys)�ͳ�������ģʽ(Hyp)�����е�,ʣ�µ� 6 ���ֱ��Ӧ 6 �ֲ�ͬ��ģʽ��R14 Ҳ��Ϊ���ӼĴ���(LR),LR �Ĵ����� ARM ����Ҫ��������������;:

�١�ÿ�ִ�����ģʽʹ�� R14(LR)����ŵ�ǰ�ӳ���ķ��ص�ַ,���ʹ�� BL ���� BLX�������Ӻ����Ļ�,R14(LR)�����óɸ��Ӻ����ķ��ص�ַ,���Ӻ�����,�� R14(LR)�е�ֵ���� R15(PC)��������Ӻ�������,�������ӳ����п���ʹ�����´���:

MOV PC, LR @�Ĵ��� LR �е�ֵ��ֵ�� PC,ʵ����ת

���߿������Ӻ�������ڳ��� LR ��ջ:

PUSH {LR} @�� LR �Ĵ���ѹջ

���Ӻ�����������ջ����:

POP {PC}

@������ѹջ�� LR �Ĵ������ݳ�ջ�� PC �Ĵ���,�ϸ�����������Ӧ���ǽ�

@LR-4 ���� PC,��Ϊ 3 ����ˮ��,����ֻ����ʾ���롣

�ڡ����쳣�����Ժ�,���쳣ģʽ��Ӧ�� R14 �Ĵ��������óɸ��쳣ģʽ��Ҫ���صĵ�ַ,

R14 Ҳ���Ե�����ͨ�Ĵ���ʹ�á�

����״̬�Ĵ���

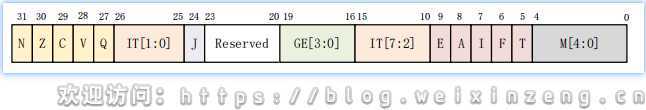

���еĴ�����ģʽ������һ�� CPSR �����Ĵ���,��� CPSR �������κ�ģʽ�±����ʡ�CPSR�ǵ�ǰ����״̬�Ĵ���,�üĴ���������������־λ���жϽ�ֹλ����ǰ������ģʽ��־��һЩ״̬λ�Լ�һЩ����λ��

���еĴ�����ģʽ������һ�� CPSR ��Ȼ�ᵼ�³�ͻ,Ϊ��,����User �� Sys ������ģʽ����,���� 7 ��ģʽÿ�����䱸��һ��ר�õ�����״̬�Ĵ���,����SPSR(���ݳ���״̬�Ĵ���),���ض����쳣�жϷ���ʱ,SPSR �Ĵ����������浱ǰ����״̬�Ĵ���(CPSR)��ֵ,���쳣�˳��Ժ������ SPSR �б����ֵ���ָ� CPSR��

��Ϊ User �� Sys ������ģʽ�����쳣ģʽ,���Բ�û���䱸 SPSR,��˲����� User ��Sys ģʽ�·��� SPSR,�ᵼ�²���Ԥ֪�Ľ�������� SPSR �� CPSR �ı���,��� SPSR �� CPSR �ļĴ����ṹ��ͬ,��ͼ��ʾ:

- N(bit31):�����������ʾ�� �з������������ʱ��,N=1 ��ʾ����ԵĽ��Ϊ����,N=0��ʾ���Ϊ������

- Z(bit30):Z=1 ��ʾ������Ϊ��,Z=0 ��ʾ��������Ϊ��,���� CMP ָ��,Z=1 ��ʾ���бȽϵ���������С��ȡ�

- C(bit29):�ڼӷ�ָ����,����������˽�λ,�� C=1,��ʾ���������㷢������,��������� C=0���ڼ���ָ����,�������з�����λ,�� C=0,��ʾ���������㷢������,��������� C=1�����ڰ�����λ�����ķǼ�/��������ָ��,C �а������һ�������λ����ֵ,���������Ǽ�/������ָ��,C λ��ֵͨ������Ӱ�졣

- V(bit28):���ڼ�/��������ָ��,������������������ʾΪ�����ƵIJ����ʾ�Ĵ�������ʱ,V=1 ��ʾ����λ���,ͨ������λ��Ӱ�� V λ��

- Q(bit27):�� ARM v5TE_J �ܹ�֧��,��ʾ����״̬,Q=1 ��ʾ�ۻ�����,Q=0 ��ʾ�ۻ������͡�

- **IT[1:0](bit26:25):�� IT[7:2](bit15:bit10)**һ����� IT[7:0],��Ϊ IF-THEN ָ��ִ��״̬��

- J(bit24):�� ARM_v5TE-J �ܹ�֧��,J=1 ��ʾ���� Jazelle ״̬,��λͨ���� T(bit5)λһ���ʾ��ǰ��ʹ�õ�ָ�,

�����ʾ:

| J | T | ���� |

|---|---|---|

| 0 | 0 | ARM |

| 0 | 1 | Thumb |

| 1 | 1 | ThumbEE |

| 1 | 0 | Jazelle |

- GE[3:0](bit19:16):SIMD ָ����Ч,���ڻ���ڡ�

- IT[7:2](bit15:10):�ο� IT[1:0]��

- E(bit9):��С�˿���λ,E=1 ��ʾ���ģʽ,E=0 ��ʾС��ģʽ��

- A(bit8):��ֹ�첽�ж�λ,A=1 ��ʾ��ֹ�첽�жϡ�

- I(bit7):I=1 ��ֹ IRQ,I=0 ʹ�� IRQ��

- F(bit6):F=1 ��ֹ FIQ,F=0 ʹ�� FIQ�� T(bit5):����ָ��ִ��״̬,������ָ���� ARM ָ��� Thumb ָ��,ͨ���� J(bit24)һ�����ָ������,�ο� J(bit24)λ��

- M[4:0]:������ģʽ����λ,���������ʾ:

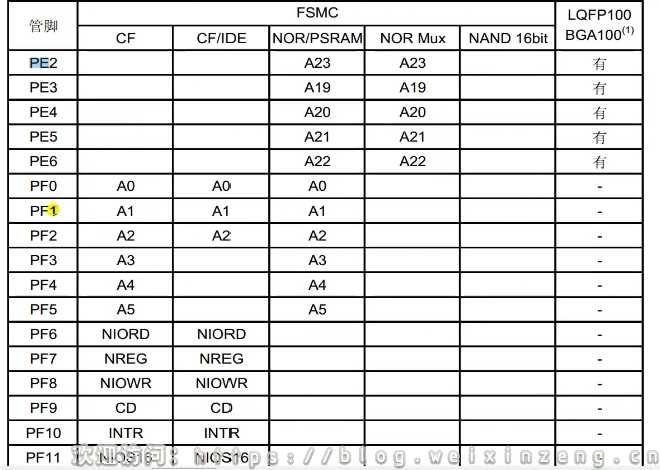

I.MAX6ULL��IO����Ϣ

STM32

�ܽ�����

STM32:�ܽ�����:PA0~15,PB0~15 PC��PD������

�ܽŸ���

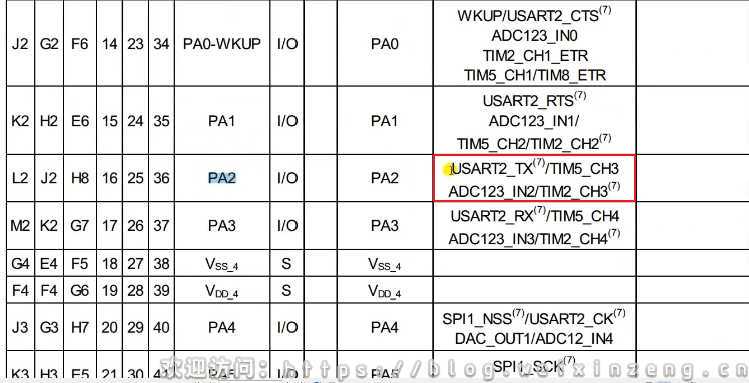

I.MAX6ULL

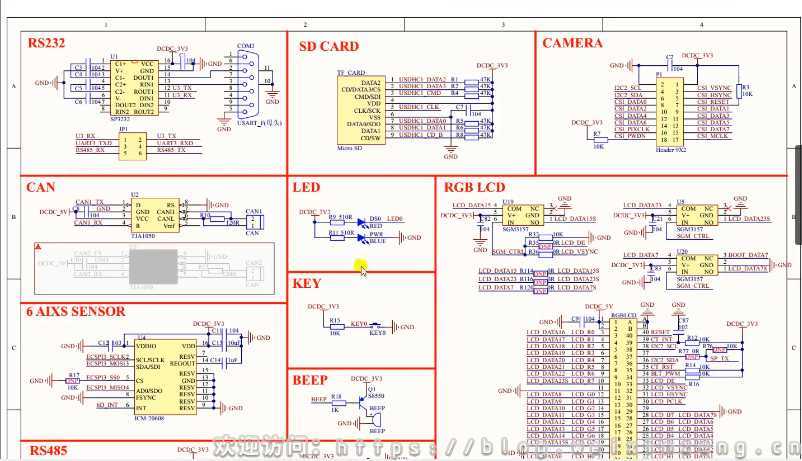

��ԭ��ͼ

�������ԭ��ͼ����Ҫ�˽�ij���ܽŵĹ��ܡ�

�ο��ֲ�

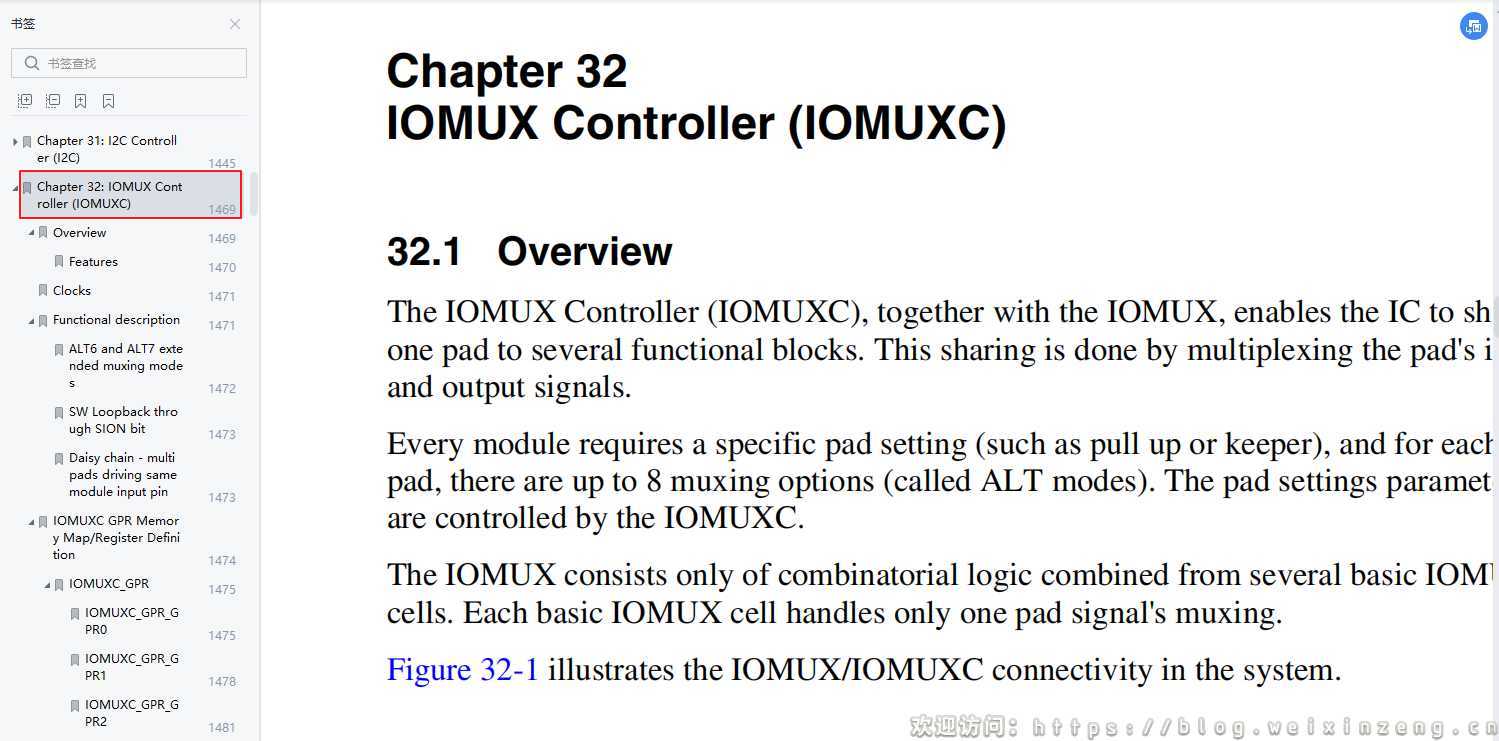

��I.MAX6ULL�ο��ֲ�,�ҵ�32��IO�����½ڡ�

�ܽ�����

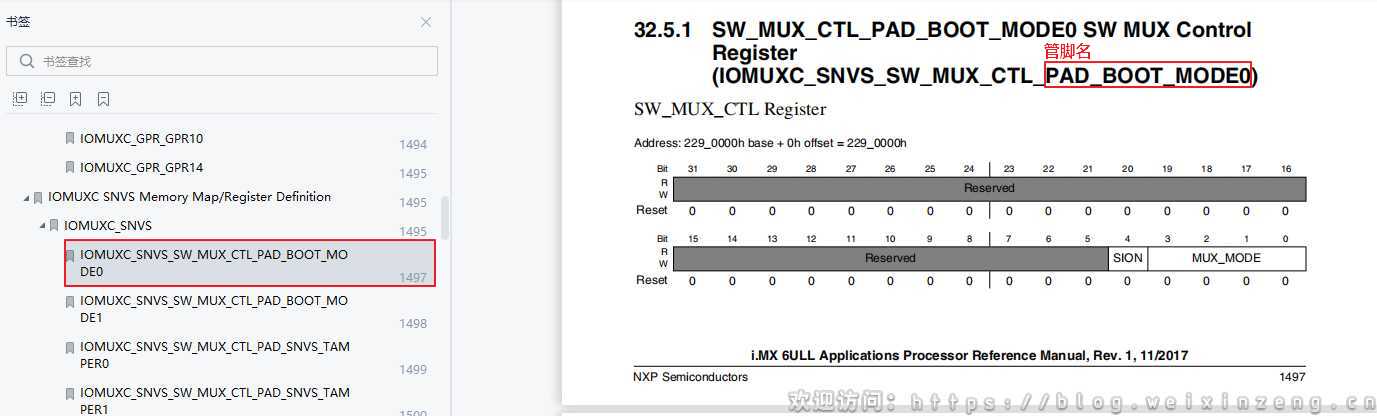

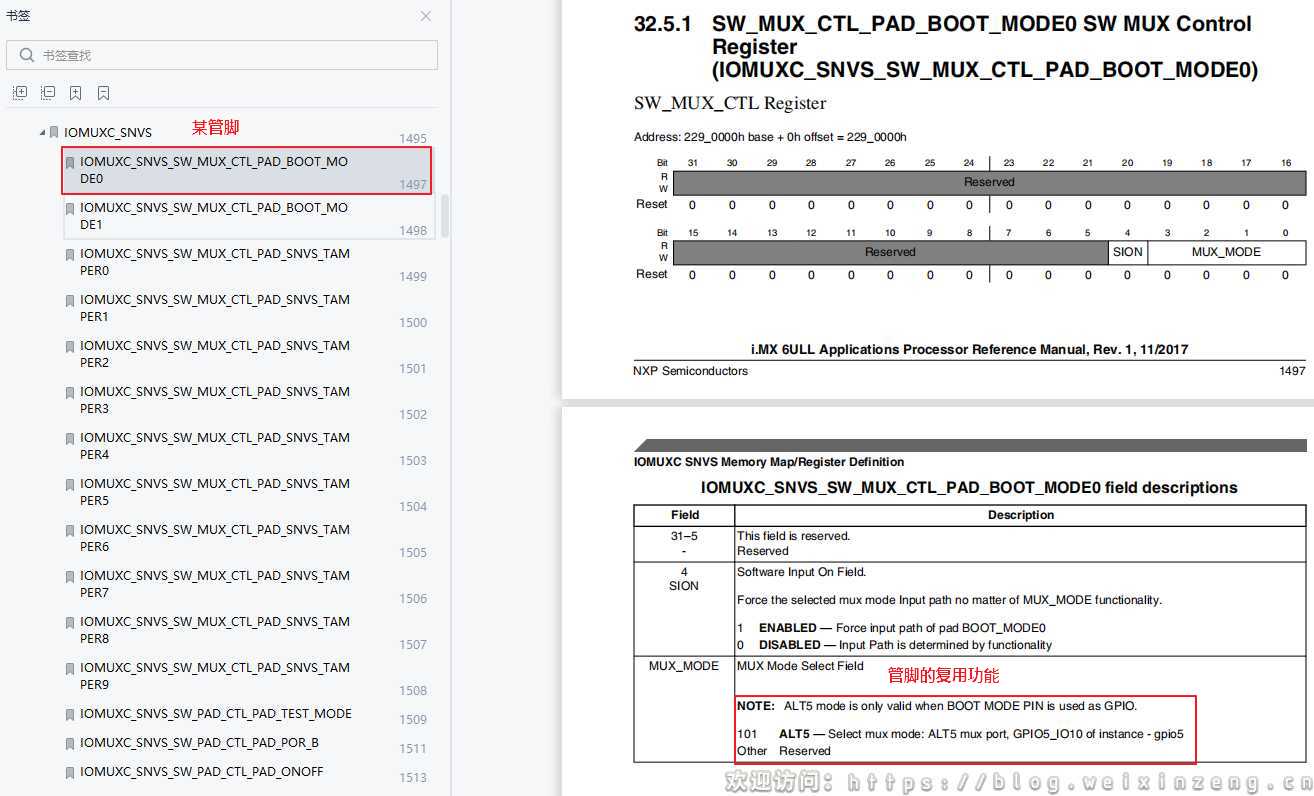

PAD_BOOT_MODE0,ѡ��ICMUXC_SNVS�µĵ�һ���ܽš�����ͼ:

�ܽŵĸ���

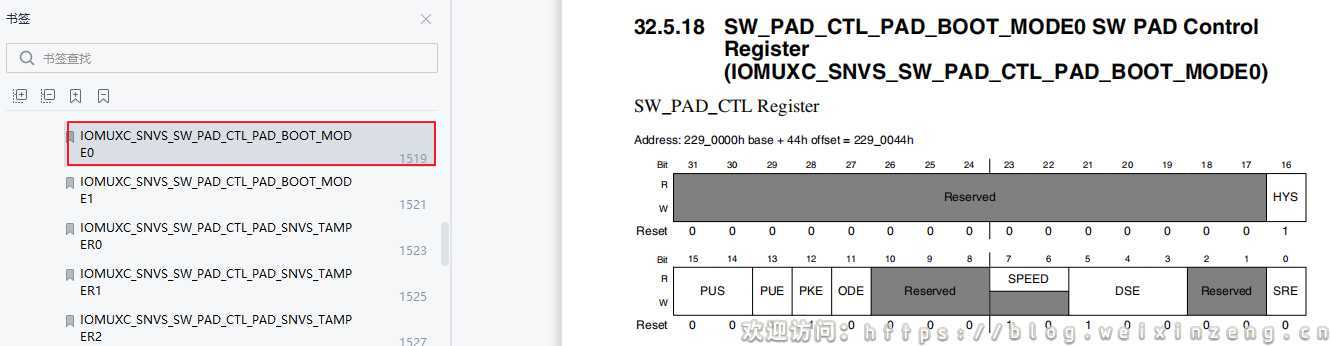

? �������йܽŶ��������Ĵ���,���ĵ���Ѱ��IOMUXC_SNVS_SW_PAD_CTL_PAD_BOOT_MODE0�Ĵ���(���õ�������)��Ӧ��IOMUXC_SNVS_SW_MUX_CTL_PAD_BOOT_MODE0�Ĵ���(���ø���)������ͼ:

MUX�������Ǹ��ù��ܡ�

����

�����Դ����

i.MAX6ULL����.rar-Ƕ��ʽ�ĵ�����Դ-CSDN����

�������

��ӭ��ע�Ź��ں�