һ��ʱ�ӹ���

��Ƭ��ϵͳ(SOC)��,��ͬ��ģ��ͨ����Ҫ�����ڲ�ͬ��ʱ��Ƶ�ʡ�Ϊ��������Щ����,оƬ��ʱ��Դ�źŽ����ȶ�����Ƶ����Ƶ���ַ��Լ�����(gate)�Ȳ���,������ͬƵ�ʵ�ʱ���źš���Щʱ���źź����ǵĹ�����·������оƬ��ʱ����ϵ,�����Ÿ��ָ����Ĺ���ģ��Эͬ������

������������һ��ʱ�ӹ���ϵͳ:

IMX6ULL��7�������·,���ǵ�����ʱ���źų�ΪԴʱ���ź�,��ͨ���Ĵ���ѡ��,ͨ��ΪXTALOSC24M������24MHZʱ���źš����ǵ����������һ��ѡ��ͷ�Ƶ,�γɲ�ͬ�ĸ�ʱ���ź�,�ַ�������ģ��ʹ�á�imx6ull 7·PLL���������ʽ����:

![[����ͼƬת��ʧ��,Դվ�����з���������,���齫ͼƬ��������ֱ���ϴ�(img-cczo4a4N-1631186411137)(E:\u-boot\pic\IMX6ULL_CCM.jpg)]](https://img-blog.csdnimg.cn/bff886b1005349b2baab50d2f03030bf.jpg?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBAcmlzY19sdWNr,size_20,color_FFFFFF,t_70,g_se,x_16)

ʱ�����ɲ��ְ����߸�PLL�� ��������PLLÿ�����䱸���ĸ���λ����������(PFDs),�Բ��������Ƶ�ʡ�ÿ��PFDͨ����ֵ�����ӵ�PLL��VCO��������������Ч������PLLVCOƵ��,����N��12��35�����������18/NxFvco��PFD��һ����ȫ���ֻ������,û��ģ��Ԫ��������·��Ƶ�ʿ���ʱ��������ö�,��Ϊ���ֻ�����������ı�����Nֻ��ı�VCO��ֵ���������ϡ���ע��,PFD����������PLL�����Ƶ�ʱ仯,���������ڲ��������ʱ�ӽ���/���ù��̵�����°�ȫ�ء���̬���������á�

�����г����߸�PLL:

1.PLL1(ARM_PLL) ��������ARM���Ĺ��� ,���ɱ����1.3GHZ,��оƬ����֧�ֵ�Ƶ��1.0GHZҪ�ߡ�

2.PLL2(System_PLL or 528_PLL),��24M�ⲿ����������,�Թ̶�22��Ƶ���528MHZƵ��,���������,��PLL��������·PFD(PLL2_PFD0 �� PLL2_PFD3).������������PFD�����Ϊ����ʱ�Ӹ�������.��Щ����Ҫ��ȷ/�㶨��Ƶ��,������Ϊ��̬Ƶ�����Ź��̵�һ���ֽ��и���.ͨ��,��PLL����PFD���ڲ�ϵͳ���ߡ��ڲ���������DDR�ӿڡ�NAND/NOR�ӿ�ģ��ȵ�ʱ��Դ

3.PLL3(USB1_PLL), PLL3��Ӧ������USB PHY��һ��ʾ������,����������ĸ�PFD (PLL3_PFD0�� PLL3_PFD3),����20�Ĺ̶���Ƶ���480MHZ��

4.PLL4(Audio PLL) ����һ�������˷������,���ڲ����Ͷ����߾��ȵ���Ƶʱ�����������ƵƵ�ʡ��������Ƶ�ʷ�Χ��650MHz��1300MHz,Ƶ�ʷֱ�������1Hz����ʱ����Ҫ����������Ƶ�ӿڵ�ʱ�Ӻ��ⲿ��Ƶ��������IJο�ʱ�ӡ����������װ��һ����Ƶ��,���Դ�PLLVCOƵ�ʲ�������1��2��4

5.PLL5(Video PLL)����һ�������˷������,���ڲ����Ͷ����߾��ȵ���Ƶʱ�����������ƵƵ��,�������Ƶ�ʷ�Χ��650MHz��1300MHz,Ƶ�ʷֱ�������1Hz�� ��ʱ����Ҫ������ʾ����Ƶ�ӿڵ�ʱ�ӡ�������������䱸�˷�����,���Դ�PLLVCOƵ�ʲ���ʱ�ӳ���1��2��4��8��16

6.PLL6(ENET_PLL)���PLLʵ����һ���̶���20(5/6)������ ����24MHz������,��VCOƵ��Ϊ500MHz�� ��PLL��������:

���ⲿ��̫���ӿڵ�50��25MHz

��125MHz���ڼ�ǧ����̫���ӿ�

��ͨ��100MHz

7.PLL7(USB2_PLL) ���PLLר��ΪUSB2PHY(USBPHY2,Ҳ��ΪOTGPHY)�ṩʱ��)�� ����20�Ĺ̶���������,����VCOƵ��Ϊ480MHz��

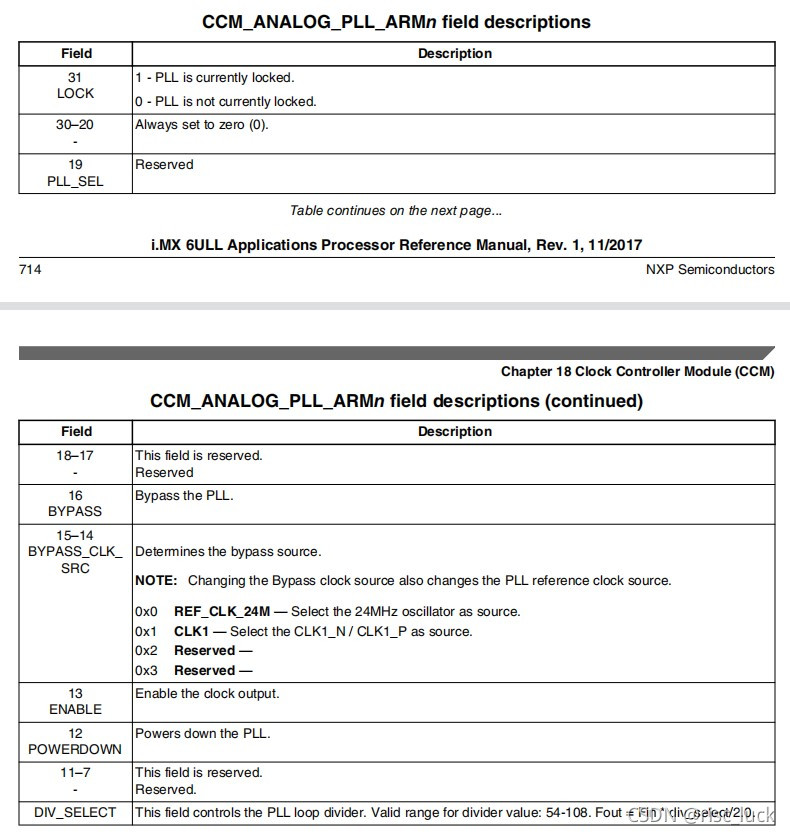

Reference input clock for any of the PLLs could be selected individually by the BYPASS_CLK_SRC field of the PLL control register. See CCM Analog Memory Map/Register Definition for more information.

ÿ��PLL���úͿ��ƹ��ܶ�����ͨ����PFD��ȫ�����ú�״̬�Ĵ����������ʡ��κ�PLL�IJο�����ʱ�Ӷ�������PLL���ƼĴ�����BYPASS_CLK_SRC�ֶε���ѡ��ÿ��PLL���Ե�������Ϊ����·������������á��͡��ϵ硱ģʽ��

��Bypassģʽ:PLL����IJο�ʱ��ֱ�Ӵ��ݵ����,��BYPASSλ����;

�� �����ֹģʽ:����bypassʱ�ӻ���PLL���ɵ�ʱ�Ӿ�����ֹ,�����ʱ���ź�,��ENABLEλ����;

�� �ϵ�ģʽ:PLL�дֵ�·�ϵ�,�����ʱ���ź�,��POWERDOWNλ���ơ�

��ARM_PLLΪ��,������ȡ����˵��,����ͼ��PLL��������ʱ,ʱ���ź�ͨ��·��1������Ϊ�ź�ref_armpll_clk���;����Bypassģʽʱ,Դʱ���źŲ�����PLL�Ŵ�,��·��2ֱ�����;���������ֹģʽʱ,ʱ���ź���armpll_enable��������,ref_armpll_clk�����;���ڶϵ�ģʽʱ,ARM_PLL�ֵ�·�ϵ�,��·������,ref_armpll_clk������źš�

![[����ͼƬת��ʧ��,Դվ�����з���������,���齫ͼƬ��������ֱ���ϴ�(img-2LcFgk8T-1631186411139)(E:\u-boot\pic\armpll.png)]](https://img-blog.csdnimg.cn/3e91860caa5442d9ade3c4e3a9c8fb3b.png?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBAcmlzY19sdWNr,size_20,color_FFFFFF,t_70,g_se,x_16)

����CCM �ڲ�ʱ�Ӳ���

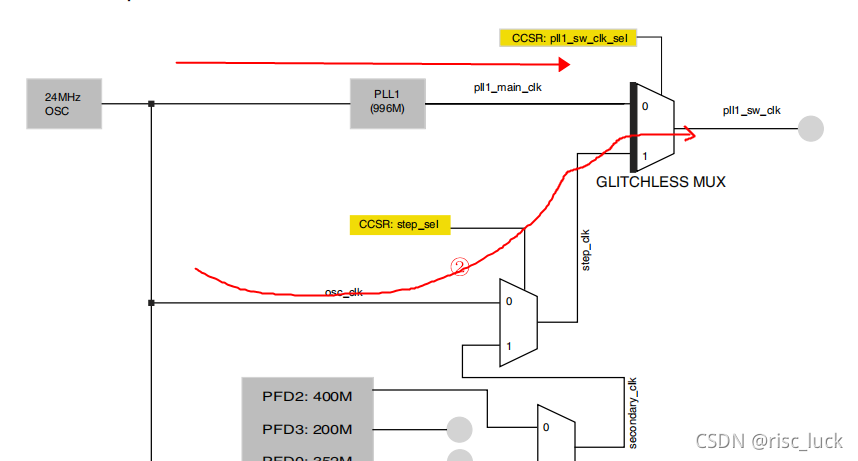

7·PLL������ֱ���ṩ������ģ��ֱ��ʹ��,������Ҫ����ѡ��Ƶ���γɸ�ʱ���ź�,Ȼ��ַ�������ģ��ʹ��(���ʱ�ӹ�����ͼ��������)����ʱ���źŵ�·��Ϊ������,ʱ���л���·��ʱ�����ɵ�·��The Clock Switcher (CCM_CLK_SWITCHER) sub-module receives the PLL output clocks and the PLL bypass clocks.ʱ���л���·��Ҫ��PLL1��PLL3���������ѡ��,��ѡ�е��ź��γ�pll1_sw_clk��pll3_sw_clk�źš�����,������PLL4��PLL5���ж���ķ�Ƶ����,�γ�pll4_main_clk��pll5_main_clk�źš����ͼ����:

������·��ֱ��ʹ������PLL�����,����ʹ��switcher�γɵ���Щ����źš�����,���������ı�CPU�Ĺ���Ƶ��,��������CCSR[pll1_sw_clk_sel]��pll1_sw_clk�л���step_clk,Ȼ����PLL1�IJ���,�ȴ������ʱ���ź��ȶ����µ�Ƶ����,���л���PLL1������ź�pll1_main_clk����Ϊʹ���������Ķ�·ѡ����(glitchless multiplexer),���л�������CPU����������,���ǽ��ڵ�һ�����ʾ������ʾ�������̡�

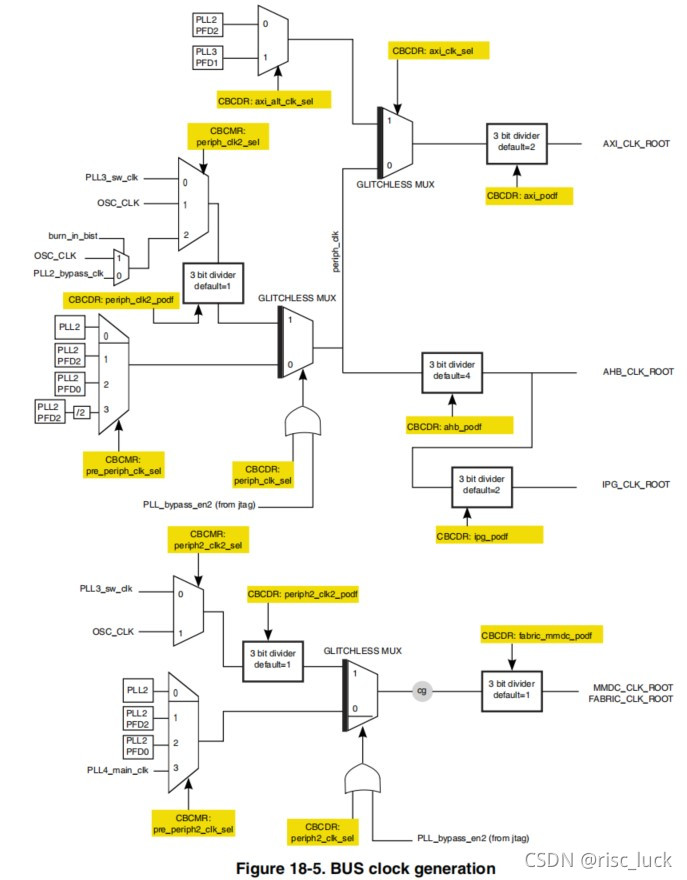

The Clock Root Generator (CCM_CLK_ROOT_GEN) sub-module generates the root clocks to be delivered to LPCG. ����ͼ��ʾ:

�����ʱ�����ÿ��Բο������ʱ����:

![[����ͼƬת��ʧ��,Դվ�����з���������,���齫ͼƬ��������ֱ���ϴ�(img-aBu4b3zQ-1631186411141)(E:\u-boot\pic\clock tree1.jpg)]](https://img-blog.csdnimg.cn/b1873e85428a444a88d5d718564c466e.jpg?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBAcmlzY19sdWNr,size_20,color_FFFFFF,t_70,g_se,x_16)

����ʱ����������

3.1 PLL����

������������PLL1,Ҳ����cpu��Ƶ,����������Ϊ�C648M(�������ѡ��)��

��������,����֪����Ƶ��Ҫ�漰��PLL1�����Լ�CCM_CACRR ��Ƶϵ���趨����������ʱ,CPUʹ�������·ARM_PLL������ź���Ϊʱ��Դ���ڸı�CPUƵ��֮ǰ,���������л�������ʱ���ź�(ʾ����ѡ������·XTALOSC24M�����),��ARM_PLL���ò��ȶ����µ�Ƶ��֮��,���л���ARM_PLL�����ʱ���źš����岽������:

- step_clkѡ��ʹ��OSC�����,bit8 ��0

- ѡ��step_clk ,bit 2��1

3.����ARM_PLL�ı�Ƶ�������ȴ����������״̬��

����DIV_SELECTΪ108,��Χ��54-108,Ȼ���ȡ�Ĵ��� ֱ��bit31Ϊ1

![[����ͼƬת��ʧ��,Դվ�����з���������,���齫ͼƬ��������ֱ���ϴ�(img-pVaQzdaZ-1631186411144)(E:\u-boot\pic\ccm_cacrr.jpg)]](https://img-blog.csdnimg.cn/191485adfde44f8da254c4e36fab404d.jpg?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBAcmlzY19sdWNr,size_20,color_FFFFFF,t_70,g_se,x_16)

4.���÷�Ƶϵ��cacrr�Ĵ���Ϊ1,ϵ��/2.

5.��ARM_ROOT�л���ARM_PLL,ѡ��pll1_main_clk , ���ccsr bit2

PLL2��PLL3 �� PLL7 �̶�Ϊ 528MHz��480MHz �� 480MHz,PLL4~PLL6 ����������������,�õ���ʱ�������á�

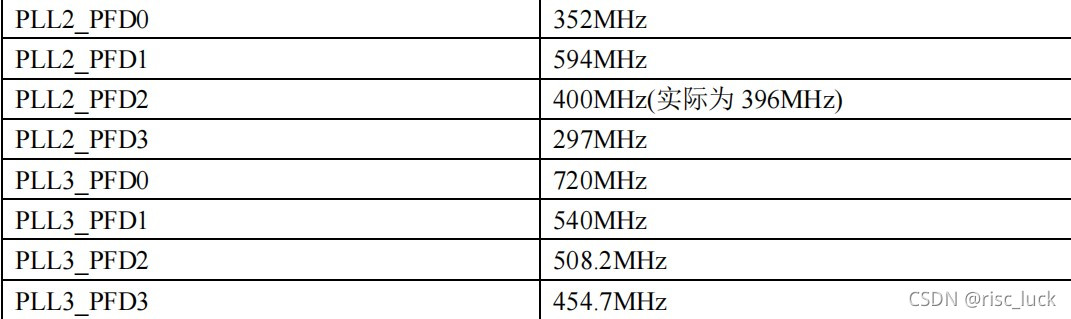

3.2 PFDƵ���趨

nxp �Ƽ���PFDƵ������:

PLL2��4·PFDƵ��ʹ�üĴ��� CCM_ANALOG_PFD_528n����

![[����ͼƬת��ʧ��,Դվ�����з���������,���齫ͼƬ��������ֱ���ϴ�(img-NazZCU0Z-1631186411145)(E:\u-boot\pic\CCM_ANALOG_PFD_528n.jpg)]](https://img-blog.csdnimg.cn/34422cf910954482aab68ff48c311968.jpg?x-oss-process=image/watermark,type_ZHJvaWRzYW5zZmFsbGJhY2s,shadow_50,text_Q1NETiBAcmlzY19sdWNr,size_19,color_FFFFFF,t_70,g_se,x_16)

�Ĵ��� CCM_ANALOG_PFD_528n ��ʵ��Ϊ����,�ֱ��ӦPFD0~PFD3,ÿ�� 8 �� bit,���Ǿ��� PFD0 Ϊ��,��һ��������� PLL2_PFD0 ��Ƶ�ʡ�PFD0��Ӧ�ļĴ���λ����:PFD0_FRAC: PLL2_PFD0 �ķ�Ƶ��,PLL2_PFD0 �ļ��㹫ʽΪ 528x18/PFD0_FRAC,��Ϊ�����õķ�ΧΪ 12~35 �� �� �� PLL2_PFD0 ��Ƶ��Ҫ����Ϊ 352MHz �� �� PFD0_FRAC=528*18/352=27��

PFD0_STABLE: ��λΪֻ��λ,����ͨ����ȡ��λ�ж� PLL2_PFD0 �Ƿ��ȶ���

PFD0_CLKGATE: PLL2_PFD0 ���ʹ��λ,Ϊ 1 ��ʱ��ر� PLL2_PFD0 �����,Ϊ 0 ��ʱ��ʹ�������

PLL3��4·pfdƵ�����������Ƶ�,ֻ�����Ĵ�����ΪCCM_ANALOG_PFD_480n, ��ʽΪ 480x18/PFDx_FRAC

3.3 AHB��IPG ��PERCLK ��ʱ������

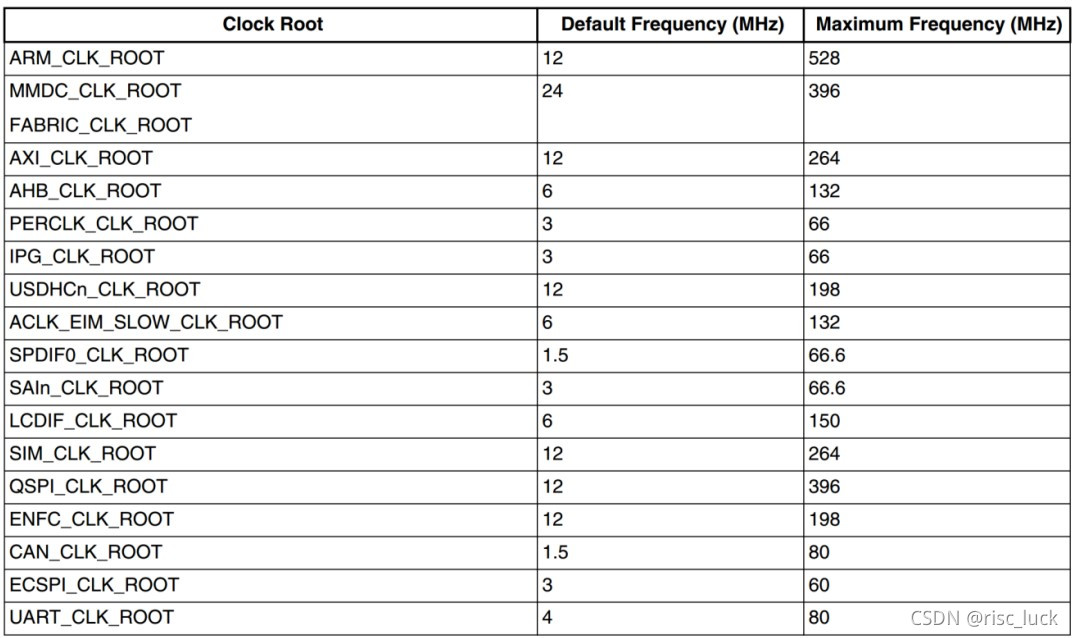

imx6u����ʱ�ӿ����÷�Χ����:

�������òο��ڶ���ʱ��·��������Ӧ�Ĵ����ͺ�����ʵ�֡�