ͨ��Э��(IIC/SPI)

һ��IIC

IIC:����ʽ��������,������������SDA��ʱ����SCL���ɵĴ�������,�ɷ��ͺͽ������ݡ�

��CPU�뱻��IC֮�䡢IC��IC֮�����˫����,����IIC����һ��ɴ�400kbs���ϡ�

ʱ����SCL:��ͨ�Ź����������á�

������SDA:����һλһλ�Ĵ������ݡ�

IIC��Ϊ����IIC��Ӳ��IIC

����IIC:����IICͨ��ָ�����õ�Ƭ��������I/O�˿�ģ�������IIC,���������ƹܽ�״̬��ģ��I2Cͨ�Ų���,����ģ��Ĵ����Ĺ�����ʽ��

Ӳ��IIC:һ��Ӳ����·,Ӳ��I2C��ӦоƬ�ϵ�I2C����,����ӦI2C������·,����ʹ�õ�I2C�ܽ�Ҳ��ר�õ�,Ӳ��(�̼�)I2C��ֱ�ӵ����ڲ��Ĵ����������á�

����:

1.Ӳ��I2C��Ч��ҪԶ����������,������I2C���ڲ��ܹܽ�����,�ӿڱȽ���

2.IIC�ǰ�˫��ͨ�ŷ�ʽ��

IICͨ��Э��

IICͨ�Ź����ɿ�ʼ�����������͡���Ӧ������������ֹ��ɡ�

1��(�ڷ��͡��������ݵ�ʱ��)��SCLΪ�ߵ�ƽʱ,SDA�߲������仯;��SCL��Ϊ�͵�ƽʱ,SDA�߿�������0��1�仯��

2��(������ʱ��)ֻ�е�SCLΪ�ߵ�ƽʱ,IIC��·�Ŷ�SDA���ϵĵ�ƽ(0����1)���м�¼,��SCL��Ϊ�͵�ƽʱ,����SDA�Ǹ��ǵ�,IIC��·������SDA���в�����

����״̬

�ڽ��������������ǰ,��������˵˵����״̬,ʲô�ǿ���״̬,����û��ͨ��ʱ��״̬(��ʼ״̬)

I2C���ߵ�SDA��SCL�����ź�ͬʱ���ڸߵ�ƽʱ,�涨Ϊ���ߵĿ���״̬����ʱ�����������������Ч�ܾ����ڽ�ֹ״̬,���ͷ�����,�������ź��߸��Ե���������ѵ�ƽ���ߡ�

��ʼ�ź���ֹͣ�ź�

��ʼ�ź�:��SCLΪ���ڼ�,SDA�ɸߵ��͵�����;�����ź���һ�ֵ�ƽ����ʱ���ź�,������һ����ƽ��

ֹͣ�ź�:��SCLΪ���ڼ�,SDA�ɵ͵��ߵ�����;ֹͣ�ź�Ҳ��һ�ֵ�ƽ����ʱ���ź�,������һ����ƽ�źš�

Ӧ���ź�

������ÿ����һ���ֽ�,����ʱ������9�ڼ��ͷ�������,�ɽ���������һ��Ӧ���źš�Ӧ���ź�Ϊ�͵�ƽʱ,�涨Ϊ��ЧӦ��λ(ACK���Ӧ��λ),��ʾ�������Ѿ��ɹ������˸��ֽ�;Ӧ���ź�Ϊ�ߵ�ƽʱ,�涨Ϊ��Ӧ��λ(NACK),һ���ʾ���������ո��ֽ�û�гɹ���

���ڷ�����ЧӦ��λACK��Ҫ����,�������ڵ�9��ʱ������֮ǰ�ĵ͵�ƽ�ڼ佫SDA������,����ȷ���ڸ�ʱ�ӵĸߵ�ƽ�ڼ�λ�ȶ��ĵ͵�ƽ�������������������,�������յ����һ���ֽں�,����һ��NACK�ź�,��֪ͨ���ط������������ݷ���,���ͷ�SDA��,�Ա����ؽ���������һ��ֹͣ�ź�P

ÿ��������ӻ�������һ���ֽڵ�����,����������Ҫ�ȴ��ӻ�����һ��Ӧ���ź�,��ȷ�ϴӻ��Ƿ�ɹ����յ�������,�ӻ�Ӧ����������Ҫ��ʱ�����������ṩ��,Ӧ�������ÿһ���������8������λ���������ŵ�ʱ������,�͵�ƽ0��ʾӦ��,1��ʾ��Ӧ��:

��������

��I2C�����ϴ��͵�ÿλ���ݶ���һ��ʱ���������Ӧ(��ͬ������),����SCL����ʱ�ӵ������,SDA��λ�ش��д���ÿһλ���ݡ�����λ�Ĵ����DZ��ش�����

��������

����������һλһλ����,��������Ҳ��һλһλ���ս���,���Ӧ���źš�

����SPI��

1��ʲô��SPI?

SPI�Ǵ�������ӿ�(Serial Peripheral Interface)����д���� Motorola ��˾�Ƴ���һ��ͬ�����нӿڼ���,��һ�ָ��ٵ�,ȫ˫��,ͬ����ͨ�����ߡ�

2��SPI�ŵ�

֧��ȫ˫��ͨ��

ͨ�ż�

���ݴ������ʿ�

3��ȱ��

û��ָ����������,û��Ӧ�����ȷ���Ƿ���յ�����,���Ը�IIC����Э��Ƚ������ݿɿ�������һ����ȱ�ݡ�

4���ص�

1):���١�ͬ����ȫ˫�����Dz�֡�����ʽ

2):���ӻ�ͨ��ģʽ

5��Э��ͨ��ʱ�����

1):SPI��ͨ��ԭ���ܼ�,�������ӷ�ʽ����,����ģʽͨ����һ�����豸��һ���������豸,��Ҫ����4����,��ʵ��3��Ҳ����(������ʱ)��Ҳ�����л���SPI���豸���е�,������SDI(��������)��SDO(�������)��SCLK(ʱ��)��CS(Ƭѡ)��

(1)SDO/MOSI �C ���豸�������,���豸��������;

(2)SDI/MISO �C ���豸��������,���豸�������;

(3)SCLK �C ʱ���ź�,�����豸����;

(4)CS/SS �C ���豸ʹ���ź�,�����豸���ơ�

���ж�����豸��ʱ��,��Ϊÿ�����豸�϶���һ��Ƭѡ���Ž��뵽���豸����,�����ǵ����豸��ij�����豸ͨ��ʱ����Ҫ�����豸��Ӧ��Ƭѡ���ŵ�ƽ���ͻ��������ߡ�

2):��Ҫ˵������,����SPIͨ����4�ֲ�ͬ��ģʽ,��ͬ�Ĵ��豸�����ڳ����Ǿ�������Ϊij��ģʽ,���Dz��ܸı��;�����ǵ�ͨ��˫�������ǹ�����ͬһģʽ��,�������ǿ��Զ����ǵ����豸��SPIģʽ��������,ͨ��CPOL(ʱ�Ӽ���)��CPHA(ʱ����λ)�������������豸��ͨ��ģʽ,��������:

Mode0:CPOL=0,CPHA=0

Mode1:CPOL=0,CPHA=1

Mode2:CPOL=1,CPHA=0

Mode3:CPOL=1,CPHA=1

ʱ�Ӽ���CPOL����������SCLK�ĵ�ƽ��������״̬ʱ�ǿ���̬������Ч̬,ʱ����λCPHA�������������ݲ������ڵڼ�������:

CPOL=0,��ʾ��SCLK=0ʱ���ڿ���̬,������Ч״̬����SCLK���ڸߵ�ƽʱ

CPOL=1,��ʾ��SCLK=1ʱ���ڿ���̬,������Ч״̬����SCLK���ڵ͵�ƽʱ

CPHA=0,��ʾ���ݲ������ڵ�1������,���ݷ����ڵ�2������

CPHA=1,��ʾ���ݲ������ڵ�2������,���ݷ����ڵ�1������

����:

CPOL=0,CPHA=0:��ʱ����̬ʱ,SCLK���ڵ͵�ƽ,���ݲ������ڵ�1������,Ҳ����SCLK�ɵ͵�ƽ���ߵ�ƽ������,�������ݲ�������������,���ݷ��������½��ء�

CPOL=0,CPHA=1:��ʱ����̬ʱ,SCLK���ڵ͵�ƽ,���ݷ������ڵ�1������,Ҳ����SCLK�ɵ͵�ƽ���ߵ�ƽ������,�������ݲ��������½���,���ݷ������������ء�

CPOL=1,CPHA=0:��ʱ����̬ʱ,SCLK���ڸߵ�ƽ,���ݲɼ����ڵ�1������,Ҳ����SCLK�ɸߵ�ƽ���͵�ƽ������,�������ݲɼ������½���,���ݷ������������ء�

CPOL=1,CPHA=1:��ʱ����̬ʱ,SCLK���ڸߵ�ƽ,���ݷ������ڵ�1������,Ҳ����SCLK�ɸߵ�ƽ���͵�ƽ������,�������ݲɼ�����������,���ݷ��������½��ء�

��Ҫע�����:���ǵ����豸�ܹ�����ʱ��,��Ϊ���ǵ�SPIͨ�Ų�����UART����IICͨ��������ר�ŵ�ͨ������,��ר�ŵ�ͨ����ʼ�ź�,��ר�ŵ�ͨ�Ž����ź�;�������ǵ�SPIЭ���ܹ�ͨ������ʱ���ź���,��û�����ݽ�����ʱ�����ǵ�ʱ����Ҫô�DZ��ָߵ�ƽҪô�DZ��ֵ͵�ƽ��

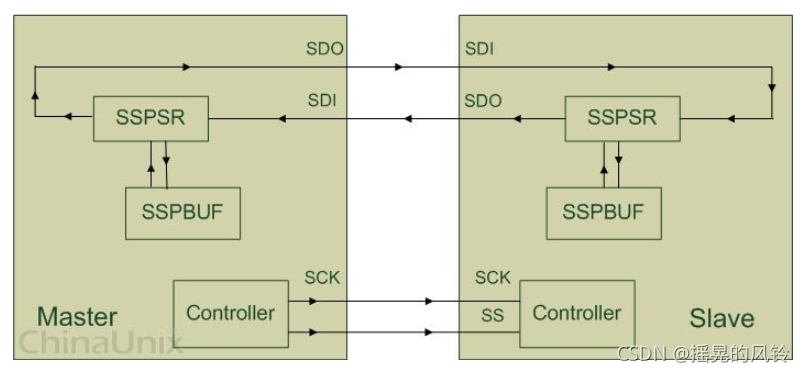

6���ڲ���������

SSPSR �� SPI �豸�ڲ�����λ�Ĵ���(Shift Register). ������Ҫ�����Ǹ��� SPIʱ���ź�״̬, �� SSPBUF ����������Ƴ�����, ÿ���ƶ������ݴ�С�� Bus-Width �Լ� Channel-Width ������.