ЩљУї:БОЮФжЛЖдЩшМЦдРэКЭЙ§ГЬзїДжТдЕФВћЪі,ЯъЯИПЩвдбаОПЮвЬљГіРДЕФЭъећдДДњТы,вВПЩвдЫНаХНЛСїЁЃ

ШєИЩТдЫѕгяНтЪЭ:

FPGA(Field Programmable Gate Array):ЯжГЁПЩБрГЬТпМУХеѓСа

DDS(Direct Digital Synthesizer):жБНгЪ§зжЦЕТЪКЯГЩММЪѕ

ROM(Read-Only Memory):жЛЖСДцДЂЦї

DAC(Digital to Analog Convertor):Ъ§зжФЃФтзЊЛЛЦї

MUX(multiplexer???????):Ъ§ОнбЁдёЦї

???????

вЛЁЂЩшМЦЫМТЗ:

????????DDS(Direct Digital Synthesizer)МДжБНгЪ§зжЦЕТЪКЯГЩММЪѕ,ЦфОпЬхдРэдкетОЭВЛзИЪіСЫ,ВЛСЫНтЕФПЩвдздМКВщдФзЪСЯЁЃ

????????РћгУDDSРДЪЕЯжаХКХЗЂЩњЦї,ЪзЯШОЭЪЧвЊАбВЈаЮЪ§ОнДцдкROMРя,ШЛКѓдкЪБжгаХКХЕФПижЦЯТ,гУROMЕФЕижЗЖдROMРяЕФВЈаЮЪ§ОнНјааВщБэ,ДгЖјНЋROMРяЕФВЈаЮЪ§ОнЖСГі,зюКѓЭЈЙ§DAзЊЛЛЪфГіФЃФтаХКХЕФВЈаЮЁЃ

? ? ? ? вЊЪЕЯжВЈаЮПЩЕї,аХКХЗЂЩњЦїОЭвЊФмЗжЪБЪфГіЖржжВЈаЮ,БОДЮЩшМЦбЁгУСЫ4жжГЃгУЕФФЃФтаХКХ:е§ЯвВЈЁЂОтГнВЈЁЂЗНВЈЁЂШ§НЧВЈ,ФЧУДОЭашвЊ4ИіROMРДЗжБ№ДцДЂ4жжВЈаЮЕФВЈаЮЪ§Он,дкаДVerilogДњТыЪБ,жБНгЕїгУBLOCK ROMЕФIPКЫМДПЩЁЃ

? ? ? ? вЊЪЕЯжВЈЁЂЗљЁЂЦЕЁЂЯрПЩЕї,ОЭашвЊдкЪфШыЖЫВЩгУФГжжЗНЪНРДПижЦВЈаЮЁЂЗљЖШЁЂЦЕТЪКЭЯрЮЛЕФИФБф,етИіЗНЪНПЩвдЪЧАДМќЁЂОиеѓМќХЬЁЂЩЯЮЛЛњЕШЕШ,БОДЮЩшМЦбЁдёзюМђЕЅЕФАДМќЗНЪН(АДЯТЪБЮЊИпЕчЦН):УПДЮАДМќАДЯТЪБ,ИФБфВЈаЮЁЂЗљЖШЁЂЦЕТЪКЭЯрЮЛЁЃМШШЛЪЙгУСЫАДМќ,ФЧУДЮЊСЫЯћГ§АДМќАДЯТКЭЫЩПЊЪБЕФЛњаЕИЩШХ,дкаДVerilogДњТыЪБ,АДМќЯћЖЖФЃПщОЭБиВЛПЩЩйЁЃ

? ? ? ? ЯћЖЖКѓЕФАДМќаХКХНјШывЛИіDDSПижЦФЃПщ,ИУФЃПщИљОнЯргІАДМќЕФДЮЪ§МЦЫуВЈаЮЁЂЗљЖШЁЂЦЕТЪКЭЯрЮЛЕФжЕ(БОДЮЩшМЦПЩЪЕЯжЗљЖШ1ЕН15БЖећЪ§ПЩЕїЁЂЦЕТЪ1ЕН50БЖећЪ§БЖЦЕЁЂЯрЮЛ15ЖШЕФећЪ§БЖПЩЕї),ДгЖјВњЩњ2ЮЛВЈаЮПижЦаХКХЁЂ4ЮЛЗљЖШПижЦаХКХЁЂ6ЮЛЦЕТЪПижЦаХКХЁЂ9ЮЛЯрЮЛПижЦаХКХЁЃетаЉаХКХПижЦROMЕФЕижЗ,ДгЖјПижЦЖдROMРяЕФЪ§ОнЕФЖСВйзїЁЃ

????????зюКѓ,РћгУвЛИі4бЁ1ЕФMUX(гУВЈаЮПижЦаХКХРДзіЕижЗ)МДПЩЪЕЯж12ЮЛЪ§зжВЈаЮЪ§ОнЕФЪфГіЁЃ

????????ИљОнвдЩЯЗжЮі,зїГіБОЩшМЦЙІФмПђЭМШчЭМ1ЫљЪО:

?ЭМ1

? ? ? ? гЩгкЮвИіШЫЕФПЊЗЂАхЩЯУЛгаDAC,ЫљвдУЛгаЩшМЦDACФЃПщ,ВЛЙ§ПЩвддкЗТецЪБ,гУVivadoШэМўздДјЕФЗТецЙЄОпжБНгАб12ЮЛЪ§зжВЈаЮЪфГіЯдЪОЮЊФЃФтаЮЪНОЭФмПДЕНФЃФтВЈаЮЁЃ(етРяЫЕвЛОфVivadoХЃХњ)

ЖўЁЂЩшМЦЙ§ГЬ:

2.1 АДМќЯћЖЖФЃПщ:

2.1.1 ЛљБОдРэ:

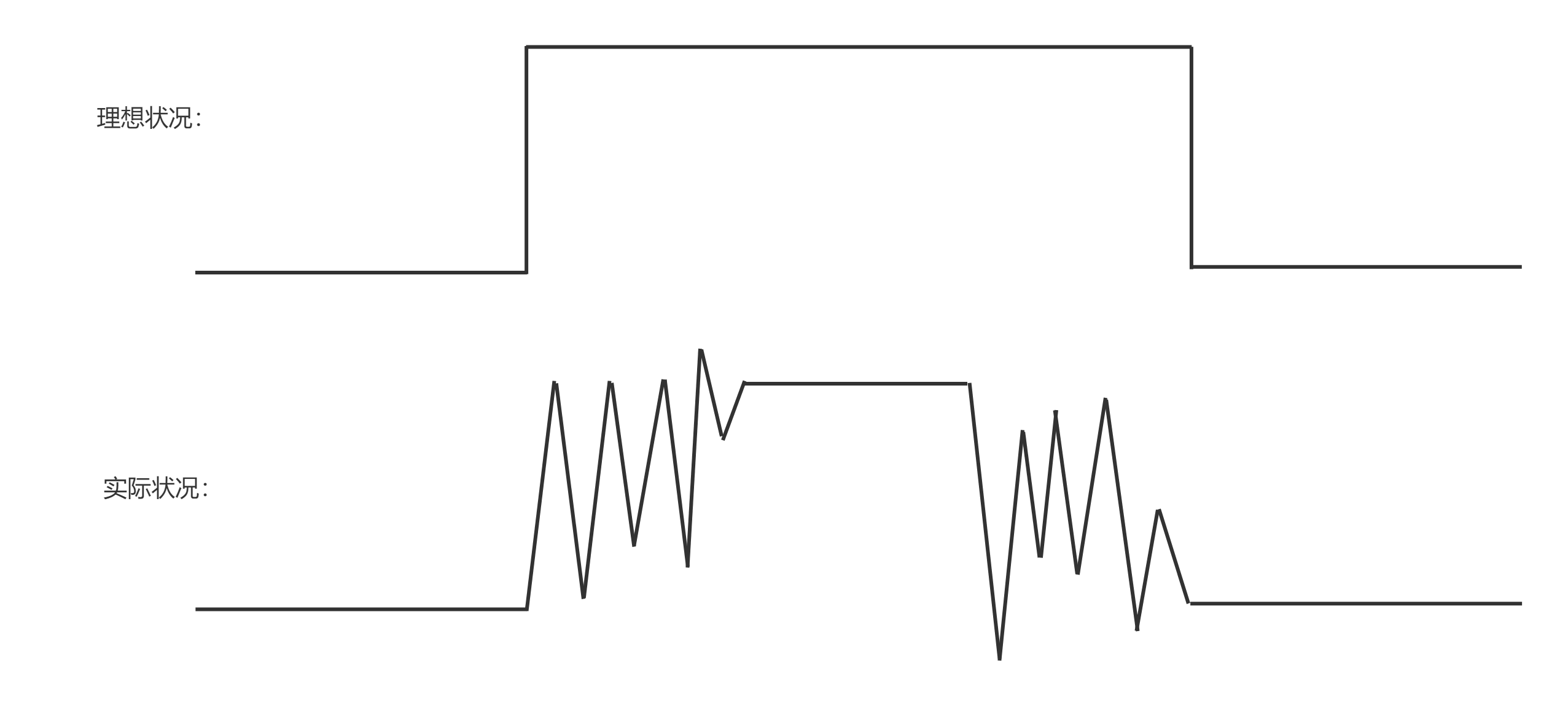

? ? ? ? гЩгкЛњаЕАДМќРягавЛИіИДЮЛЕЏЛЩ,ЯрЕБгквЛИіЧЗзшФсЖўНзеёЕДЯЕЭГ,ОпгавЛЖЈЕФЙпад,ЫљвдЕБАДМќАДЯТКЭЫЩПЊЪБ,ЛсЯШеёЕДвЛЖЮЪБМф,ШЛКѓВХЮШЖЈЕНвЛИіШЗЖЈЕФЕчЦНЁЃЭМ2ЮЊРэЯыКЭЪЕМЪЕФАДМќЕчЦНЪБађЭМ:

?ЭМ2

????????етаЉеёЕДОЭГЦЮЊАДМќЖЖЖЏ,КСЮовЩЮЪ,етжжвтСЯжЎЭтЕФЕчЦНЖЖЖЏЛсЖдТпМдьГЩИЩШХ,БиаыТЫГ§(ЯћЖЖ)ЁЃГЃгУЕФАДМќЯћЖЖЗНЪНгагВМўЯћЖЖКЭШэМўЯћЖЖ,ЧАепЪЧдкАДМќКѓМгвЛИігВМўТЫВЈЕчТЗ,ШчRCЕчТЗЕШЕШ;КѓепЪЧЭЈЙ§РрЫЦжаЖЯЕФЗНЪН,ЕБАДМќАДЯТЛђЫЩПЊЪБ,ЯШОЙ§вЛЖЈЪБМфЕФбгЪБ(вЛАуЮЊ20ms),жЎКѓдйХаЖЯАДМќЕФзДЬЌЪЧЗёвбОЮШЖЈЁЃ

????????БОДЮЩшМЦВЩгУШэМўЯћЖЖ,ВЂРћгУVerilogДњТыБраДзДЬЌЛњРДЪЕЯжЁЃОпЬхЪЧНЋАДМќЯћЖЖЕФећИіЙ§ГЬЗжЮЊ4ИізДЬЌ:

????????зДЬЌS0:МДПеЯаЬЌ,ИУзДЬЌЕШД§АДМќАДЯТ,ШєАДМќАДЯТ,дђЬјзЊЕНS1;ШєАДМќЮДАДЯТ,дђВЛЬјзЊЁЃ

????????зДЬЌS1:ИУзДЬЌдкАДМќАДЯТЪБПижЦвЛИіМЦЪБЦїНјааМЦЪБ,ШєМЦЪБЦїЛЙЮДМЦЕН20ms,АДМќЕчЦНОЭРЕЭ,ЫЕУїВњЩњСЫвЛДЮАДЯТЖЖЖЏ,зДЬЌВЛЬјзЊЧвМЦЪБЦїЧхСу;ШєМЦЪБЦїМЦЕН20ms,АДМќЕчЦНЛЙЮДРЕЭ,ЫЕУїАДЯТвбОЮШЖЈ,МЦЪБЦїЧхСуЧвзДЬЌЬјзЊЕНS2ЁЃ

????????зДЬЌS2:ИУзДЬЌЕШД§АДМќЫЩПЊ,ШєАДМќЫЩПЊ,дђЬјзЊЕНS3;ШєАДМќЮДЫЩПЊ,дђВЛЬјзЊЁЃ

????????зДЬЌS3:ИУзДЬЌдкАДМќЫЩПЊЪБПижЦвЛИіМЦЪБЦїНјааМЦЪБ,ШєМЦЪБЦїЛЙЮДМЦЕН20ms,АДМќЕчЦНОЭРИп,ЫЕУїВњЩњСЫвЛДЮЫЩПЊЖЖЖЏ,зДЬЌВЛЬјзЊЧвМЦЪБЦїЧхСу;ШєМЦЪБЦїМЦЕН20ms,АДМќЕчЦНЛЙЮДРИп,ЫЕУїЫЩПЊвбОЮШЖЈ,МЦЪБЦїЧхСуЧвзДЬЌЬјзЊЕНS0ЁЃ

? ? ? ? ЩЯЪізДЬЌЛњЕФзДЬЌзЊЛЛ,ЪЧгЩАДМќАДЯТЪБВњЩњЕФЩЯЩ§биКЭАДМќЫЩПЊЪБВњЩњЕФЯТНЕбиРДДЅЗЂЕФЁЃвђДЫ,ЪзЯШОЭашвЊВЩМЏетСНИіБпби,БОЩшМЦВЩгУвЛИі2ЮЛМФДцЦїРДЪЕЯжБпбиВЩМЏ,ШчЭМ3:

? ? ЭМ3?

? ? ? ? гЩЩЯЭМПЩжЊ,ШєФГвЛЪБПЬ,D1ЮЊЁА0ЁБЧвD0ЮЊЁА1ЁБ,дђВЩМЏЕНАДМќЪфШыЕФвЛИіЩЯЩ§би;ШєФГвЛЪБПЬ,D1ЮЊЁА1ЁБЧвD0ЮЊЁА0ЁБ,дђВЩМЏЕНАДМќЪфШыЕФвЛИіЯТНЕбиЁЃ

? ? ? ? жСДЫ,ПЩвдЕУЕНАДМќЯћЖЖзДЬЌзЊЛЛЭМШчЭМ4(IКЭOДњБэАДМќЪфШыКЭЯћЖЖЪфГіЕФТпМжЕ):

ЭМ4

2.1.2 ОпЬхУшЪі:

? ? ? ? ИљОнзДЬЌЛњ,ОЭПЩвдгУRTLгябдНЋАДМќЯћЖЖФЃПщУшЪіГіРД,БраДЕФVerilogДњТыШчЯТ,зДЬЌЛњВПЗжВЩгУШ§ЖЮЪНУшЪі:

`timescale 1ms / 1ps

module KEY_filter(

input clk, //50MHzжїЪБжг

input rst, //ИДЮЛаХКХ,ИпЕчЦНгааЇ

input key_in, //ЪфШыЕФАДМќаХКХ,АДЯТЪБЮЊИпЕчЦН

output key_filter //ЯћЖЖКѓЕФАДМќаХКХ

);

reg [1:0] key_test; //АДМќБпбиМьВтМФДцЦї

reg key_filter_R; //ЯћЖЖКѓЕФАДМќаХКХМФДцЦї

/*************МьВтБпби************/

always @ (posedge clk)

key_test <= {key_test[0],key_in};

reg [1:0] c_sta = 2'd0; //ЯжЬЌ

reg [1:0] n_sta = 2'd0; //ДЮЬЌ

reg [19:0] cnt = 20'd0; //МЦЪБЦї

/**********МЦЪБЦїПижЦ**********/

always @ (posedge clk or negedge rst)

begin

if (rst)

cnt <= 20'd0;

else if (cnt == 20'd999999)

cnt <= 20'd0;

else

case (n_sta)

2'd0:cnt <= 20'd0;

2'd1:

begin

if ( (key_test == 2'b10 && cnt < 20'd999999) || (key_test != 2'b10 && cnt == 20'd999999) )

cnt <= 20'd0;

else

cnt <= cnt + 1'd1;

end

2'd2:cnt <= 20'd0;

2'd3:

begin

if ( (key_test == 2'b01 && cnt < 20'd999999) || (key_test != 2'b01 && cnt == 20'd999999) )

cnt <= 20'd0;

else

cnt <= cnt + 1'd1;

end

default:;

endcase

end

/*************зДЬЌЕФзЊЛЛ***********/

always @ (posedge clk or negedge rst)

begin

if (rst)

c_sta <= 2'd0;

else

c_sta <= n_sta;

end

/*************ИїзДЬЌзЊЛЛЬѕМў***********/

always @ (*)

begin

case(c_sta)

2'd0:

begin

if (key_test == 2'b01)

n_sta = 2'd1;

else

n_sta = 2'd0;

end

2'd1:

begin

if (key_test == 2'b10 && cnt < 20'd999999)

n_sta = 2'd1;

else if (key_test != 2'b10 && cnt == 20'd999999)

n_sta = 2'd2;

else

n_sta = 2'd1;

end

2'd2:

begin

if (key_test == 2'b10)

n_sta = 2'd3;

else

n_sta = 2'd2;

end

2'd3:

begin

if (key_test == 2'b01 && cnt < 20'd999999)

n_sta = 2'd2;

else if (key_test != 2'b01 && cnt == 20'd999999)

n_sta = 2'd0;

else

n_sta = 2'd3;

end

default:;

endcase

end

/*************ИїзДЬЌЕФЪфГі***********/

always @ (posedge clk or negedge rst)

begin

if (rst)

key_filter_R <= 1'd0;

else

case (n_sta)

2'd0:key_filter_R <= 1'd0;

2'd2:key_filter_R <= 1'd1;

default:;

endcase

end

/*************ИјЯћЖЖКѓЕФАДМќаХКХИГжЕ***********/

assign key_filter = key_filter_R;

endmodule2.1.3 ЗТецВтЪд:

? ? ? ? БраДЕФtestbeachШчЯТ:

`timescale 1ms / 1ps

module TB_KEY_filter(

);

reg clk; //50MHzжїЪБжг

reg rst; //ИДЮЛаХКХ,ИпЕчЦНгааЇ

reg key_in; //ЪфШыЕФАДМќаХКХ,АДЯТЪБЮЊИпЕчЦН

wire key_filter; //ЯћЖЖКѓЕФАДМќаХКХ

KEY_filter uut_KEY_filter(

.clk(clk), //50MHzжїЪБжг

.rst(rst), //ИДЮЛаХКХ,ИпЕчЦНгааЇ

.key_in(key_in), //ЪфШыЕФАДМќаХКХ,АДЯТЪБЮЊЕЭЕчЦН

.key_filter(key_filter) //ЯћЖЖКѓЕФАДМќаХКХ

);

/**************ВњЩњ50MHzЪБжг**************/

always #0.00001 clk = ~clk;

/**************ЪфШыГѕЪМЛЏ**************/

initial

begin

clk = 1'd0;

rst = 1'd1;

key_in = 1'd0;

/**************АДМќЕквЛДЮАДЯТ**************/

#0.1

rst = 1'd0;

key_in = 1'd1;

/**************ФЃФтАДЯТЪБЕФЖЖЖЏ**************/

#0.1

key_in = 1'd0;

#0.2

key_in = 1'd1;

#0.1

key_in = 1'd0;

#0.2

key_in = 1'd1;

/**************АДМќЕквЛДЮЫЩПЊ**************/

#50

key_in = 1'd0;

/**************ФЃФтЫЩПЊЪБЕФЖЖЖЏ**************/

#0.1

key_in = 1'd1;

#0.1

key_in = 1'd0;

#0.2

key_in = 1'd1;

#0.1

key_in = 1'd0;

end

endmodule? ? ? ? дкVivadoздДјЕФЗТецЦїЩЯХмГіЕФАДМќЯћЖЖФЃПщЗТецНсЙћШчЭМ5жСЭМ8ЫљЪО:

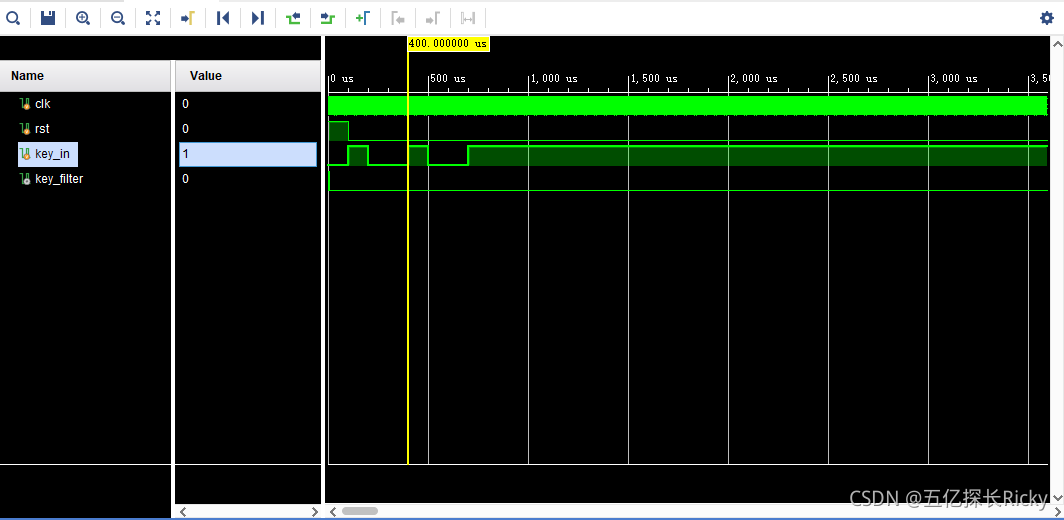

ЭМ5?

? ? ? ? гЩЩЯЭМПЩвдПДЕН,дкАДМќАДЯТЖЖЖЏЦкМф,АДМќЯћЖЖФЃПщЕФЪфГівРШЛЮЊЁА0ЁБЁЃ

ЭМ6?

????????гЩЩЯЭМПЩвдПДЕН,дкАДМќЫЩПЊЖЖЖЏЦкМф,АДМќЯћЖЖФЃПщЕФЪфГівРШЛЮЊЁА1ЁБЁЃ?

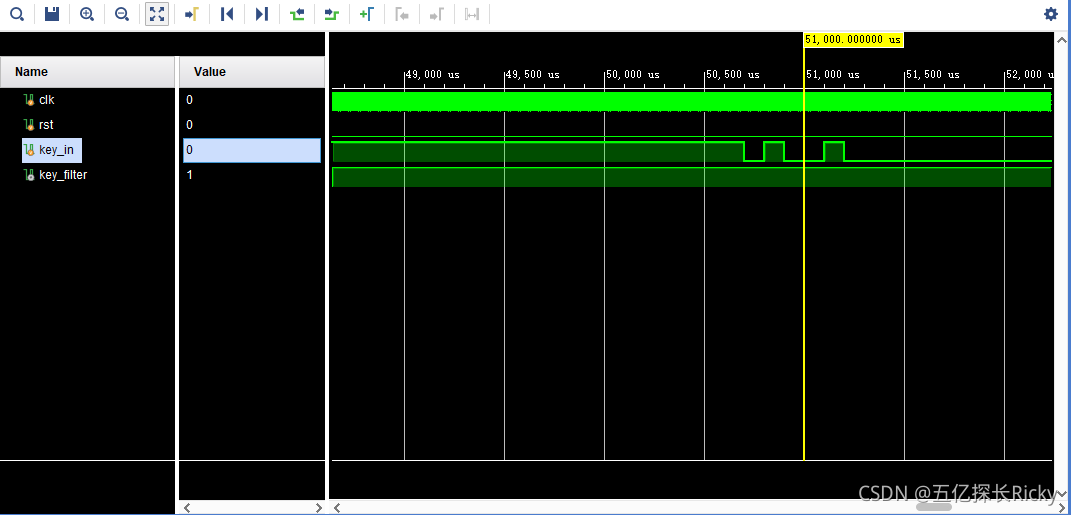

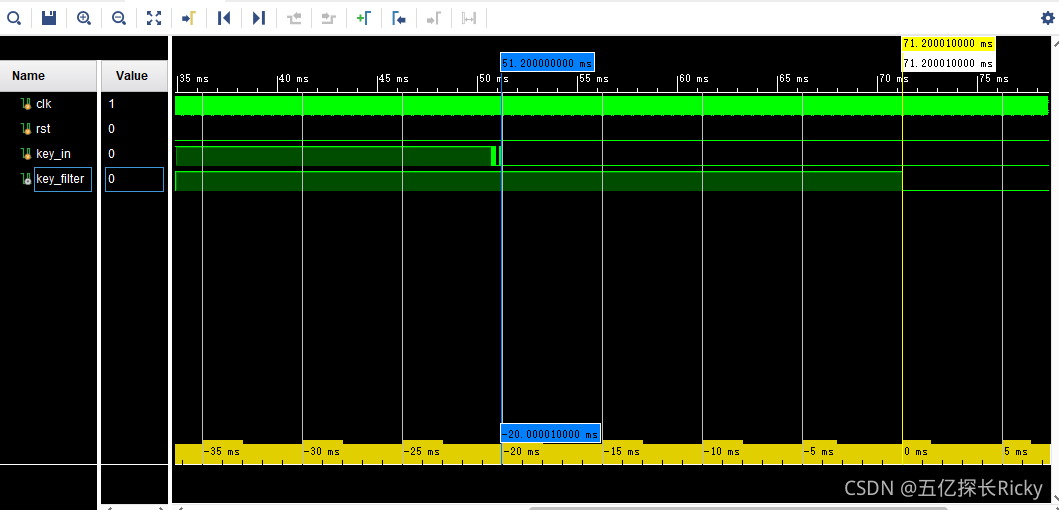

ЭМ7?

????????гЩЩЯЭМПЩвдПДЕН,АДМќАДЯТКѓ,ДгзюКѓвЛДЮЖЖЖЏЕНАДМќЯћЖЖФЃПщЕФЪфГіБфЮЊЁА1ЁБ,жаМфЕФЪБМфОЭЪЧ20msЁЃ? ?

ЭМ8?

????????гЩЩЯЭМПЩвдПДЕН,АДМќЫЩПЊКѓ,ДгзюКѓвЛДЮЖЖЖЏЕНАДМќЯћЖЖФЃПщЕФЪфГіБфЮЊЁА0ЁБ,жаМфЕФЪБМфвВЪЧ20msЁЃ?

? ? ? ? жСДЫ,АДМќЯћЖЖФЃПщЩшМЦГЩЙІЁЃ

2.2?ВЈаЮЪ§ОнЕФДцДЂ:

2.2.1?ЩњГЩCOEЮФМў:

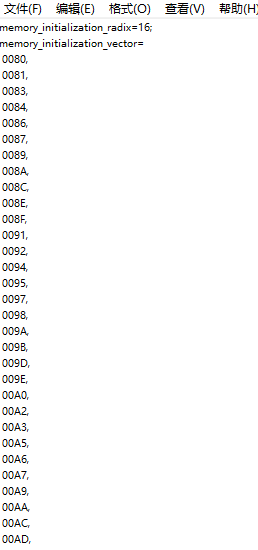

? ? ? ? ЪзЯШвЊЩњГЩУПжжВЈаЮЕФЪ§зжВЈаЮЪ§Он,етПЩвдЪЙгУMATLABЁЂGuagleЕШШэМўЩњГЩвЛИіMIFЮФМўЛђепCOEЮФМўЕФЗНЪНРДЪЕЯжЁЃMIFЮФМўКЭCOEЮФМўЖМЪЧгУРДСаГіДцДЂЦїРяДцЗХЕФЫљгаЪ§ОнЕФЮФМў,ЕЋСНепЕФЮФМўИёЪНВЛЭЌЁЃБОДЮЩшМЦРћгУGuagleШэМўЯШЩњГЩИїжжВЈаЮЕФMIFЮФМў,дйНЋMIFЮФМўИФГЩCOEЮФМў,ЭМ9ЪЧЩњГЩЕФе§ЯвВЈCOEЮФМўЕФвЛВПЗж:

ЭМ9?

2.2.2?ЕїгУBLOCK ROM IPКЫ:

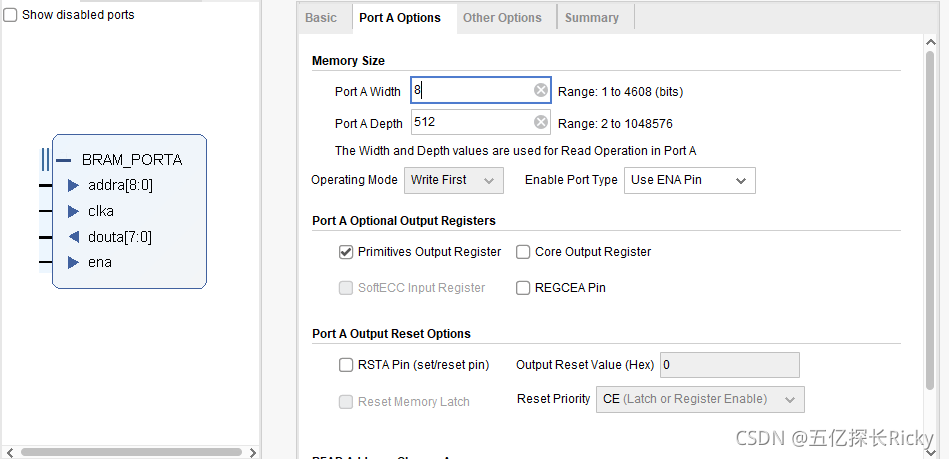

? ? ? ? XilinxЕФFPGAжаОпгаКмЖрВЛЭЌЙІФмЕФIPКЫ,ЕїгУетаЉIPКЫПЩвдДѓДѓЬсИпЩшМЦаЇТЪЁЃЩЯУцЫЕЕН,БОДЮЩшМЦРћгУBLOCK ROMЕФIPКЫРДДцЗХВЈаЮЪ§Он,ОпЬхЪЧЕїгУЪ§ОнПэЖШЮЊ8,Ъ§ОнЩюЖШЮЊ512ЕФЕЅПкROM,IPХфжУШчЭМ10ЫљЪО:

ЭМ10?

? ? ? ? жЎКѓ,НЋЩњГЩЕФВЈаЮCOEЮФМў,ЗХЕНIPКЫРяМДЭъГЩСЫВЈаЮЪ§ОнЕФДцДЂЁЃ

2.3?DDSПижЦФЃПщ:?

2.3.1?ВЈаЮЕїећ:

? ? ? ? ВЈаЮЕїећЪЕЯжЪЧРћгУЪфШыЕФВЈаЮПижЦМќПижЦ2ЮЛВЈаЮПижЦаХКХ,ДгЖјИФБф4жжЪфГіВЈаЮЁЃОпЬхЙ§ГЬЮЊ:ЕБВЈаЮПижЦМќАДЯТЪБ,ВњЩњВЈаЮАДМќЪфШыаХКХ,ИУаХКХОЙ§АДМќЯћЖЖКѓДцШывЛИіБпбиМьВтМФДцЦї(дРэЭЌАДМќБпбиМьВтМФДцЦї),УПЕББпбиМьВтМФДцЦїМьВтЕНвЛИіЩЯЩ§би,ВЈаЮПижЦаХКХОЭМг1,МгЕН3ЪБЧхСу,зюКѓ,ВЈаЮПижЦаХКХдйШЅПижЦвЛИі4бЁ1ЕФЪ§ОнбЁдёЦїМДПЩЪЕЯж4жжЪфГіВЈаЮЕФЕїећЁЃ?

2.3.2?ЗљЖШЕїећ:

? ? ? ? ЪЕЯжЗљЖШЕїећЪЧБШНЯМђЕЅЕФ,жЛашРћгУвЛИіГЫЗЈЦї,АбВЈаЮЪфГіЯШГЫЩЯвЛИіЗХДѓБЖЪ§дйЪфГіМДПЩЁЃЕЋВЩгУетжжЗНЪНжЛФмЪЕЯжЗХДѓБЖЪ§НЯЕЭЕФЗХДѓ,вђЮЊЫцзХЗХДѓБЖЪ§ЕФдіМг,ЪфГіЕФЮЛПэЪЦБивВЛсдіМг,ВЛЙ§дкЪЕМЪгІгУжа,ПЩвддкБОЩшМЦЕФЪфГіЖЫМгЩЯФЃФтЗХДѓЦї,ДгЖјЪЕЯжИпдівцЗХДѓЁЃБОЩшМЦФмЪЕЯжЕФзюИпдівцЪЧ15БЖ,ЖјдкROMРяДцЗХЕФ8ЮЛВЈаЮЪ§ОнзюДѓЮЊЁА0xFFЁБ,ЙЪВЈаЮЪфГіЕФзюДѓЪ§ОнЮЊЁА0xEF1ЁБ,ЙЪВЈаЮЪфГіЮЛПэгІИУЮЊ12ЮЛЁЃ?

????????ОпЬхЙ§ГЬЮЊ:ЕБЗљЖШПижЦМќАДЯТЪБ,ВњЩњЗљЖШАДМќЪфШыаХКХ,ИУаХКХОЙ§АДМќЯћЖЖКѓДцШывЛИіЗљЖШБпбиМьВтМФДцЦї,УПЕБМьВтЕНвЛИіЩЯЩ§би,ЗљЖШПижЦаХКХОЭМг1,МгЕН15ЪБЧхСу,зюКѓ,УПИіДгROMРяЪфГіЕФВЈаЮЪ§ОнГЫЩЯЗљЖШПижЦаХКХМДЪЕЯжЗљЖШЕїећЁЃ

2.3.3?ЯрЮЛЕїећ:

? ? ? ? гЩгкДцЗХдкROMРяЕФВЈаЮЪ§ОнЪЧ512ИіРыЩЂЕФЪ§ОнЕу,ШєДгЕижЗЮЊ0ЕФЪ§ОнПЊЪМЪфГі,ФЧУДЪфГіЕФВЈаЮЯрЮЛОЭЮЊ0Ёу,гЩДЫВЛФбЯыЕН,жЛвЊИФБфROMЕФГѕЪМЪфГіЕижЗ,ОЭФмЪЕЯжЯрЮЛЕїећЁЃ

????????ЩшашвЊВњЩњЕФЯрвЦЮЊNЁу,дђЖдгІЕФЯрЮЛПижЦаХКХPЮЊ:

? ? ? ? ЛљгквдЩЯЫуЗЈ,БОЩшМЦЪЕЯжЯрЮЛ15ЁуЕФећЪ§БЖПЩЕї,ФЧУДУПДЮВњЩњЕФЯрЮЛПижЦаХКХОЭгІИУЮЊ21ЕФећЪ§БЖ,ОпЬхЙ§ГЬЮЊ:ЕБЯрЮЛПижЦМќАДЯТЪБ,ВњЩњЯрЮЛАДМќЪфШыаХКХ,ИУаХКХОЙ§АДМќЯћЖЖКѓДцШывЛИіЯрЮЛБпбиМьВтМФДцЦї,УПЕБМьВтЕНвЛИіЩЯЩ§би,ЯрЮЛПижЦаХКХОЭМг21,МгЕН504ЪБЧхСу,ШЛКѓНЋдРДЕФROMГѕЪМЪфГіЕижЗИГжЕЮЊаТЕФЯрЮЛПижЦаХКХ,ДгЖјЪЕЯжЯрЮЛЕїећЁЃ

2.3.4?ЦЕТЪЕїећ:

? ? ? ? РћгУВЈаЮЪ§ОнЕФРыЩЂад,вВФмЪЕЯжЦЕТЪЕїећЁЃдквЛЖЈЕФГѕЪМЪфГіЕижЗЯТ,ШєУПМфИєвЛИіЪ§ОнЕуЪфГівЛДЮ,ФЧУДЪфГіЕФВЈаЮЦЕТЪОЭЮЊдРДЕФ2БЖ,вРДЫРрЭЦ,жЛвЊИФБфROMЪ§ОнВЩбљЕФМфИє,ОЭФмЪЕЯжЦЕТЪЕїећЁЃЕЋЪЧ,ИљОнФЮПќЫЙЬиВЩбљЖЈРэ(ВЩбљЦЕТЪБиаыДѓгкЕШгкБЛВЩбљаХКХзюИпЦЕТЪЕФ2БЖ,ЗёдђВЩбљКѓаХКХЛсЪЇец),ВЩбљМфИєВЛПЩФмЮоЯодіДѓЁЃ

????????БОДЮЩшМЦЪЕЯжЦЕТЪ1ЕН50БЖећЪ§БЖЦЕЁЃОпЬхЙ§ГЬЮЊ:ЕБЦЕТЪПижЦМќАДЯТЪБ,ВњЩњЦЕТЪАДМќЪфШыаХКХ,ИУаХКХОЙ§АДМќЯћЖЖКѓДцШывЛИіЦЕТЪБпбиМьВтМФДцЦї,УПЕБМьВтЕНвЛИіЩЯЩ§би,ЦЕТЪПижЦаХКХОЭМг1,МгЕН50ЪБЧхСу,ШЛКѓдкжїЪБжгЕФПижЦЯТ,УПДЮжїЪБжгЕНРД,дРДЕФROMГѕЪМЪфГіЕижЗОЭдіМгвЛИіЦЕТЪПижЦаХКХ,ДгЖјЪЕЯжЦЕТЪЕїећЁЃ

? ? ? ? ?злЩЯ,УПДЮжїЪБжгЕНРД,ROMЕижЗWЕФЫуЗЈЮЊ(W1ЮЊЩЯвЛЪБПЬЕФЕижЗ,PЮЊЯрЮЛПижЦаХКХ,FЮЊЦЕТЪПижЦаХКХ):

2.4?ЖЅВуУшЪі:

? ? ? ? ИљОнвдЩЯЕФЩшМЦЫМТЗ,БраДЕФVerilogЖЅВуДњТыШчЯТ:

`timescale 1ms / 1ps

module DDS_top(

input clk, //50MHzжїЪБжг

input rst, //ИДЮЛаХКХ,ИпЕчЦНгааЇ

input W_ctrl, //ВЈаЮПижЦМќ

input A_ctrl, //ЗљЖШПижЦМќ

input P_ctrl, //ЯрЮЛПижЦМќ

input F_ctrl, //ЦЕТЪПижЦМќ

output reg [11:0] wave_out //ВЈаЮЪфГіаХКХ

);

wire W_ctrl_key; //ЯћЖЖКѓЕФВЈаЮПижЦМќ

wire A_ctrl_key; //ЯћЖЖКѓЕФЗљЖШПижЦМќ

wire P_ctrl_key; //ЯћЖЖКѓЕФЯрЮЛПижЦМќ

wire F_ctrl_key; //ЯћЖЖКѓЕФЦЕТЪПижЦМќ

wire [7:0] wave_sin; //е§ЯвВЈЪфГіаХКХ

wire [7:0] wave_Sawtooth; //ОтГнВЈЪфГіаХКХ

wire [7:0] wave_square; //ЗНВЈЪфГіаХКХ

wire [7:0] wave_Triangular; //Ш§НЧВЈЪфГіаХКХ

reg [1:0] r_M; //ВЈаЮБпбиМьВтМФДцЦї

reg [1:0] r_A; //ЗљЖШБпбиМьВтМФДцЦї

reg [1:0] r_P; //ЯрЮЛБпбиМьВтМФДцЦї

reg [1:0] r_F; //ЦЕТЪБпбиМьВтМФДцЦї

reg [1:0] WAVE = 2'd0; //ВЈаЮПижЦаХКХ,ЪЕЯжЪфГіВЈаЮЯрЮЛГЌЧА15ЖШЕФећЪ§БЖПЩЕї

reg [3:0] AMPLITUDE = 4'd1; //ЗљжЕПижЦаХКХ,ЪЕЯжЪфГіВЈаЮЗљжЕ1ЕН15ећЪ§БЖПЩЕї

reg [8:0] PHASE = 9'd0; //ЯрЮЛПижЦаХКХ,ЪЕЯжЪфГіВЈаЮЯрЮЛГЌЧА15ЖШЕФећЪ§БЖПЩЕї

reg [5:0] FREQUENCY = 6'd1; //ЦЕТЪПижЦаХКХ,ЪЕЯжЪфГіВЈаЮЦЕТЪБЖЦЕ1ЕН50БЖећЪ§ПЩЕї

reg [8:0] wave_add = 9'd0; //ВЈаЮЪ§ОнЕФЕижЗ

/*****************ЕїгУАДМќЯћЖЖФЃПщЪЕЯжВЈаЮбЁдёаХКХЯћЖЖ*****************/

KEY_filter key_WAVE(

.key_filter (W_ctrl_key),

.clk (clk),

.rst (rst),

.key_in (W_ctrl)

);

/*****************ЕїгУАДМќЯћЖЖФЃПщЪЕЯжЗљЖШПижЦзжЯћЖЖ*****************/

KEY_filter key_AMPLITUDE(

.key_filter (A_ctrl_key),

.clk (clk),

.rst (rst),

.key_in (A_ctrl)

);

/*****************ЕїгУАДМќЯћЖЖФЃПщЪЕЯжЯрЮЛПижЦзжЯћЖЖ*****************/

KEY_filter key_PHASE(

.key_filter (P_ctrl_key),

.clk (clk),

.rst (rst),

.key_in (P_ctrl)

);

/*****************ЕїгУАДМќЯћЖЖФЃПщЪЕЯжЦЕТЪПижЦзжЯћЖЖ*****************/

KEY_filter key_FREQUENCY(

.key_filter (F_ctrl_key),

.clk (clk),

.rst (rst),

.key_in (F_ctrl)

);

/*****************ВЈаЮБпбиМьВт*****************/

always @ (posedge clk)

r_M <= {r_M[0],W_ctrl_key};

/*****************ЗљЖШБпбиМьВт*****************/

always @ (posedge clk)

r_A <= {r_A[0],A_ctrl_key};

/*****************ЯрЮЛБпбиМьВт*****************/

always @ (posedge clk)

r_P <= {r_P[0],P_ctrl_key};

/*****************ЦЕТЪБпбиМьВт*****************/

always @ (posedge clk)

r_F <= {r_F[0],F_ctrl_key};

/*****************ВЈаЮПижЦ*****************/

always @ (posedge clk or negedge rst)

begin

if (rst)

WAVE <= 2'd0;

else if (r_M == 2'b01)

if (WAVE == 2'd3)

WAVE <= 2'd0;

else

WAVE <= WAVE + 1'b1;

else

WAVE <= WAVE;

end

/*****************ЗљЖШПижЦ*****************/

always @ (posedge clk or negedge rst)

begin

if (rst)

AMPLITUDE <= 6'd1;

else if (r_A == 2'b01)

if (AMPLITUDE == 4'd15)

AMPLITUDE <= 6'd1;

else

AMPLITUDE <= AMPLITUDE + 1'b1;

else

AMPLITUDE <= AMPLITUDE;

end

/*****************ЯрЮЛКЭЕижЗПижЦ*****************/

always @ (posedge clk or negedge rst)

begin

if (rst)

begin

PHASE <= 9'd0;

wave_add <= 9'd0;

end

else if (r_P == 2'b01)

if (PHASE == 9'd504)

PHASE <= 9'd0;

else

begin

PHASE = PHASE + 15*511/360;

wave_add = PHASE;

end

else

begin

PHASE <= PHASE;

wave_add <= wave_add + FREQUENCY;

end

end

/*****************ЦЕТЪПижЦ*****************/

always @ (posedge clk or negedge rst)

begin

if (rst)

FREQUENCY <= 6'd1;

else if (r_F == 2'b01)

if (FREQUENCY == 6'd50)

FREQUENCY <= 6'd1;

else

FREQUENCY <= FREQUENCY + 1'b1;

else

FREQUENCY <= FREQUENCY;

end

/*****************ЪфГіВЈаЮ*****************/

always @ (posedge clk)

begin

case (WAVE)

2'd0:wave_out <= wave_sin * AMPLITUDE;

2'd1:wave_out <= wave_Sawtooth * AMPLITUDE;

2'd2:wave_out <= wave_square * AMPLITUDE;

2'd3:wave_out <= wave_Triangular * AMPLITUDE;

default:wave_out <= 12'd0;

endcase

end

/*****************ЕїгУе§ЯвВЈПщROM*****************/

sin u1 (

.clka(clk),

.ena(1'd1),

.addra(wave_add),

.douta(wave_sin)

);

/*****************ЕїгУОтГнВЈПщROM*****************/

Sawtooth u2 (

.clka(clk),

.ena(1'd1),

.addra(wave_add),

.douta(wave_Sawtooth)

);

/*****************ЕїгУЗНВЈПщROM*****************/

square u3 (

.clka(clk),

.ena(1'd1),

.addra(wave_add),

.douta(wave_square)

);

/*****************ЕїгУШ§НЧВЈПщROM*****************/

Triangular u4 (

.clka(clk),

.ena(1'd1),

.addra(wave_add),

.douta(wave_Triangular)

);

endmodule2.5?ЖЅВуЗТецВтЪд:

? ? ? ? БраДЕФtestbeachШчЯТ:

`timescale 1ms / 1ps

module TB_DDS_top(

);

reg clk; //ЯЕЭГжїЪБжг

reg rst; //ИДЮЛаХКХ,ИпЕчЦНгааЇ

reg W_ctrl; //ВЈаЮПижЦМќ

reg A_ctrl; //ЗљЖШПижЦМќ

reg P_ctrl; //ЯрЮЛПижЦМќ

reg F_ctrl; //ЦЕТЪПижЦМќ

wire [11:0] wave_out; //ВЈаЮЪфГіаХКХ

/**************ФЃПщР§ЛЏ**************/

DDS_top TB_UUT(

.clk(clk),

.rst(rst),

.W_ctrl(W_ctrl),

.wave_out(wave_out),

.A_ctrl(A_ctrl),

.P_ctrl(P_ctrl),

.F_ctrl(F_ctrl)

);

/**************ВњЩњ50MHzЪБжг**************/

always #0.00001 clk = ~clk;

/**************ЪфШыГѕЪМЛЏ**************/

initial

begin

clk = 1'd0;

rst = 1'd0;

W_ctrl = 1'd0;

A_ctrl = 1'd0;

P_ctrl = 1'd0;

F_ctrl = 1'd0;

/**************4ИіПижЦМќЕквЛДЮАДЯТ**************/

#1

W_ctrl = 1'd1;

A_ctrl = 1'd1;

P_ctrl = 1'd1;

F_ctrl = 1'd1;

/**************4ИіПижЦМќЕквЛДЮЫЩПЊ**************/

#21

W_ctrl = 1'd0;

A_ctrl = 1'd0;

P_ctrl = 1'd0;

F_ctrl = 1'd0;

/**************4ИіПижЦМќЕкЖўДЮАДЯТ**************/

#21

W_ctrl = 1'd1;

A_ctrl = 1'd1;

P_ctrl = 1'd1;

F_ctrl = 1'd1;

/**************4ИіПижЦМќЕкЖўДЮЫЩПЊ**************/

#21

W_ctrl = 1'd0;

A_ctrl = 1'd0;

P_ctrl = 1'd0;

F_ctrl = 1'd0;

/**************4ИіПижЦМќЕкШ§ДЮАДЯТ**************/

#21

W_ctrl = 1'd1;

A_ctrl = 1'd1;

P_ctrl = 1'd1;

F_ctrl = 1'd1;

/**************4ИіПижЦМќЕкШ§ДЮЫЩПЊ**************/

#21

W_ctrl = 1'd0;

A_ctrl = 1'd0;

P_ctrl = 1'd0;

F_ctrl = 1'd0;

/**************4ИіПижЦМќЕкЫФДЮАДЯТ**************/

#21

W_ctrl = 1'd1;

A_ctrl = 1'd1;

P_ctrl = 1'd1;

F_ctrl = 1'd1;

/**************4ИіПижЦМќЕкЫФДЮЫЩПЊ**************/

#21

W_ctrl = 1'd0;

A_ctrl = 1'd0;

P_ctrl = 1'd0;

F_ctrl = 1'd0;

end

endmodule? ? ? ? ЖЅВуЗТецНсЙћШчЭМ11жСЭМ15ЫљЪО:?

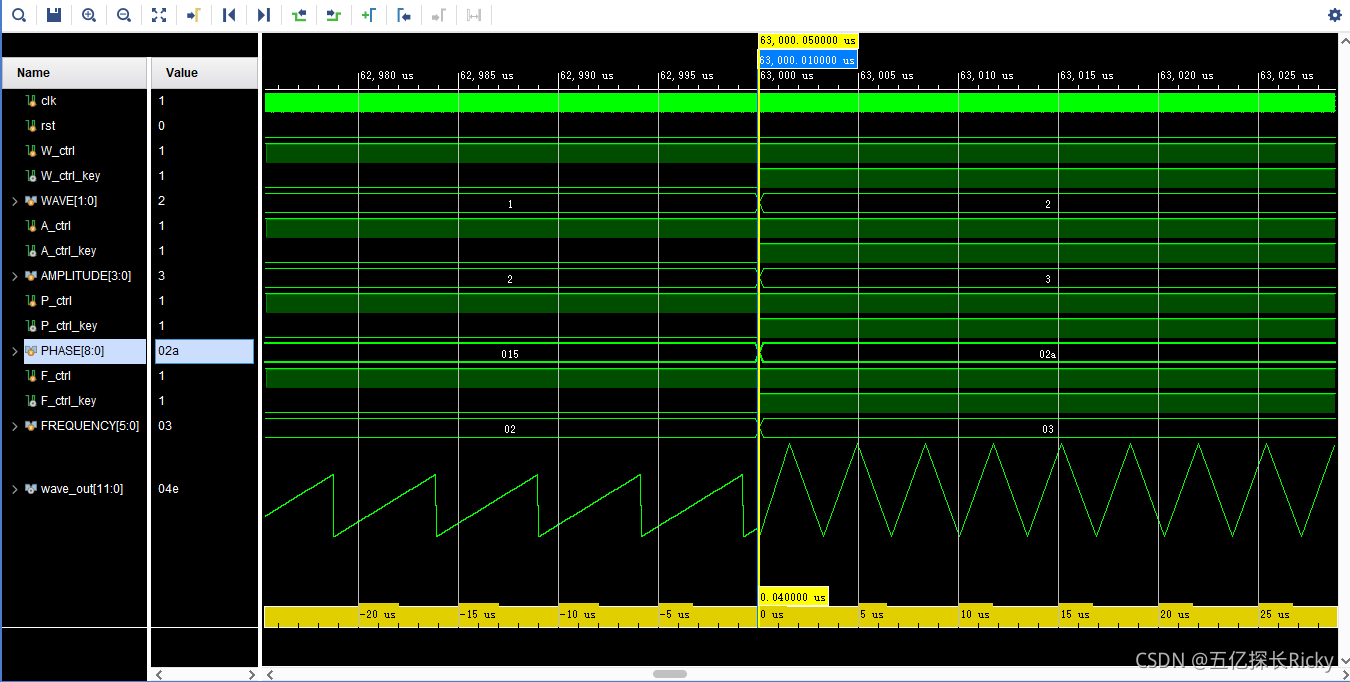

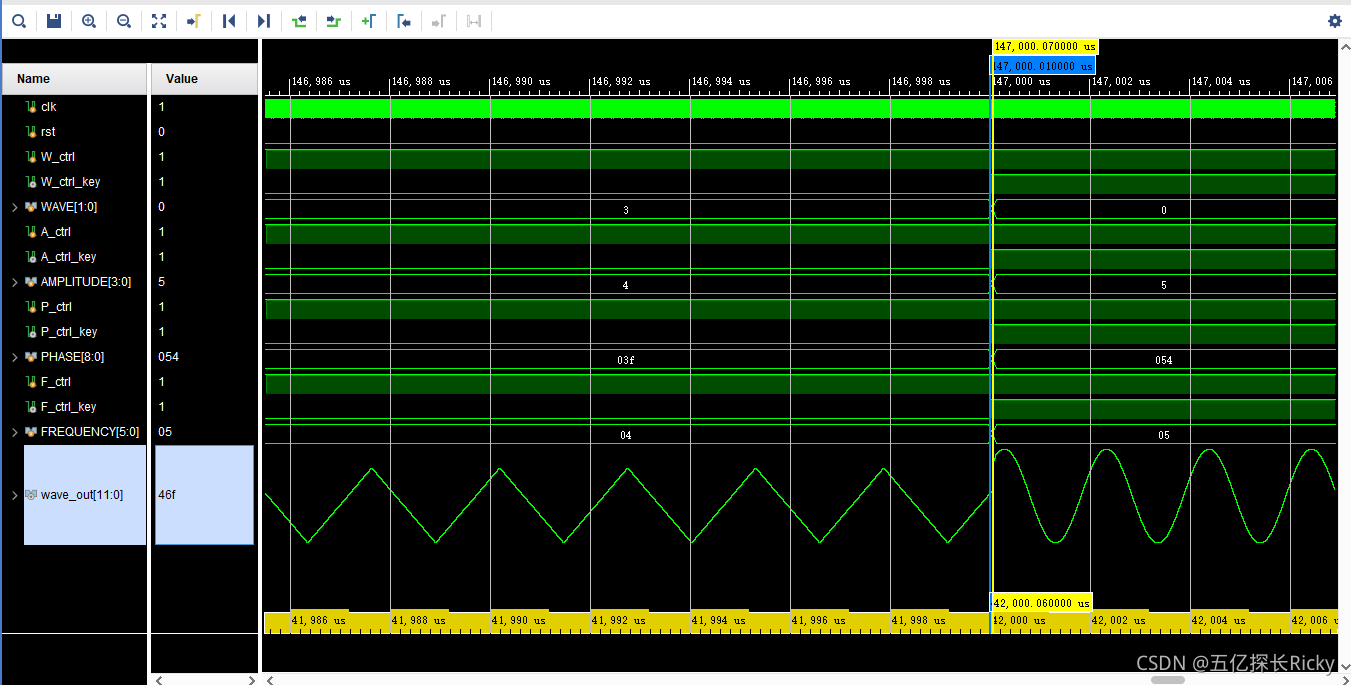

ЭМ11?

? ? ? ? гЩЩЯЭМПЩвдПДЕН,ЕБ4ИіПижЦМќЕквЛДЮАДЯТЪБ,ВЈаЮгЩе§ЯвВЈБфЮЊОтГнВЈ,ЭЌЪБЯрвЦ15Ёу,БЖЦЕ2БЖ,ЗљЖШЗХДѓ2БЖЁЃ

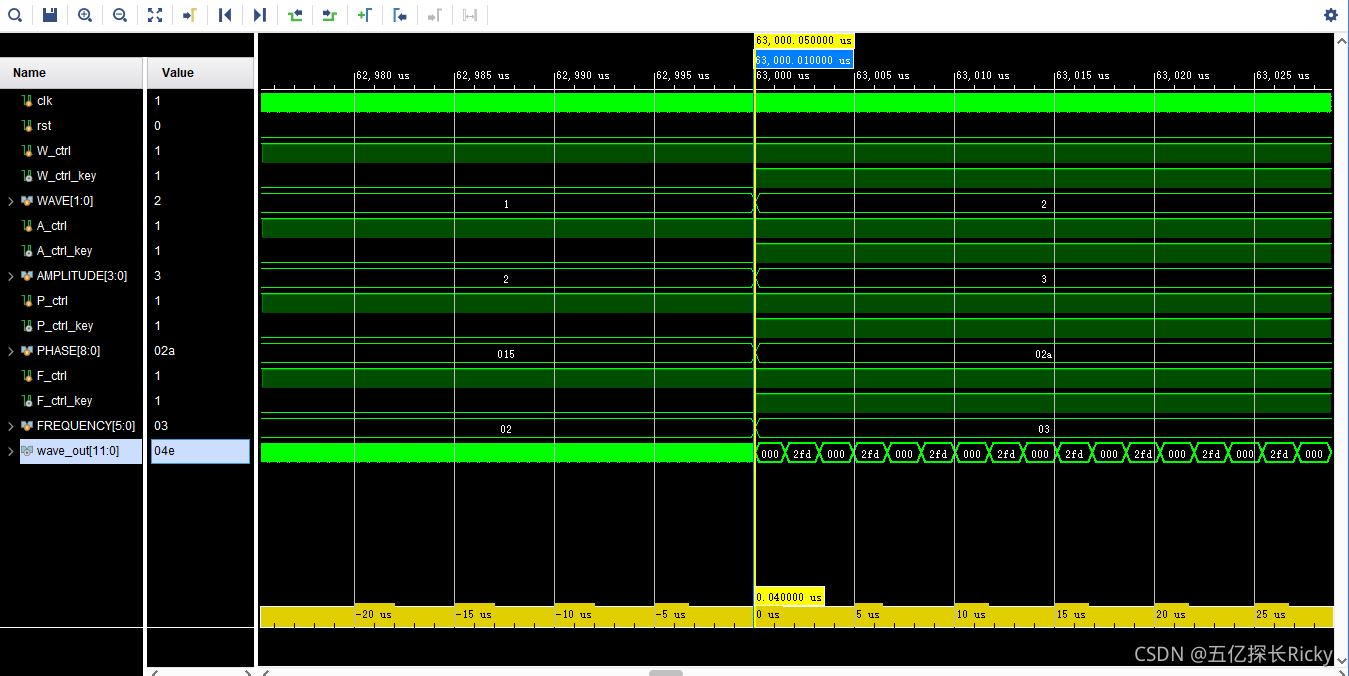

ЭМ12?

????????гЩЩЯЭМПЩвдПДЕН,ЕБ4ИіПижЦМќЕкЖўДЮАДЯТЪБ,ВЈаЮгЩОтГнВЈБфЮЊЗНВЈ(ЭМжаФЃФтВЈаЮЯдЪОЕФЪЧШ§НЧВЈ,ЕЋЪЧИљОнЭМ13ЫљЪО,зЊЮЊЪ§зжЯдЪОКѓШЗЪЕЪЧЗНВЈЕФВЈаЮЪ§Он,ЫљвддкетРяЮвЛГвЩгІИУЪЧVivadoЗТецЦїЗжБцТЪЕФЮЪЬт),ЭЌЪБЯрНЯвЛПЊЪМЕФе§ЯвВЈ,ЯрвЦ30Ёу,БЖЦЕ3БЖ,ЗљЖШЗХДѓ3БЖЁЃ

ЭМ13?

ЭМ14?

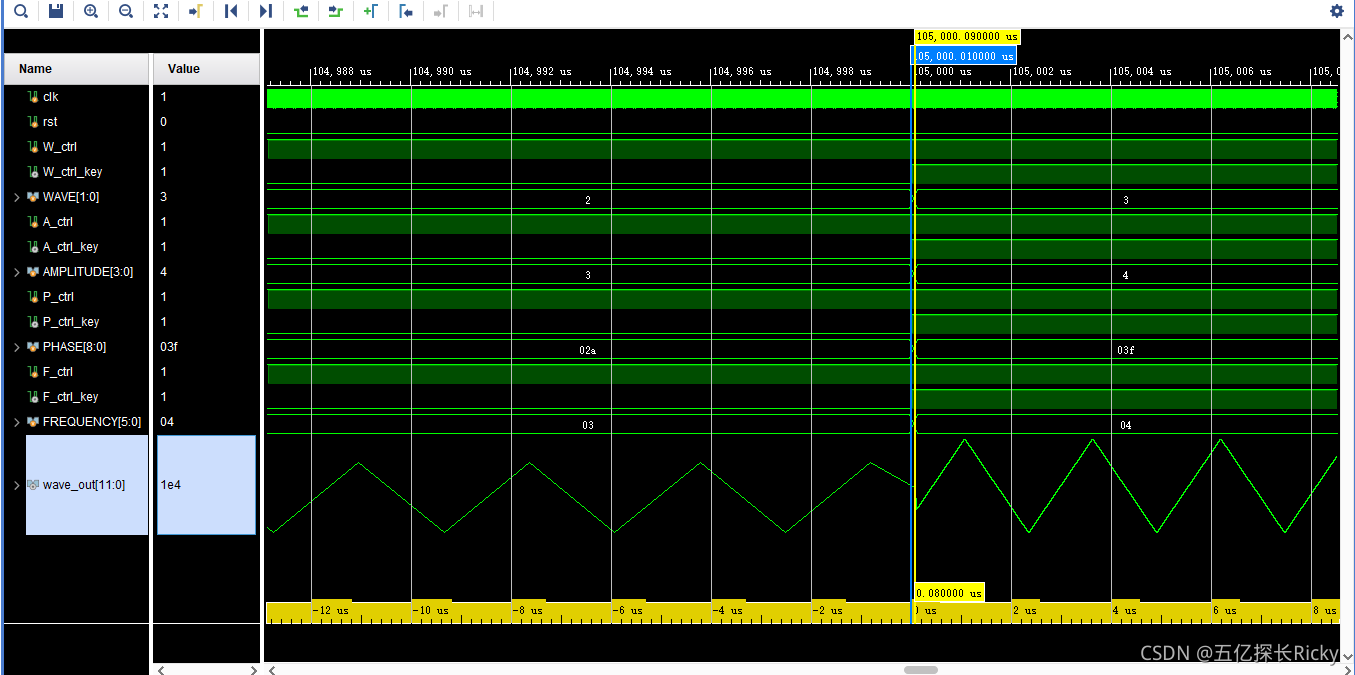

????????гЩЩЯЭМПЩвдПДЕН,ЕБ4ИіПижЦМќЕкШ§ДЮАДЯТЪБ,ВЈаЮгЩЗНВЈБфЮЊШ§НЧВЈ,ЭЌЪБЯрНЯвЛПЊЪМЕФе§ЯвВЈ,ЯрвЦ45Ёу,БЖЦЕ4БЖ,ЗљЖШЗХДѓ4БЖЁЃ

ЭМ15?

????????гЩЩЯЭМПЩвдПДЕН,ЕБ4ИіПижЦМќЕкЫФДЮАДЯТЪБ,ВЈаЮгЩШ§НЧВЈБфЛие§ЯвВЈ,ЭЌЪБЯрНЯвЛПЊЪМЕФе§ЯвВЈ,ЯрвЦ60Ёу,БЖЦЕ5БЖ,ЗљЖШЗХДѓ5БЖЁЃ

? ? ? ? жСДЫ,ећИіЩшМЦЭъГЩЁЃ