近些年,CPU等通用处理器的性能提升速度放缓,为了继续满足各行各业对高能效计算日益增长的需求,以FPGA,GPU,DSP,ASIC,NPU等为代表的异构算例,一夜之间在众多的新型热点领域受到广泛关注。

首先结合市面上能够看到的具体的产品来展示这些异构核之间的不同。

CPU、GPU 都属于冯・诺依曼结构,指令译码执行、共享内存。冯氏结构中,由于执行单元(如 CPU 核)可能执行任意指令,就需要有指令存储器、译码器、各种指令的运算器、分支跳转处理逻辑。由于指令流的控制逻辑复杂,不可能有太多条独立的指令流,因此 GPU 使用 SIMD(单指令流多数据流)来让多个执行单元以同样的步调处理不同的数据,CPU 也支持 SIMD 指令,但SIMD指令的支持只能算是CPU的一个锦上添花的功能,不构成CPU的主要功能,比如X86的SSE,MIPS/RISCV的向量指令,以及ARM 的NEON,都是CPU的可配置功能。

FPGA 之所以比 CPU 甚至 GPU 能效高,本质上是无指令、无需共享内存的体系结构带来的福利,?FPGA 每个逻辑单元的功能在重编程(烧写)时就已经确定,不需要指令。

谷歌发布的人工智能芯片:Tensor Processing Unit(TPU),这是ASIC,TPU兼具了CPU与ASIC的特点,可编程,高效率,低能耗,还有多种多样的各类用于CNN深度学习的NPU,它们也都可以归为ASIC的一种。

DSP有些类似于CPU,但是它拥有更强的并行计算能力,支持多发射,VLIW指令以及单精度,双精度浮点运算和专门用于SIMD加速的MAC阵列等,使其能耗比远高于CPU。?

GPU的峰值性能要高于FPGA,PPA,性能功耗比也要更优一些,FPGA基本单元的计算能力有限。为了实现可重构特性,FPGA 内部有大量极细粒度的基本单元,但是每个单元的计算能力(主要依靠LUT 查找表)都远远低于CPU 和GPU 中的ALU模块,单位面积的功耗高,算力弱于GPU,价格高,PPA没有优势。

FPGA的强项是能够实现可重构计算。

总体上看,各类异构芯片品类各有优劣,短时间内谁也替代不了谁,处于共存竞争的局面。

下面从软件角度,分析几类适用于异构芯片的并行处理方案。

1.CUDA

CUDA是一种新的操作GPU计算的硬件和软件架构,它将GPU视作一个数据并行计算设备,而且无需把这些计算映射到图形API,GPU 编程早期被称为?通用GPU编程(General-popuse GPU programing,GPGPU),这一时期的程序员借助 Direct3D 和 OpenGL 的图形 API 通过迷惑图形硬件来执行非图形的计算任务。CUDA (自2007年)的出现改变了这一切。

CUDA的架构如下图所示:

CUDA在软件方面组成有:一个CUDA库、一个应用程序编程接口(API)及其运行库(Runtime)、几个较高级别的通用数学库,即CUFFT,CUDANN和CUBLAS。CUDA改进了DRAM的读写灵活性,使得GPU与CPU的机制相吻合。另一方面,CUDA提供了片上(on-chip)共享内存,使得线程之间可以共享数据。应用程序可以利用共享内存来减少DRAM的数据传送,更少的依赖DRAM的内存带宽。

CUDA程序构架分为两部分:Host和Device。一般而言,Host指的是CPU,Device指的是GPU。在CUDA程序构架中,主程序还是由CPU 来执行,而当遇到数据并行处理的部分,CUDA 就会将程序编译成 GPU能执行的程序,并传送到GPU。而这个程序在CUDA里称做核(kernel)。CUDA允许程序员定义称为核的C语言函数,从而扩展了C语言,在调用此类函数时,它将由N个不同的CUDA线程并行执行N次,这与普通的C语言函数只执行一次的方式不同。执行核的每个线程都会被分配一个独特的线程ID,可通过内置的threadIdx变量在内核中访问此ID。在 CUDA 程序中,主程序在调用任何 GPU内核之前,必须对核进行执行配置,即确定线程块数和每个线程块中的线程数以及共享内存大小。

关于CUDA的编程例子,可以参考这篇博客:

采用这种方式进行计算加速的项目有比如darknet,在darknet/Makefile中通过开启GPU=1,CUDNN=1来进行计算加速。

![]()

?2.OpenMP(AVX)

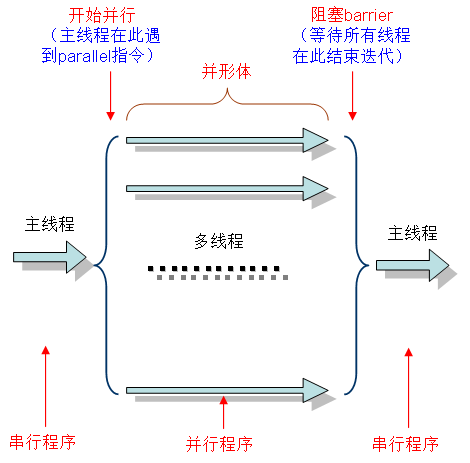

OpenMP是用来对CPU计算进行加速的机制,penMP采用fork-join的执行模式。开始的时候只存在一个主线程,当需要进行并行计算的时候,派生出若干个分支线程来执行并行任务。当并行代码执行完成之后,分支线程会合,并把控制流程交给单独的主线程。

一个典型的fork-join执行模型的示意图如下:

OpenMP编程模型以线程为基础,通过编译Directive指令指导并行化,有三种编程要素可以实现并行化控制,他们分别是编译directive、API函数集和环境变量。

OpenMP具体使用可以参考这篇文章:GCC使用OpenMP_tugouxp的专栏-CSDN博客![]() https://blog.csdn.net/tugouxp/article/details/119210576

https://blog.csdn.net/tugouxp/article/details/119210576

3.SIMD(vector,neon)

这种方式是利用CPU,DSP中的专用VFP,SRAM硬件,在ISA层实现的加速指令。

4.NN Library.

这是比较常见的一种加速实现机制,比如CMSIS NN,BLAS,cudaNN等机制加速。