����M263KIAAEоƬ

- 1,PDMA

- 2,SPI

- 3,EPWM

- 4,I^2^C����

- 5,SysTick(System Timer)

- 6,UART

- 6.1,����

- 6.2,�ص�

- 6.3,����ͼ

- 6.4,��������

- 6.5,����˵��

- 6.5.1,UART�����������ʷ�����

- 6.5.2,UART�����������ʲ���

- 6.5.3,UART�������Զ������ʹ���ģʽ

- 6.5.4,UART�����������ӳ�ʱ��ֵ

- 6.5.5,UART������FIFO���ƺ�״̬

- 6.5.6,UART���������ѹ���

- 6.5.7,UART�������жϺ�״̬

- 6.5.8,UART����ģʽ

- 6.5.9,IrDA����ģʽ

- 6.5.10,LIN����ģʽ(���ػ�������)

- 6.5.11,RS-485����ģʽ

- 6.5.11,PDMA���亯��

- 6.5.12,Register Map and Register Description

1,PDMA

Peripheral Direct Memory Access (PDMA)

����ֱ�Ӵ洢����ȡ(PDMA) �����������ṩ�������ݴ��䡣PDMA������������û��CPU��Ԥ������½����ݴ�һ����ַ���䵽��һ����ַ���������ĺô��Ǽ�����CPU�Ĺ�������,��Ϊ����Ӧ�ó������˿��е�CPU��Դ��������PDMA������PDMA0��PDMA1��ÿ��PDMA����������8��ͨ��,ÿ��ͨ������ִ�д洢��������֮���洢����洢��֮��Ĵ��䡣

����:

- ֧�� 2PDMA ������,�� PDMA0 �� PDMA1;

- ֧�� 8 ���ɶ������õ�ͨ��;

- ֧�ֿ�ѡ��2�����ȼ�(�̶����ȼ���ѭ�����ȼ�);

- ֧��8λ��16λ��32λ�Ĵ������ݿ���;

- ֧��Դ��Ŀ�ĵ�ַ������С�������ֽڡ����֡��ֻ�������;

- ֧��������USB��ͨ���첽�շ���(Universal Asynchronous

Receiver/Transmitters , UART)��ͨ�ô��п��ƽӿ�(Universal Serial Control

Interface, USCI)��������Χ�ӿ�(Serial Peripheral Interface

,SPI)��EPWM(Enhanced PWM< Pulse Width

Modulation>,��ǿ��������ȵ���)��I2C��I2S����ʱ��(Timer)��ģ��ת����(ADC)����ģת����(DAC)����; - ֧�ַ�ɢ-�ۼ�ģʽ,ͨ��ʹ��������������ִ�и��ӵĴ���;

- ֧�ֵ������ͻ����������;

- ֧��ͨ��0��ͨ��1�ij�ʱ����;

- ֧��ͨ��0��ͨ��5�Ŀ�ȹ���

2,SPI

Serial Peripheral Interface,SPI

��������ӿ�(SPI) ������ͬ����������ͨ��,������ȫ˫�����䡣�豸ͨ��4��˫��ӿ�����/��ģʽͨ�š�M261/M262/M263 ϵ������������ SPI ������,�Դ���Χ�豸���յ�����ִ�д���ת��,�Է��͵���Χ�豸������ִ�в���ת����ÿ�� SPI ��������������Ϊ���豸����豸,��֧�� PDMA �������������ݻ�������ÿ�� SPI ��������֧�� I2S ģʽ�����ⲿ��Ƶ���������

����:

1,SPIģʽ

- �������SPI������

- ֧����ģʽ���ģʽ����

- �����ֵĿ�����λ����8λ��32λ

- �ṩ������4����ȷ��ͺͽ����Ƚ��ȳ�������

- ֧�����λ���Ȼ����λ���ȴ�������

- ֧���ֽ���������

- ֧���ֽڻ��ֹ���ģʽ

- ֧��PDMA����

- ֧��һ������ͨ����˫������

- ֧��ֻ����ģʽ

2, I2Sģʽ

- ֧��������ӻ� -�ܹ�����8λ��16λ��24λ��32λ�Ĵ�����С

- ÿһ�����ṩ����4��FIFO���ݻ�����,һ�����ڷ���,��һ�����ڽ���

- ֧�ֵ���������������Ƶ����

- ֧��PCMģʽA��PCMģʽB��I2S��MSB���������ݸ�ʽ

- ֧������PDMA����,һ�����ڷ���,��һ�����ڽ���

3,EPWM

��оƬ�ṩ����EPWM������-EPWM 0��EPWM 1��

ÿ��EPWM֧��6·EPWM��������벶����һ��12λԤ��Ƶ��,֧��16λEPWM������(��16λ�Ƚ���)�����ʱ�ӡ�

EPWM������֧�ֵ������ݼ��͵����ݼ����������͡�EPWMʹ�ñȽ����ͼ������������¼�����Щ�¼����ڲ���EPWM���塢�жϺʹ����ź�,�Ա�EADC/DAC��ʼת����

EPWM������֧�����ֱ���EPWM���ģʽ:����ģʽ�ͻ���ģʽ,���Ǿ��в�ͬ����ϵ�ṹ�����ڱ����ģʽ�������������:�鹦�ܺ�ͬ�����ܡ������ڶ���ģʽ��ģʽ������Ⱥ�鹦�ܡ�ͬ�����ܽ�����ȫģʽ�����á�����ģʽ�������Ƚ���,��12λ������������������EPWM����;��һ�����ɴ����Ƚ���,��������EADC�Ĵ����źš�

EPWM������Ƶ�Ԫ֧�ּ�������������������κ��ƶ����ܡ�EPWM��������֧�����벶���ܡ�������ͨ����������ԾǨ���½�ԾǨ��ͬʱ��������ԾǨ���½�ԾǨʱ,֧�ֽ�EPWM������ֵ���浽��Ӧ�ļĴ����������ܻ�֧��PDMA����������ݴ��䵽�洢����

4,I2C����

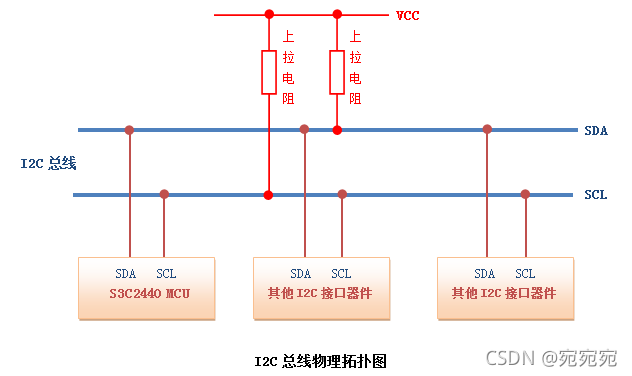

I2C ���������������Ϻܼ�,�� SDA (����������)�� SCL (����ʱ����)������������ɡ�ͨ��ԭ����ͨ���� SCL �� SDA �߸ߵ͵�ƽʱ��Ŀ���,�� ���� I2C ����Э������Ҫ���źŽ������ݵĴ��ݡ������߿���״̬ʱ,��������һ�㱻�������ӵ�������������,���ָߵ�ƽ״̬��

4.1,I2C��������

- I2C �����ϵ�ÿһ���豸��������Ϊ���豸���ߴ��豸,����ÿһ���豸�����Ӧһ��Ψһ�ĵ�ַ(�����豸��ͨ���õ�ַͨ��,��ַ���Դ� I2C �����������ֲ��֪)

- ��ͨ����Ӧ����,��CPU�� I2C ���߽ӿڵ�ģ����Ϊ���豸,�ѹҽ��������ϵ������豸����Ϊ���豸

- I2C �����Ͽɹҽӵ��豸���������ߵ������� 400pF ����,������ҽӵ�����ͬ�ͺŵ�����,����������ַλ������

- I2C �������ݴ��������ڱ�ģʽ�¿ɴ� 100 kbit/s,����ģʽ�¿ɴ� 400 kbit/s,����ģʽ�¿ɴ� 3.4 Mbit/s��һ��ͨ�� I2C ���߽ӿڿɱ��ʱ����ʵ�ִ������ʵĵ���,ͬʱҲ�����ӵ������������ֵ�й�

- I2C �����ϵ����豸����豸֮�����ֽ�(8λ)Ϊ��λ����˫������ݴ���

4.2,I2C������

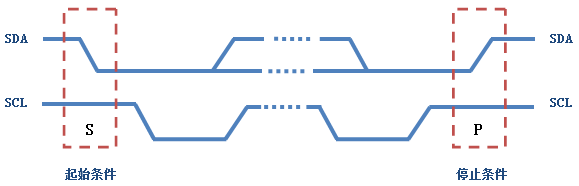

I2C Э��涨,���������ݵĴ��������һ����ʼ�ź���Ϊ��ʼ����,��һ�������ź���Ϊ�����ֹͣ��������ʼ�ͽ����ź����������豸������

�����ڿ���״̬ʱ,SCL��SDA�������Ÿߵ�ƽ��

��SCLΪ�ߵ�ƽ��SDA�ɸߵ��͵�����,��ʾ����һ����ʼ����;��SCLΪ�߶�SDA�ɵ͵��ߵ�����,��ʾ����һ�� ֹͣ������

����ʼ����������,���ߴ���æ״̬,�ɱ������ݴ���������豸��ռ,���� I2C ��������������;����ֹͣ����������,�������ݴ���������豸���ͷ�����,�����ٴδ��ڿ���״̬����ͼ��ʾ:

4.3,I2C�������ݴ������

4.3.1,���ݴ����������

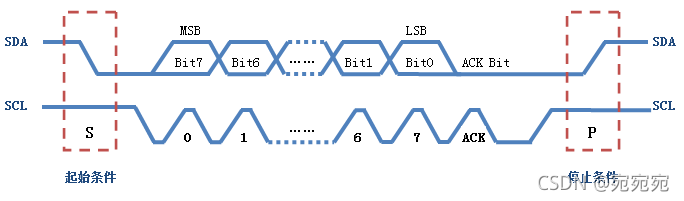

���ݴ������ֽ�Ϊ��λ�����豸��SCL���ϲ���ÿ��ʱ������Ĺ����н���SDA���ϴ���һ������λ,��һ���ֽڰ�����λ�Ӹ�λ����λ��˳�������,�����Ŵ��豸������SDA��,�ش������豸һ��Ӧ��λ, ��ʱ����Ϊһ���ֽ������ı�������ɡ�

��Ȼ,���������е��ֽڴ��䶼������һ��Ӧ��λ,����:�����豸�����ٽ������豸���͵�����ʱ,���豸���ش�һ���� ��Ӧ��λ�����ݴ���Ĺ�����ͼ��ʾ:

ע:MSBΪ�����Чλ,LSBΪ�����Чλ

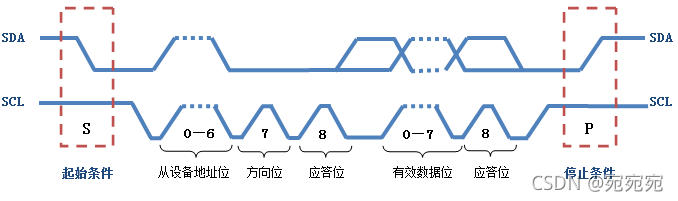

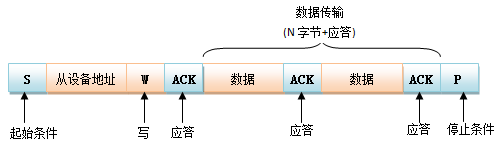

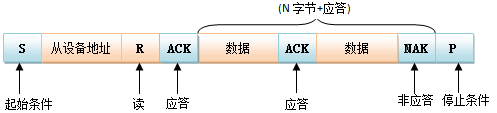

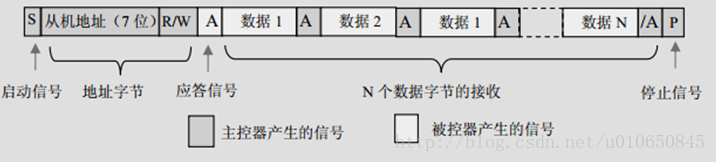

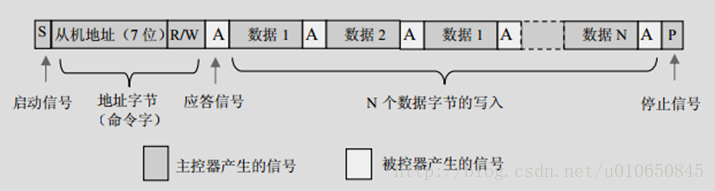

����,I2C �����ϵ�ÿһ���豸����Ӧһ��Ψһ�ĵ�ַ,�����豸֮������ݴ����ǽ����ڵ�ַ�Ļ�����,Ҳ����˵,���豸�ڴ�����Ч����֮ǰ Ҫ��ָ�����豸�ĵ�ַ,��ַָ���Ĺ��̺��������ݴ���Ĺ���һ��,ֻ������������豸�ĵ�ַ��7λ��,Ȼ��Э��涨�ٸ���ַ����һ�����λ������ʾ������ ���ݴ���ķ���,0��ʾ���豸����豸д����,1��ʾ���豸����豸�����ݡ���ͼ��ʾ:

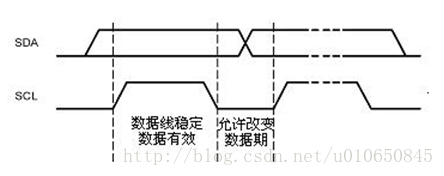

����,��IIC�����ϴ��͵�ÿһλ���ݶ���һ��ʱ���������Ӧ(��ͬ������),����SCL����ʱ�ӵ������,��SDA����λ�ش��д���ÿһλ���ݡ��������ݴ���ʱ,��SCL���ָߵ�ƽ�ڼ�,SDA�ϵĵ�ƽ���뱣���ȶ���ֻ����SCLΪ�͵�ƽ�ڼ�,������SDA�ϵĵ�ƽ�ı�״̬��

��I2C���ߵIJ���ʵ�ʾ��������豸֮��Ķ�д���������¿ɷ�Ϊ�������ֲ������:

-

���豸�����豸��д���ݡ����ݴ����ʽ����:

-

���豸�Ӵ��豸�ж����ݡ����ݴ����ʽ����:

ע:Ӧ���ź�Ϊ�͵�ƽʱ,�涨Ϊ��ЧӦ��λ(ACK���Ӧ��λ),��ʾ�������Ѿ��ɹ��ؽ����˸��ֽ�;Ӧ���ź�Ϊ�ߵ�ƽʱ,�涨Ϊ��Ӧ��λ(NACK),һ���ʾ���������ո��ֽ�û�гɹ���

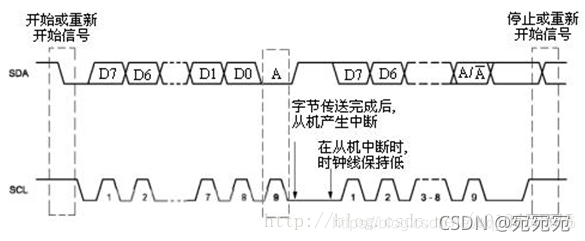

���һ���������ֽ����ݴ�����Ҫ9��ʱ�����塣����ӻ���Ϊ���շ����������ͷ�Ӧ���ź�,����������Ϊ�˴����ݴ���ʧ��;�����������Ϊ���շ�,�ڴӻ�������������һ���ֽ����ݺ�,��ӻ������˷�Ӧ���ź�,�ӻ�����Ϊ���ݴ������,���ͷ�SDA���������������������������ֹ���ݴ���,��ʱ�������Dz���ֹͣ�ź��ͷ������Dz������¿�ʼ�ź�,��ʼһ���µ�ͨ�š� -

���豸�����豸��д����,Ȼ��������ʼ����,�����ŴӴ��豸�ж�ȡ����;���������豸�Ӵ��豸�ж�����,Ȼ��������ʼ����(�뿪ʼ������ͬ),���������豸�����豸��д���ݡ����ݴ����ʽ����:

�����ֲ����ڵ������豸ϵͳ��,�ظ��Ŀ�����ʼ��������Ҫ����STOP��ֹ��������ٴο������߸���Ч�ʡ�

ע:�������ݲ��ִӴ��е����� I2C����Э����� ���������õ�

4.3.2,����ȴ�ʱ��

�����������Ҫ�ӳ���һ�������ֽڿ�ʼ���͵�ʱ��,�����ͨ����ʱ����SCL��ƽ���Ͳ��ұ���,ʹ����������ȴ�״̬��һ���������ͷ�ʱ����,���ݴ���͵��Լ�����ȥ,������ʹ�ñ������õ��㹻ʱ��ת���Ѿ��յ��������ֽ�,�������ü������͵������ֽڡ�

����CPU�ı������ڶ��յ��ĵ�ַ�ֽ�����Ӧ��֮��,��Ҫһ����ʱ��ȥִ���жϷ����ӳ���,��������Ƚϵ�ַ��,���Ͱ�SCL��ǯλ�ڵ͵�ƽ��,ֱ������������ͷ�SCL��,����ʹ�������������������ֽڵķ���

4.3.3,���߳�ͻ�������ٲ�

������ijIIC����ϵͳ�д��������������ڵ�,�ֱ��Ϊ������1��������2,��������ݷֱ�ΪDATA1��DATA2,���Ƕ��п������ߵ�����,��ʹ����ŷ������߳�ͻ(��д��ͻ)�Ŀ����ԡ�

������ijһ˲��������������߷����������ź�,����:I2C���ߵġ����롱����,ʹ����������SDA�ϵõ����źŲ�����DATA1��DATA2��������Ľ��

�����߱�������,������1��ͼ�������ݡ�101������,������2��ͼ�������ݡ�100��������

������������ÿ�η���һ������λ��ͬʱ��Ҫ���Լ�����˵��źŵ�ƽ���г��,ֻҪ���Ľ���������Լ�Ԥ�ڵĵ�ƽ���,�ͻ����ռ������,���߿���ȨҲ�͵ò����ö������

������1�ĵ�3λ�������͡�1��,Ҳ�����ڵ�3��ʱ���������ͳ��ߵ�ƽ���ڸ�ʱ�����ڵĸߵ�ƽ�ڼ�,������1�������г��ʱ,�����һ������ƥ��ĵ�ƽ��0��,��ʱ������1ֻ�þ����������߿����;���,������2�ͳ������ߵ�Ωһ������,���߿���ȨҲ�����յó��˲ö����,�Ӷ�ʵ���������ٲõĹ��ܡ�

�����������ٲõ���ɹ��̿��Եó�:�ٲù���������1��������2�����ᶪʧ����;����������û�����ȼ���֮��,���߿���Ȩ������ö��ġ�

ϵͳʵ������ѭ���ǡ��͵�ƽ���ȡ����ٲ�ԭ��,�������и������������ȷ��͵͵�ƽ��������,���������ߵ�ƽ����������ʧȥ���߿���Ȩ

4.3.4,ʱ��ͬ��

�����ijһI2C����ϵͳ�д��������������ڵ�,�ֱ��Ϊ������1��������2,��ʱ������˷ֱ�ΪCLK1��CLK2,���Ƕ��п������ߵ�������

������ijһ�ڼ����������SCL�߷����˲��β�ͬ��ʱ����������CLK1��CLK2,�����߿���Ȩ��û�вö�֮ǰ���������ǿ��ܳ��ֵġ�

����IIC���ߵġ����롱����,ʹ��ʱ����SCL�ϵõ���ʱ���źŲ���,�Ȳ���������1��������CLK1,Ҳ����������2��������CLK2,�������߽�������Ľ����

CLKI��CLK2�ĺϳɲ�����Ϊ��ͬ��ͬ��ʱ���ź�,һ�����߿���Ȩ�ö���ijһ������,������ʱ���źŽ���ֻ�ɸ�����������

4.3.5,�������

���߷���״̬

�����������,�����Ҫ��ֹ���з�����I2C�����ϵ�ͨ�Ż,������ر�������һ�ֿ���;��,ֻҪ�ҽ��ڸ������ϵ�����һ��������ʱ����SCL�����ڵ͵�ƽ�ϼ��ɡ�

����ģʽ

ԭ���Ͻ�,ʹ������������������1���������ߵ�������ٶȡ����ٶ�����������Ӧ�õ�����֮һ����Ҳ˵��ΪʲôҪ�������ģʽ(3.4 Mbps)���ڷ���һ�θ���ģʽ����ǰ,���豸�������ڵ��ٵ�ģʽ��(�������ģʽ)�����ض��ġ�High Speed Master���źš�Ϊ�����źŵ����ں���������ٶ�,����ģʽ����ʹ�ö����I/O������������,�����ٲ��ڸ���ģʽ�¿����ε���

ʱ������

�� IIC ͨ����,���豸������ʱ���ٶȡ���Ϊʱ�������ź��������豸��ʽ�����ġ�����,�����豸û�취�������豸���ٶ�ʱ,���豸��Ҫһ�ֻ������������豸��һ�㡣���ֻ��Ƴ�Ϊʱ������,������I2C�ṹ��������,���ֻ��Ƶõ�ʵ�֡������豸��Ҫ���ʹ�����ٶȵ�ʱ��,����������ʱ����,�������豸����ȴ�״̬,ֱ�����豸�ͷ�ʱ����,ͨ�Ųż�����

4.4,ͨ�Ź���

����,���豸��һ��START�ź�,Ȼ�������豸��ʼ�������������������ݡ�����,���豸����һ��7λ�豸��ַ��һλ�Ķ�д����������֡�������д��豸�������ݺ�,�ȶԵ�ַ�Լ��Ƿ�Ŀ���豸������ȶԲ���,�豸����ȴ�״̬,�ȴ�STOP�źŵ�����;����ȶ����,�豸�ᷢ��һ��Ӧ���źš���ACK����Ӧ��

�����豸�յ�Ӧ���㿪ʼ���ͻ�������ݡ�����֡��СΪ8λ�����豸��������,���豸Ӧ��;�෴���豸��������,���豸Ӧ�𡣵����ݴ������,���豸����һ��STOP�ź�,�������豸�����ͷ�����,�����豸�ص���ʼ״̬��

4.5,Ѱַ����

ѰַԼ��

Ϊ������IIC����ϵͳ���������뱻�����ĵ�ַѡ����,����ȵؼ�����������,IIC���߲����˶��ص�ѰַԼ��,�涨�˿�ʼ�źź�ĵ�һ���ֽ�ΪѰַ�ֽ�,����Ѱַ��������,���涨���ݴ��ͷ���

��IIC����ϵͳ��,Ѱַ�ֽ�����λ��ַλ(��ռ����D7-D1λ)��һλ����λ(ΪD0λ)��ɡ�����λΪ0ʱ��ʾ������������д�뱻����,Ϊ 1ʱ��ʾ�������ӱ�������ȡ���ݡ����������Ϳ�ʼ�źź�,��������Ѱַ�ֽ�,��ʱ�����ϵ�������������Ѱַ�ֽ��е�7λ��ַ���Լ�������ַ�Ƚϡ����������ͬ,���������Ϊ��������Ѱַ,������Ӧ���ź�,���������ݶ�/дλȷ����������Ϊ���������ǽ�������

��������Ϊ������ʱ,��7λ�ӵ�ַ��IIC���ߵ�ַ�Ĵ����и���,Ϊ��������ַ�����ǵ�Ƭ�����͵���Χ������ַ��ȫ���������������ŵ�ƽ������IIC����ϵͳ��,û�������ӻ��ĵ�ַ����ͬ�ġ���������Ӧ�ô���һ�����������Ĵӵ�ַ��ͬ�ĵ�ַ��

7λI2C���߿��Թҽ�127����ͬ��ַ��I2C�豸,0�š��豸����ΪȺ����ַ.

��ַ�ķ��䷽��������:

��CPU����������,��ַ��������ʼ��ʱ����,�������������������г�ͻ

����CPU�ķ���������,�ɳ����������ڲ��̻�,���ɸı䡣

��7λΪ��ַ��,���Ϊ������:

��4λ���ڹ̶���ַ���ɸı�,�ɳ��ҹ̻���ͳһ��ַ;

����λΪ�����趨��ַ,�������ⲿ�������趨(�������������������趨);

����IIC�ӿ�ͨ��������������ַ���������ͺ��Լ�Ѱַ����ɵ�,��7λ�����ʽ����:

D7 D6 D5 D4 D3 D2 D1 D0

����������:D7-D4 ��4λ�����ġ������ɰ뵼��˾����ʱ���ѹ̶�����,Ҳ����˵��4λ���ǹ̶��ġ��û��Զ����ַ��:D3-D1��3λ���������û��Լ����õ�,ͨ����������EEPROM��Щ���������ⲿIC��3����������ϵ�ƽ������(�ó��õ�������A0,A1,A2)����Ҳ����Ѱַ�롣����ΪʲôͬһIIC������ͬһ�ͺŵ�ICֻ������8Ƭͬ����оƬ��ԭ���ˡ�

4.6,�����

������

�������������źź�,���ŷ��������ֽ�(���� R/W=1)

��Ӧ�Ĵӻ��յ���ַ�ֽں�,����һ��Ӧ���źŲ���������������

�����յ����ݺ���ӻ�����һ��Ӧ���ź�

�ӻ��յ�Ӧ���źź���������������һ������

��������ɽ������ݺ�,��ӻ�����һ������Ӧ���ź�(ACK=1)��,�ӻ��յ�ACK=1 �ķ�Ӧ���źź��ֹͣ����

�������ͷ�Ӧ���źź�,�ٷ���һ��ֹͣ�ź�,�ͷ����߽���ͨ��

ע��:�������������ݵ���������������������,�����͡���Ӧ���ź�/A��ʱ�ӻ���������Ͳ��ͷ�����(��Ӧ���źŵ���������:ǰһ�����ݽ��ճɹ�,ֹͣ�ӻ����ٴη���)��

���

�����ڼ�����Ϊ������״̬��(�� SDA��SCL �߾�Ϊ�ߵ�ƽ)ʱ,����һ�������źš�S��,��ʼһ��ͨ�ŵĿ�ʼ

�������ŷ���һ�������ֽڡ����ֽ��� 7 λ����Χ������ַ�� 1 λ��д����λ R/W���(��ʱ R/W=0Ϊд)

���Ӧ�Ĵӻ��յ������ֽں�����������Ӧ���ź� ACK(ACK=0)

�����յ��ӻ���Ӧ���źź�ʼ���͵�һ���ֽڵ�����

�ӻ��յ����ݺ�һ��Ӧ���ź� ACK

�����յ�Ӧ���źź��ٷ�����һ�������ֽ�

�������������һ�������ֽڲ��յ��ӻ��� ACK ��,ͨ����ӻ�����һ��ֹͣ�ź�P��������ͨ�Ų��ͷ����ߡ��ӻ��յ�P�źź�Ҳ�˳�������֮���ͨ��

ע��:������ͨ�����͵�ַ�����Ӧ�Ĵӻ�������ͨ�Ź�ϵ,���ҽ��������ϵ������ӻ���ȻͬʱҲ�յ��˵�ַ��,����Ϊ���������ĵ�ַ�������,�����ǰ�˳���������ͨ��;��������һ�η���ͨ��,�䷢�͵����������������ơ�������ͨ�� P �ź�֪ͨ���͵Ľ���,�ӻ��յ� P �źź��˳�����ͨ��;��������ÿһ�η��ͺ���ͨ���ӻ��� ACK �ź��˽�ӻ��Ľ���״��,���Ӧ��������ط���

��������ԭ�����,��ַ��չ�� IIC ���ߵ���Ӧ������ο�����2

�ο�����1: I2C���߽���.

�ο�����2(��ϸ):I2C����Э��/��ַ���.(���ĺܶ�����Ϊֱ�Ӹ��Ʊ����Ӷ���)

�ο�����3: ����ƪ����������(SPI��I2C��I2S��鼰����Ա�).

�ο�����4: I2S���߸���.<����̫��>

�����5: ��������:IIC��IIS��SPI��UART��JTAG��CAN��SDIO��GPIO.

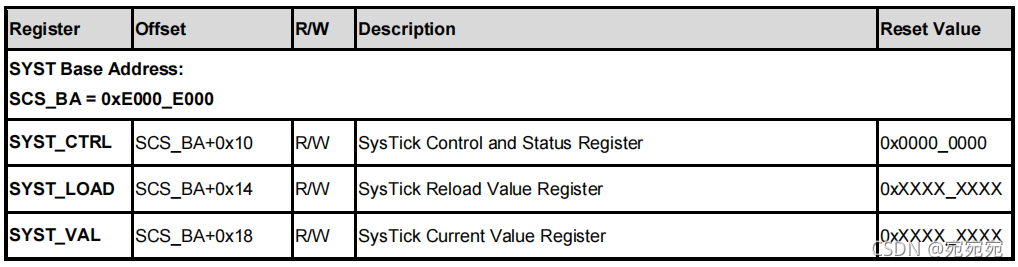

5,SysTick(System Timer)

Cortex?-M23����һ�����ɵ�ϵͳ��ʱ��SysTick,�ö�ʱ���ṩ��һ����24λ��д���ݼ������������,�������Ŀ��ƻ��ơ�������������ʵʱ����ϵͳ(RTOS)��ʱ�����������

����ϵͳ��ʱ����,������SysTick��ǰֵ�Ĵ���(SYST_VAL)�е�ֵ���¼�������,������һ��ʱ���������¼���(����)��SysTick���¼���ֵ�Ĵ���(SYST_LOAD)�е�ֵ,Ȼ���ں���ʱ���ϵݼ�����������ת��Ϊ��ʱ,COUNTFLAG״̬λ�����á���ȡʱ,COUNTFLAGλ���㡣

SYST_VALֵ�ڸ�λʱδ֪�������øù���֮ǰ,����Ӧд��Ĵ����Խ������㡣���ȷ����ʱ��������ʱ����syst_loadֵ����������ֵ��ʼ����

���syst_loadΪ��,���ʱ����ʹ�ô�ֵ���¼��غ��ֵ�ǰֵΪ�㡣�û��ƿ����ڶ����ڶ�ʱ��ʹ��λ���øù���

�йظ�����ϸ��Ϣ,����ġ�ARM?Cortex?-M23�����ο��ֲᡷ�͡�ARM?V8-M�ܹ��ο��ֲᡷ��

5.1,ϵͳ��ʱ�����ƼĴ���ӳ��

R: read only, W: w rite only, R/W: both read and write

5.2,ϵͳ��ʱ�����ƼĴ�������

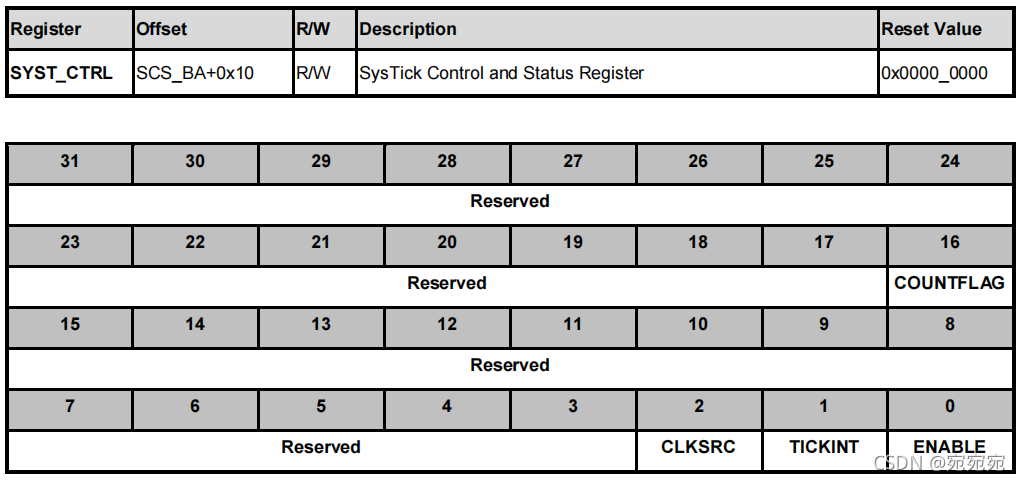

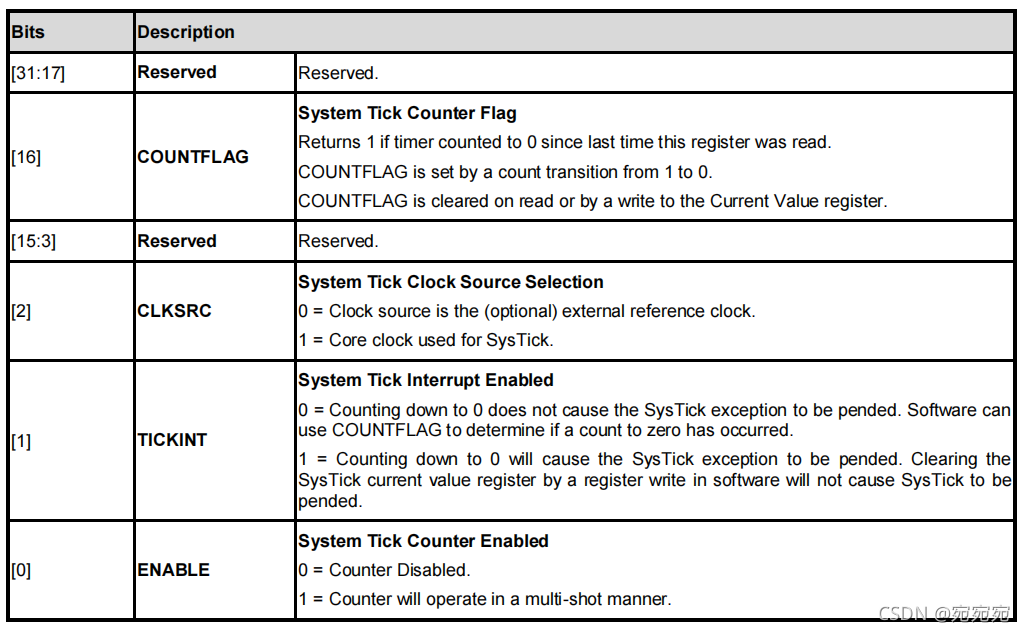

5.2.1,SysTick���ƺ�״̬�Ĵ���(SYST_CTRL)

����,COUNTFLAG ����ض���Ϊ:

������ϴζ�ȡ�üĴ���������ʱ������Ϊ0,��ϵͳ��ʱ��������־����1��COUNTFLAGͨ����1��0�ļ���ת�������á�COUNTFLAG�ڶ�ȡ��д�뵱ǰֵ�Ĵ���ʱ�����

ϵͳ�δ�ʱ��Դѡ��CLKSRC

0=ʱ��ԴΪ(��ѡ)�ⲿ�ο�ʱ�ӡ�

1=SysTickʹ�õĺ���ʱ�ӡ�

ϵͳ��ʱ�ж����á���TICKINT

0=����ʱ��0���ᵼ�¹���SysTick�쳣����������ʹ��COUNTFLAG��ȷ���Ƿ����˼���Ϊ��������

1=����ʱ��0�����¹���SysTick�쳣��ͨ����������д��Ĵ��������SysTick��ǰֵ�Ĵ������ᵼ��SysTick����

ϵͳ���ļ��������á���ENABLE

0=���������á�

1=���������Զ�巽ʽ���С�

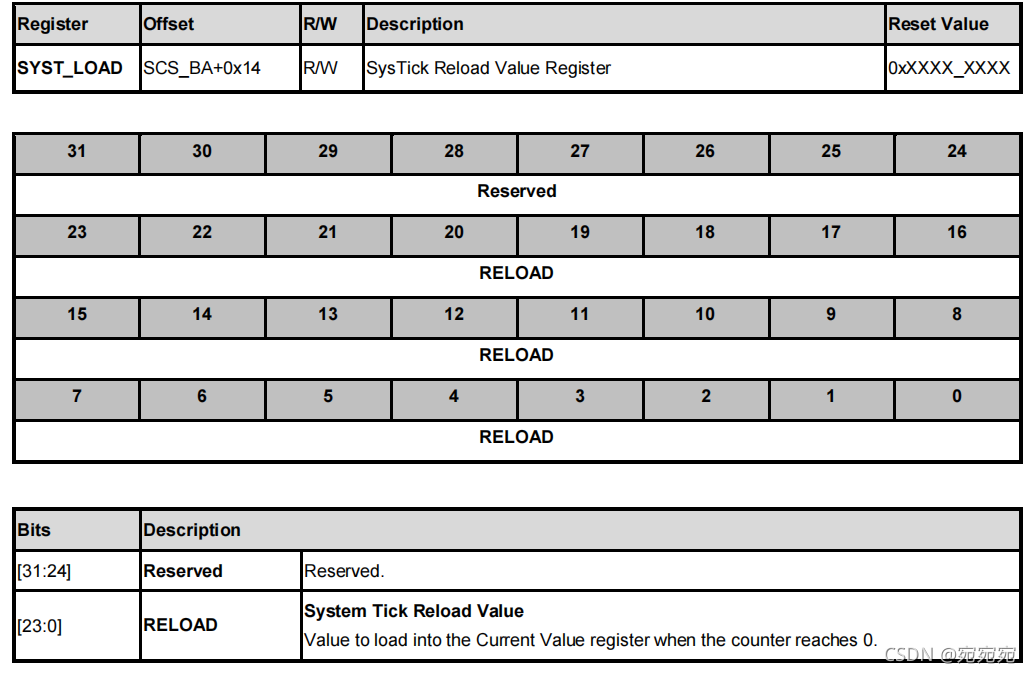

5.2.2,SysTick����ֵ�Ĵ���(SYST_LOAD)

ϵͳ��ʱ����ֵ����RELOAD

�������ﵽ0ʱҪ���ص���ǰֵ�Ĵ�����ֵ��

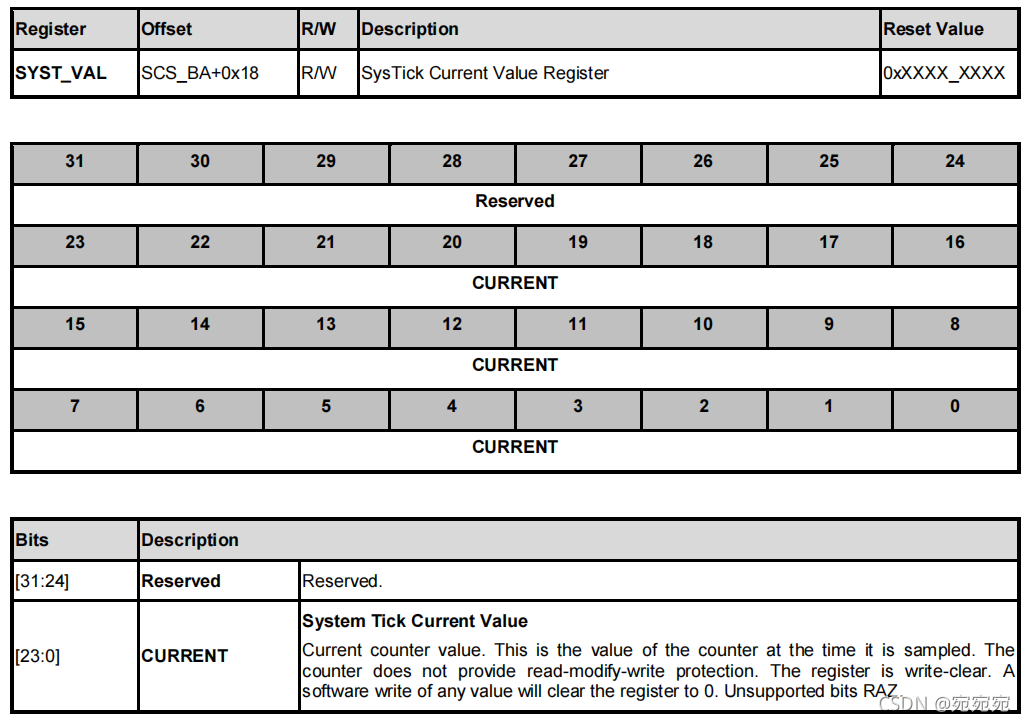

5.2.3,SysTick��ǰֵ�Ĵ���(SYST_VAL)

ϵͳ�δ�ֵ����CURRENT

��ǰ������ֵ�����Dz���ʱ��������ֵ�����������ṩ��-��-д�������üĴ�����д����ġ�����д���κ�ֵ���Ὣ�Ĵ������㡣��֧�� bits RAZ��

RAZ : Read-As-Zero ���κ�ʵ����,λ�����Ϊ0,����һ��λ�������ֵ����0��

�ο�����: ����һЩ����Ľ���.

5.3,һ���IJο�����

__STATIC_INLINE void CLK_SysTickLongDelay(uint32_t us)

{

uint32_t u32Delay;

/* It should <= 65536us for each delay loop */

u32Delay = 65536UL;

do

{

if(us > u32Delay)

{

us -= u32Delay;

}

else

{

u32Delay = us;

us = 0UL;

}

SysTick->LOAD = u32Delay * CyclesPerUs; //CyclesPerUs����Ϊ:Cycles per micro second,��ֵ��Ϊ48,������������֪,��ֵΪ��ǰҪ���ص�SysTick�Ĵ����е�ֵ

SysTick->VAL = (0x0UL); //SYST_VALֵ�ڸ�λʱδ֪�������øù���֮ǰ,����Ӧд��Ĵ����Խ������㡣���ȷ����ʱ��������ʱ����syst_loadֵ����������ֵ��ʼ����

SysTick->CTRL = SysTick_CTRL_CLKSOURCE_Msk | SysTick_CTRL_ENABLE_Msk; //��ʼ��,����CLCSRCλ��ENABLEλ��ֵ��Ϊ1.��SysTick����core clock,��ʹ��SysTick�Ĵ���

/* Waiting for down-count to zero */

while((SysTick->CTRL & SysTick_CTRL_COUNTFLAG_Msk) == 0UL);//����ѭ��ʱ,SysTick->CTRL & SysTick_CTRL_COUNTFLAG_Msk=0(000101 & (1<<16)),ѭ����������,����whileѭ����֮��ֱ������������,SysTick->CTRL�е�COUNTFLAGλ��0��Ϊ1,ѭ���������ٳ���,����ѭ����

/* Disable SysTick counter */

SysTick->CTRL = 0UL;//���øò���,��Ҫ������COUNTFLAGλ

}

while(us > 0UL);

}

������Ϊһ������ʱ����,������SysTick��ʱ��������ʱ������

6,UART

UART Interface Controller (UART) :UART�ӿڿ�����

6.1,����

��оƬ�ṩ��·ͨ���첽�շ��� (Universal Asynchronous Receiver/Transmitters,UART)��UART������ִ�г���UART,��֧���������ƹ��ܡ�UART�������Դ�������յ�����ִ�д���ת��,�Դ�CPU���͵�����ִ�в���ת����ÿ��UART������ͨ��֧��10�����͵��жϡ�UART��������֧��IrDA SIR��LIN��RS-485����ģʽ�Լ��Զ������ʲ������ܡ�

6.2,�ص�

- ȫ˫���첽ͨ��;

- ��������Ч�غɵ�16/16�ֽ������Ƚ��ȳ�����;

- ֧��Ӳ���Զ���������;

- �ɱ�̽�����������������ƽ;

- ֧��ÿ��ͨ���Ŀɱ�̲����ʷ�����;

- ֧��nCTS���������ݡ����������Ƚ��ȳ��ﵽ��ֵ��RS-485��ַƥ��(AADģʽ)���ѹ���;

- ֧��8λ���������峬ʱ����;

- ͨ������DL�ɱ�̴�����һվ����һ��ʼλ֮��������ӳ�ʱ��;

- ֧���Զ������ʲ����Ͳ����ʲ�������,

��LXTѡ��֧��9600 bps��UART_CLK�� - ֧���жϴ���֡������żУ�����ͽ���/���ͻ������������;

- ��ȫ�ɱ�̵Ĵ��нӿ����ԡ�

���ɱ������λ��,5λ��6λ��7λ��8λ�ַ�;

���ɱ����żУ��λ��ż���桢����żУ��λ��������żУ��λ���ɺͼ��;

���ɱ��ֹͣλ,1��1.5��2��ֹͣλ���� - ֧��IrDA SIR����ģʽ

��֧������ģʽ��3/16λ����ʱ��; - ֧��LIN����ģʽ(��UART0/UART1����LIN����)

��֧��LIN��/��ģʽ;

��֧�ַ�����ɱ���ж����ɹ���;

��֧�ֽ��ջ��жϼ���; - ֧��RS-485����ģʽ��

��֧��RS-4859λģʽ;

��֧��Ӳ��������,�ɶ�NRT���Ž��б���Կ���RS-485���䷽��; - ֧��PDMA���书��

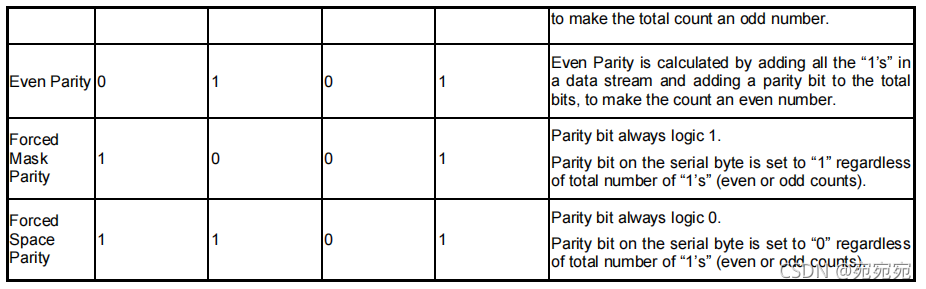

6.3,����ͼ

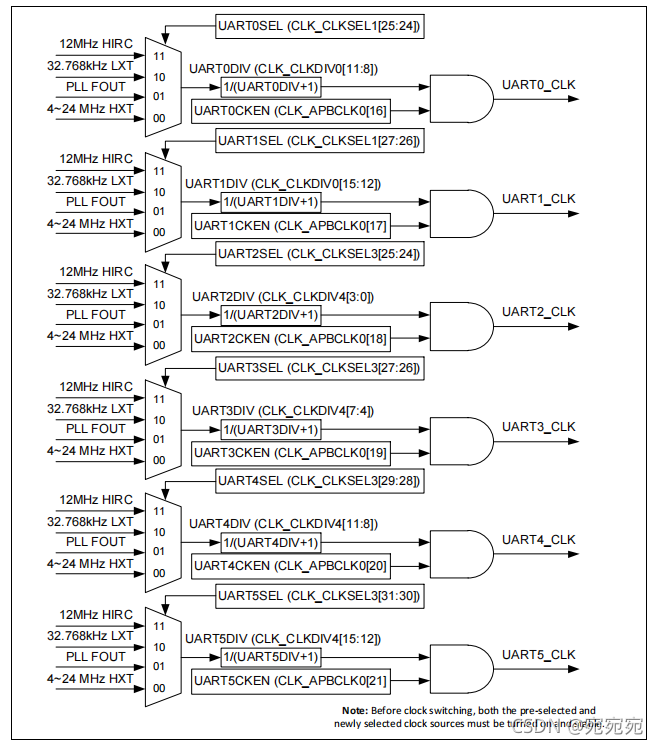

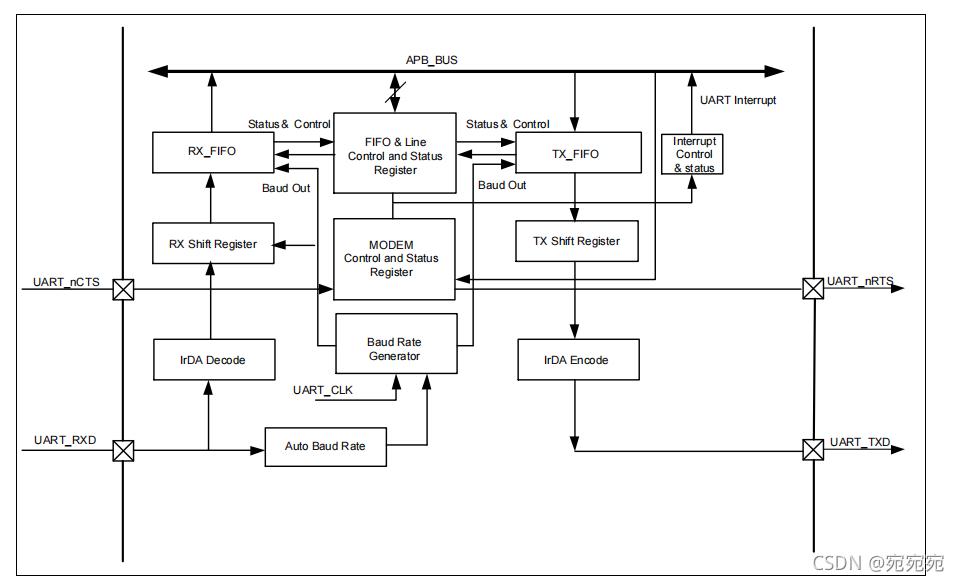

UARTʱ�ӿ��ƺͿ�ͼ�ֱ�����ͼ6.3-1��ͼ6.3-2��ʾ:

ע��:UARTx_CLK��Ƶ�ʲ�Ӧ����HCLK��30����

ͼ6.3-1 UARTʱ�ӿ���ͼ

ͼ6.3-2 UART��ͼ

ÿ�������ϸ��������:

TX_FIFO

����������16�ֽ�FIFO���л���,�Լ����ṩ��CPU���ж�������

RX_FIFO

������ʹ��16�ֽ�FIFO(�����������λBIF(UART_FIFO STS[6])��FEF(UART_FIFO STS[5])��PEF(UART_FIFO STS[4])���л���,�Լ�����CPU�ṩ���ж�������

TX Shift Register

��ģ�鸺�����Ƴ��������ݡ�

RX Shift Register

��ģ�鸺��������������ݡ�

Modem Control and Status Register

���ƽ�������ƺ�״̬�Ĵ���,�˼Ĵ������Ƶ��ƽ���������ݼ�(��ģ����ƽ��������Χ�豸)�Ľӿڡ�

Baud Rate Generator

�����ʷ�����,���ⲿʱ�ӳ��Գ���,�õ�����IJ�����ʱ�ӡ�����IJ����ʷ��̡�

IrDA Encode

IrDA����,�˿���IrDA������ƿ�

IrDA Decode

IrDA����,�˿���IrDA������ƿ�

FIFO & Line Control and Status Register

FIFO&��·���ƺ�״̬�Ĵ���,���ֶ��ǼĴ�����,�������ڷ������ͽ�������FIFO���ƼĴ���(UART_FIFO)��FIFO״̬�Ĵ���(UART_FIFOSTS)����·���ƼĴ���(UART_LINE)����ʱ�Ĵ���(UART_TOUT)��ʶ��ʱ�жϵ�����

Auto-Baud Rate Measurement

�Զ������ʲ���,��ģ�鸺���Զ������ʲ�����

Interrupt Control and Status Register

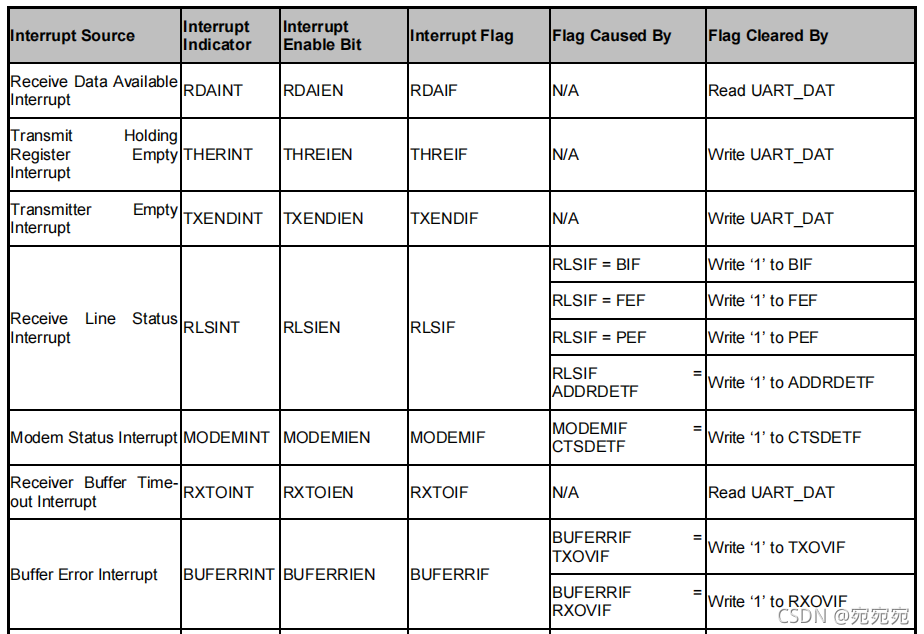

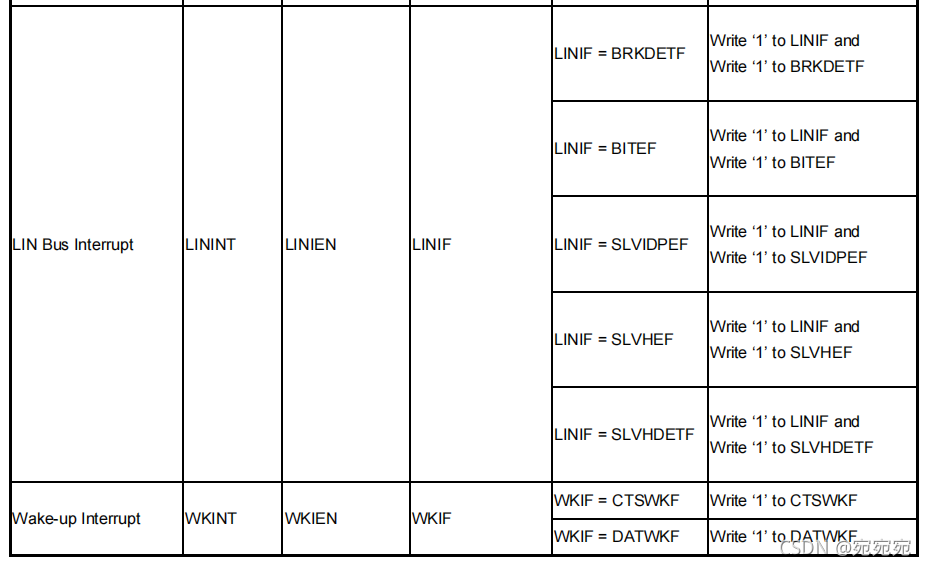

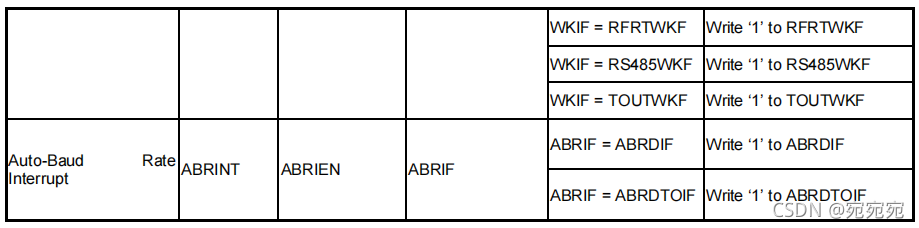

�жϿ��ƺ�״̬�Ĵ���,��ʮ�����͵��ж�,�������ݿ����ж�(Receive Data Available Interrupt,RDAINT)�����ͱ��ּĴ������ж�(Transmit Holding Register Empty Interrupt ,THERINT)�����������ж�(Transmitter Empty Interrupt ,TXENDINT)��������״̬�ж�(��żУ�������֡������ж�)(Receive Line Status Interrupt ,RLSINT)�����ƽ����״̬�ж�(MODEM Status Interrupt ,MODEMINT)����������������ʱ�ж�(Receiver Buffer Time-out Interrupt ,RXTOINT)�������������ж�(Buffer Error Interrupt ,BUFERRINT)��LIN�����ж�(Bus Interrupt,LINT),�����ж�(Wake-up Interrupt ,WKINT) ���Զ��������ж�(Auto-Baud Rate Interrupt ,ABRINT)���ж����üĴ���(UART_INTEN)���û������Ӧ�жϺ��ж�״̬�Ĵ���(UART_INTSTS),��ʶ����Ӧ�жϵķ�����

6.4,��������

UART0�Ļ�����������:

- ʱ��Դ����

�Cѡ��UART0SEL(CLK_CLKSEL1[25:24])�ϵ�UART0����ʱ��Դ��

�Cѡ��UART0DIV(CLK_CLKDIV0[11:8])��UART0����ʱ�ӵ�ʱ�ӷ�Ƶ����š�

�C��UART0CKEN(CLK_APBCLK0[16])������UART0����ʱ�ӡ� - ��UART0RST(SYS_IPR ST1[16])������UART0��������

- ��������

UART1�Ļ�����������:

- ʱ��Դ����

�Cѡ��UART1SEL(CLK_CLKSEL1[27:26])�ϵ�UART1����ʱ��Դ��

�Cѡ��UART1DIV(CLK_CLKD IV0[15:12])��UART1����ʱ�ӵ�ʱ�ӷ�Ƶ����š�

�C��UART1CKEN(CLK_APBCLK0[17])������UART1����ʱ�ӡ� - ��λUART1RST(SYSIPRST1[17])�е�UART1��������

- ��������

UART2 ~ UART5��,��������ֲ�

6.5,����˵��

UART������֧�����ֹ���ģʽ,����UART��IrDA��LIN��RS-485ģʽ���û�����ͨ������UART_FUNCSEL�Ĵ�����ѡ���ܡ����²��ֽ����������ֹ���ģʽ��

6.5.1,UART�����������ʷ�����

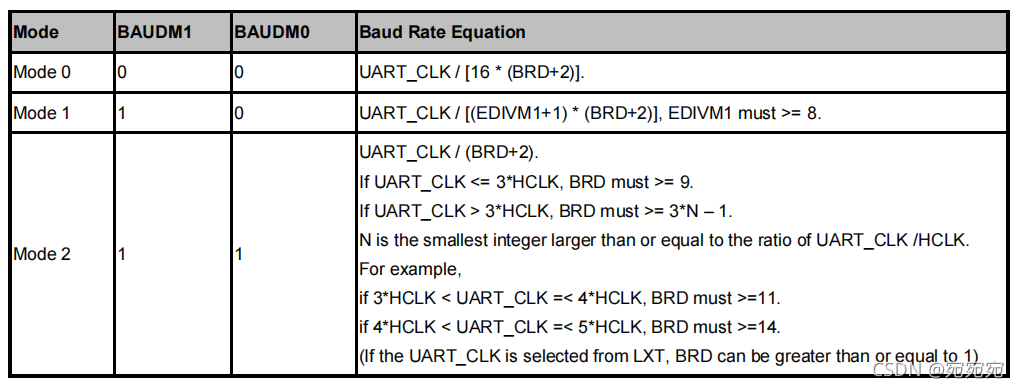

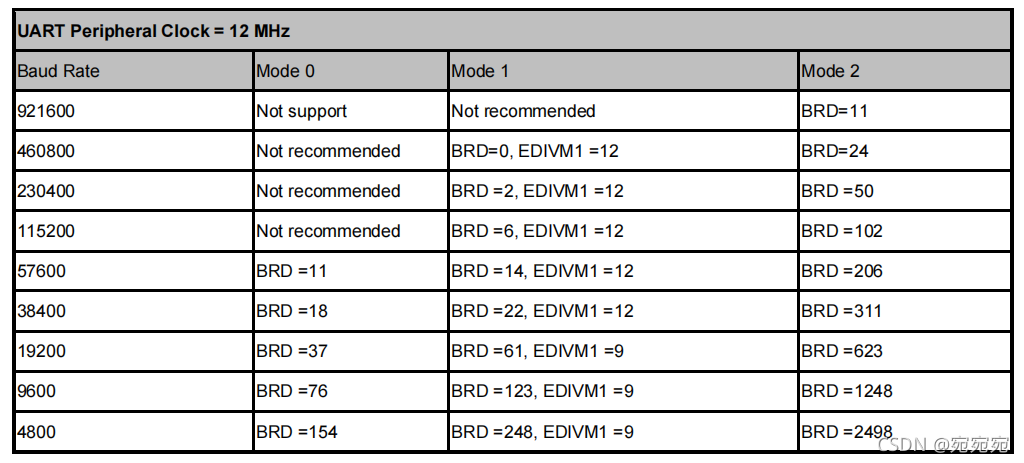

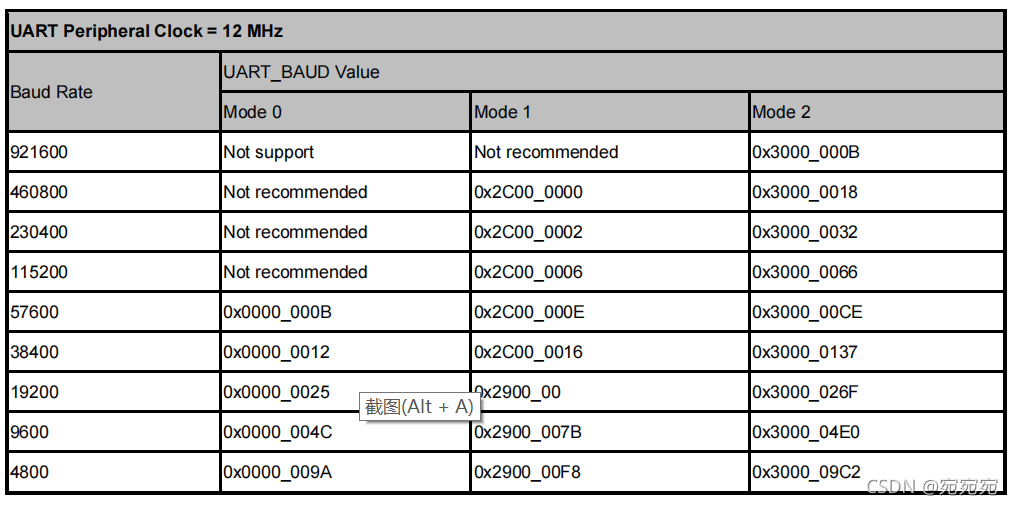

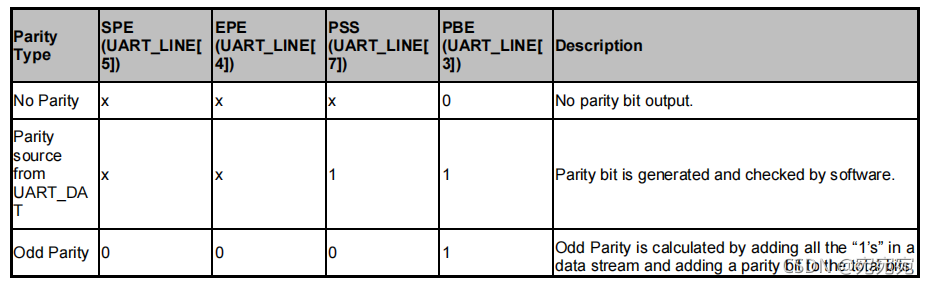

UART����������һ���ɱ�̲����ʷ�����,�ܹ���ʱ��������Գ���,�Բ����������ͽ���������Ĵ���ʱ�ӡ���6.1�г��˸��������µ�UART�����ʹ�ʽ����6.2�ͱ�6.3�г���UART�����ʲ����ͼĴ�������ʾ������IrDA����ģʽ��,�����ʷ�������������Ϊģʽ0������ϸ�ļĴ���˵����UART_BAUD�Ĵ���������������ģʽ��ģʽ0��UART_Baud[29:28]����Ϊ00��ģʽ1��UART_Baud[29:28]����Ϊ10��ģʽ2��UART_Baud[29:28]����Ϊ11��

��6.1 UART�����������ʷ���ʽ��

��6.2 UART�����������ʲ�������ʾ����

ע:UART����ʱ��=12 MHz

��6.3 UART�����������ʼĴ�������ʾ����

6.5.2,UART�����������ʲ���

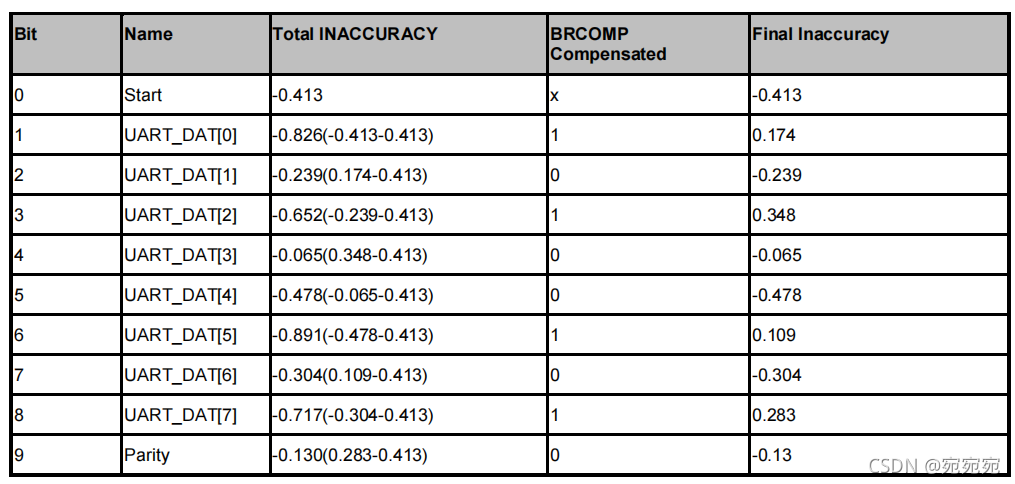

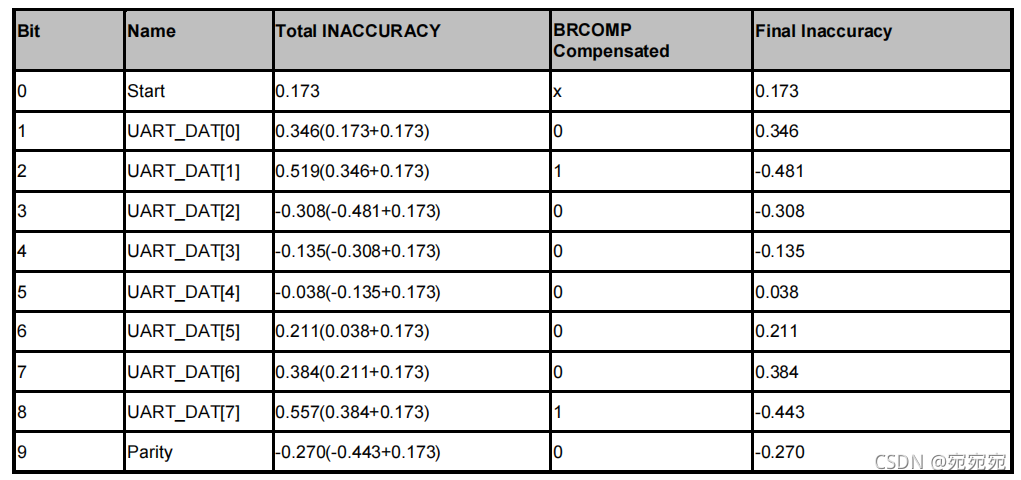

UART������֧�ֲ����ʲ������ܡ��������Ż�ÿһλ�ľ��ȡ���������ΪUARTģ��ʱ�ӵ�һ��,��Ϊÿ��λ����BRCOMDECλ(UART_BRCOMP[31])�������������������BRCOMPDEC(UART_BRCOMP[31])=0,��ÿһλΪ������,����λ�н��ٸ���һ��ģ��ʱ�ӡ����BRCOMPDEC(UART_BRCOMP[31])=1,��ÿһλΪ������,�ڲ���λ�м���һ��ģ��ʱ�ӡ�

BRCOMP [8:0] (UART_BRCOMP[8:0])��9λλ��,�����û������Զ����Ƿ����λ��BRCOMP[7:0]���ڶ���UART_DAT[7:0]�IJ���,BRCOMP[8]���ڶ�����żУ��λ��

ʾ��:

1, UART������ʱ��=32.768K,������Ϊ9600

UART����ʱ��Ϊ32.768K->3.413(32768 / 9600)1 ����ʱ�� / λ

������ط�Ƶ������Ϊ1(3������ʱ�� / λ),��ÿ��λ�����Ϊ-0.413����ʱ��,��BRCOMPDEC=0��

��6.4 �����ʲ���ʾ����1

���BRCOMP(UART_BRCOMP[8:0])��������Ϊ9��b010100101=0xa5��

2, UART������ʱ��=32.768K,������Ϊ4800

������Ϊ4800ʱ,UART����ʱ��Ϊ32.768K->6.827����ʱ��/λ

��������ʷ�Ƶ������Ϊ5(7������ʱ��/λ),��ÿλ�����Ϊ0.173����ʱ��,BRCOMPDEC=1��

��6.5 �����ʲ���ʾ����2

���BRCOMP(UART_BRCOMP[8:0])��������Ϊ9��b010000010=0x82��

6.5.3,UART�������Զ������ʹ���ģʽ

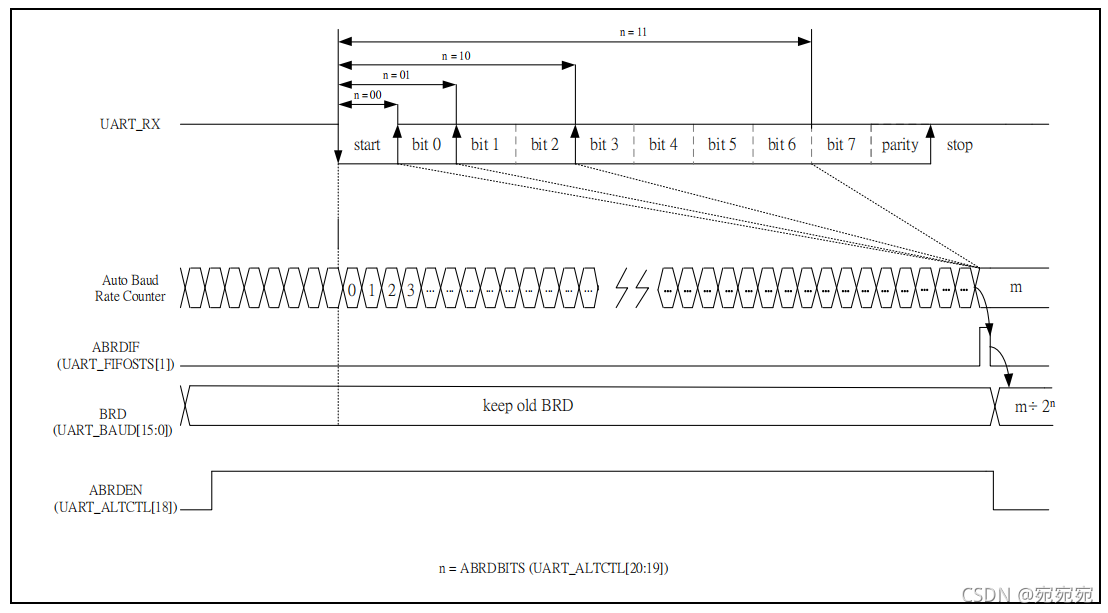

�Զ������ʹ��ܿ����Զ�������UART RX���Ž������ݵIJ����ʡ��Զ������ʲ�����ɺ�,���������ʼ��ص�BRD(UART_BAUD[15:0])��BAUDM1(UART_BAUD[29])��BAUDM0(UART_BAUD[28])���Զ�����Ϊ1������ʼλ����һ������ʱ���UART RX�������Զ������ʹ��ܼ��֡�е�2ABRDBITSλʱ�����á�

2ABRDBITSλ����ʼλ����һ�������ص�ʱ��ͨ������ABRDBITS(UART_ALTCTL[20:19])���㡣����ABRDEN(UART_ALTCTL[18])��ʹ���Զ������ʹ��ܡ��ڿ�ʼ��,UART RX������1��һ�����½���,�ͽ�����ʼλ���Զ������ʼ�������λ����ʼ������������һ��������ʱ,�Զ������ʼ�������ֹͣ��Ȼ��,�Զ������ʼ�����ֵ����2ABRDBITS(UART_ALTCTL[20:19])�Զ����ص�BRD(UART_BAUD[15:0])��ABRDEN(UART_ALTCTL[18])��������Զ���������ͼ6.5-1��ʾ���Զ������ʲ�����ɺ�,����ABRDIF(UART_FIFOSTS[1])�����Զ������ʼ��������ʱ,����ABRDTOIF(UART_FIFOSTS[2])��ABRDIF(UART_FIFOSTS[1])��ABRDTOIF(UART_FIFO STS[2])�����Զ������ʱ�־ABRIF(UART_ALTCTL[17])���ɡ����ABRIEN(UART_INTEN[18])ʹ��,��ABRIF(UART_ALTCTL[17])�ᵼ���Զ��������ж�ABRINT(UART_INTST[31])���ɡ�

ͼ6.5-1 �Զ������ʲ���

�������ʾ��:

1.���ABRDBITS(UART_ALTCTL[20:19])��2ABRDBITSλʱ��ȷ��UART RX���ݴ�START��ʼ�ĵ�һ��������ʱ�䡣

2.����ABRIEN(UART_INTEN[18])ʹ���Զ������ʹ����жϡ�

3.����ABRDEN(UART_ALTCTL[18])ʹ���Զ������ʹ��ܡ�

4.����ABRDIF(UART_FIFOSTS[1]),����Զ������ʲ�����

5.����UART���ͺͽ��ն�����

6.����Զ������ʼ��������,������ABRDTOIF(UART_FIFOSTS[2])��

7.ת������3��

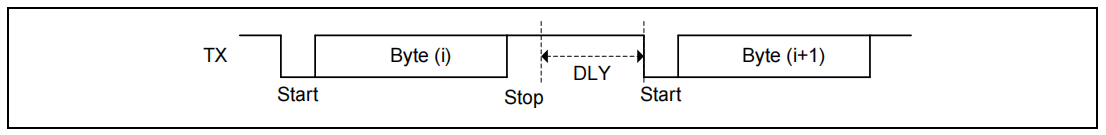

6.5.4,UART�����������ӳ�ʱ��ֵ

UART��������DLY(UART_TOUT[15:8])���б��,�Կ��ƴ��������һ��ֹͣλ����һ����ʼλ֮��Ĵ����ӳ�ʱ�䡣�����Ԫ�Dz��صġ�������ͼ6.5-2��ʾ��

ͼ6.5-2 �����ӳ�ʱ�����

6.5.5,UART������FIFO���ƺ�״̬

UART����������16�ֽڷ�����FIFO(TX_FIFO)��16�ֽڽ�����FIFO(RX_FIFO),�ɼ����ṩ��CPU���ж�������CPU�����ڲ����ڼ���ʱ��ȡUART��״̬�������״̬��Ϣ����UART����ִ�еĴ�����������,�Լ����������������żУ�顢֡���жϴ���ʱ������3����������(��żУ�����֡�����ж��ж�)��UART��IrDA��LIN��RS485ģʽ֧��FIFO���ƺ�״̬���ܡ�

6.5.6,UART���������ѹ���

UART������֧�ֻ���ϵͳ���ܡ����ѹ��ܰ���nCTS���š��������ݻ��ѡ���������FIFO�ﵽ��ֵ���ѡ�RS-485��ַƥ��(AADģʽ)���Ѻͽ�������FIFO��ֵ��ʱ���ѹ��ܡ�CTSWKF(UART_WKSTS[0])��DATWKF(UART_WKSTS[1])��RFRTWKF(UART_WKSTS[2])��RS485WKF(UART_WKSTS[3])��TOUTWKF(UART_WKSTS[4])���������жϱ�־WKIF(UART_INTSTS[6�����WKIEN(UART_INTEN[6])ʹ��,�����жϱ�־WKIF(UART_INTSTS[6])���������ж�WKINT(UART_INTSTS[14])��

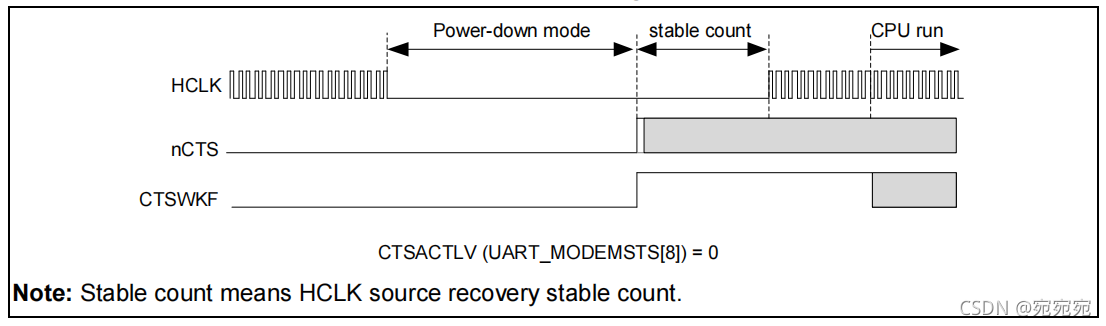

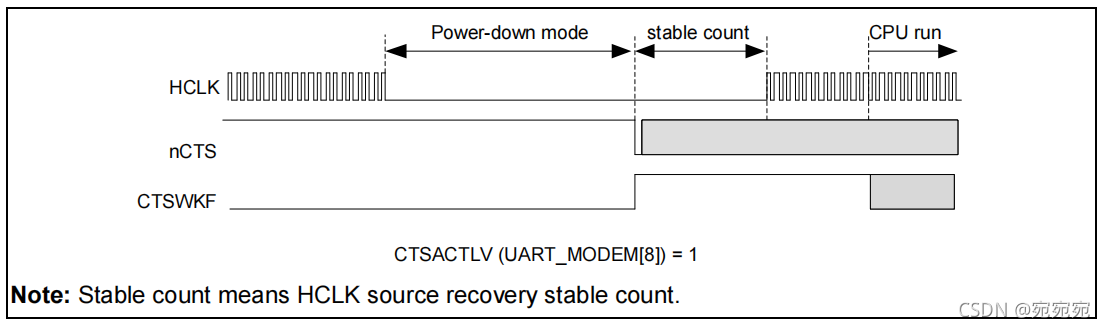

NCTS���Ż���:��ϵͳ���ڵ���ģʽ��������WKCTSEN(UART_WKCTL[0])ʱ,nCTS���ŵ��л����Ի���ϵͳ�����ʹ��WKCTSEN(UART_WKCTL[0]),��nCTS���ŵ��л������nCTS���ѱ�־CTSWKF(UART_WKSTS[0])��NCTS������ͼ6.5-3-5��ͼ6.5-4��ʾ��

ͼ6.5-3 NCTS���Ѱ���1(nCTS�ӵ͵��ߵ�ת��)

ע:�ȶ�������ζ��HCLKԴ�ָ��ȶ�������

ͼ6.5-4 NCTS���Ѱ���2(nCTS�Ӹߵ��͵�ת��)

ע:�ȶ�������ζ��HCLKԴ�ָ��ȶ�������

�������ݻ���

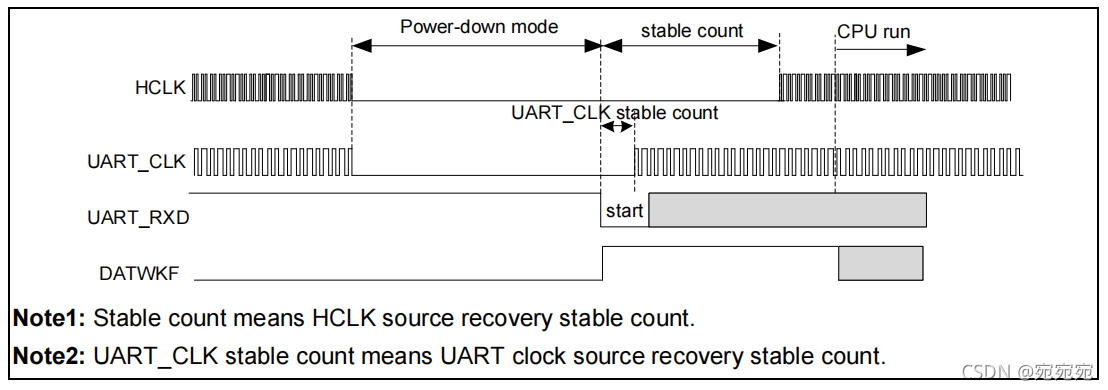

��ϵͳ���ڵ���ģʽ��������WKDATEN(UART_WKCTL[1])ʱ,��������(UART_RXD)���ŵ��л����Ի���ϵͳ��Ϊ����ϵͳ���Ѻ������������,Ӧ����STCOMP(UART_DWKCOMP[15:0])��STCOMP����Щλ�ֶα�ʾ��ϵͳ�ӵ���ģʽ����ʱ,UART_CLKѡ���˶��ٸ�ʱ������,UART���������Ի�õ�һλ(��ʼλ)��

���������ݻ���ϵͳʱ,�������ݽ������ղ��洢��FIFO�С����WKDATEN(UART_WKCTL[1])ʹ��,����������(UART_RXD)���ŵ��л�������������ݻ��ѱ�־DATWKF(UART_WKSTS[1])����������ݻ�����ͼ6.5-5��ʾ��

ע1:UART������ʱ��ԴӦѡ��ΪHIRC,��ʼλ����ʱ��ԼΪ8.602us����ʾSTCOMP(UART_DWKCOMP[15:0])��ֵ��������Ϊ0x68��

ע2:BRD(UART_BAUD[15:0])��ֵӦ����STCOMP(UART_DWKCOMP[15:0])��

ͼ6.5-5 UART���ݻ���

ע1:�ȶ�������ʾHCLKԴ�ָ��ȶ�������

ע2:UART_CLK�ȶ�������ʾUARTʱ��Դ�ָ��ȶ�������

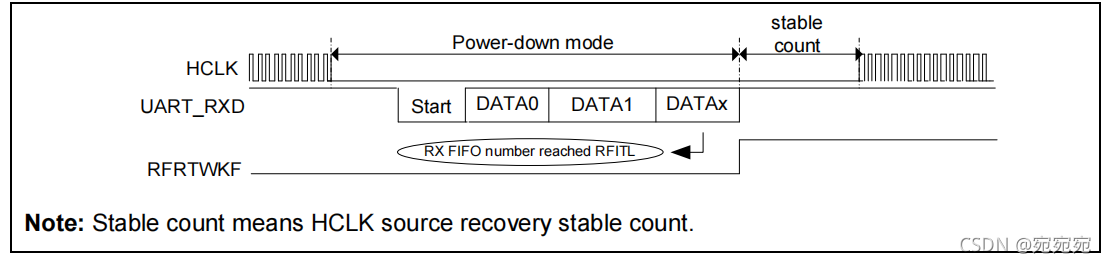

��������FIFO�ﵽ��ֵ����

ͨ������WKRFRTEN(UART_WKCTL[2])���ý�������FIFO��ֵ�ﵽ���ѹ��ܡ��ڵ���ģʽ��,��RX FIFO�н��յ����������ﵽ��ֵRFITL(UART_FIFO[7:4])ʱ,���Ի���ϵͳ�����WKRFRTEN(UART_WKCTL[2])ʹ��,��RX FIFO�еĽ������������ﵽ��ֵRFITL(UART_FIFO[7:4]),�Ӷ����ɽ�������FIFO�ﵽ��ֵ���ѱ�־RFRTWKF(UART_WKSTS[2])����������FIFO�ﵽ��ֵ������ͼ6.5-6��ʾ��

ע:�ڵ���ģʽ��,Ӧѡ��UART������ʱ��Դ��ΪLXT�Խ�������

ͼ6.5-5 UART��������FIFO�ﵽ��ֵ����

ע:�ȶ�������ζ��HCLKԴ�ָ��ȶ�����

RS-485��ַƥ��(AADģʽ)����,��������FIFO��ֵ��ʱ������,��������ֲ�

6.5.7,UART�������жϺ�״̬

ÿ��UART������֧��10�����͵��ж�,����:

- �������ݿ����ж�;

- ���䱣�ּĴ������ж�;

- ���������ж�;

- ������״̬�ж�;

�C�ж��жϱ�־;

�C��֡�����־;

�C��żУ������־;

�CRS-485��ַ�ֽڼ���־(ADDRDETF) - ���ƽ����״̬�ж�(MODEMINT);

�C���NCTS״̬���ı�־(CTSDETF); - ��������������ʱ�ж�;

- �����������ж�;

�CTX��������жϱ�־;

�CRX��������жϱ�־; - LIN�����ж�(LININT);

�CLIN�жϼ���־ (BRKDETF);

�Cλ������״̬��־(BITEF);

�CLIN��ID��żУ������־(SLVIDPEF);

�CLIN������ͷ�����־(SLVHEF);

�CLIN������ͷ����־(SLVHDETF) - �����ж�(WKINT);

�C nCTS���ѱ�־(CTSWKF);

�C�������ݻ��ѱ�־(DATWKF);

�C��������FIFO�ﵽ��ֵ���ѱ�־(RFRTWKF);

�CRS-485��ַƥ��(AADģʽ)���ѱ�־(RS485WKF);

�C��������FIFO��ֵ��ʱ���ѱ�־(TOUTWKF) - �Զ��������ж�(ABRINT);

�C�Զ������ʼ���жϱ�־(ABRDIF)

�C�Զ������ʼ�ⳬʱ�жϱ�־(ABRDTOIF)

��6.6�������ж�Դ�ͱ�־�������жϱ�־�������ж�ʹ��λʱ,�������жϡ��û��������ж����ɺ�����жϱ�־��

��6.6 UART�������ж�Դ�ͱ�־�б�

��ͷ:�ж�Դ �ж�ָʾ�� �ж�����λ �жϱ�־ ��־ ��ʼ�� ��־�����

N/A:Not Applicable

6.5.8,UART����ģʽ

UART�������ṩUART����(��FUNCSEL(UART_FUNCSEL[1:0])����Ϊ��00��������UART����ģʽ)��UART�����ʸߴ�1Mbps��

UART�ṩȫ˫�����첽ͨ�š��������ͽ���������������Ч�غɵ�16�ֽ�FIFO���û����ԶԽ��������崥����ƽ�ͽ��������峬ʱ�����б�̡�ͨ������DLY(UART_TOUT[15:8])�Ĵ���,���Զ���һ��ֹͣλ����һ����ʼλ֮��ķ��������ӳ�ʱ����б�̡�UART֧��Ӳ���Զ���������,���ṩ�ɱ��NRT�������ƴ�������RX FIFO�е������ֽ������ڻ����RTSTRGLV(UART_FIFO[19:16]),��ȡ����NRT����λ��

UART��·���ƹ���

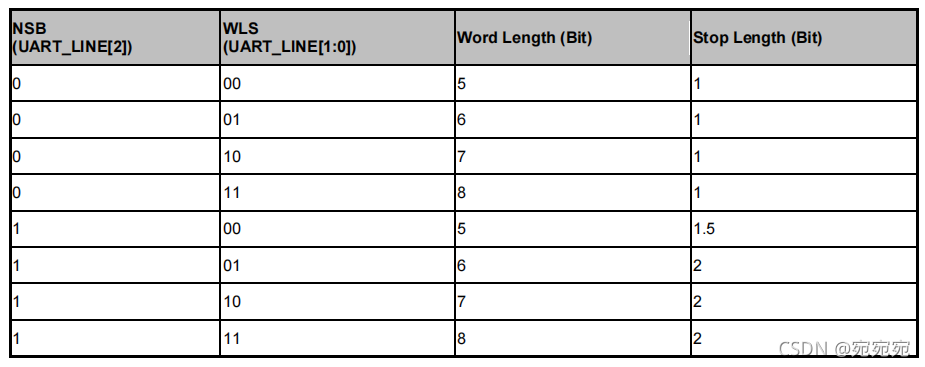

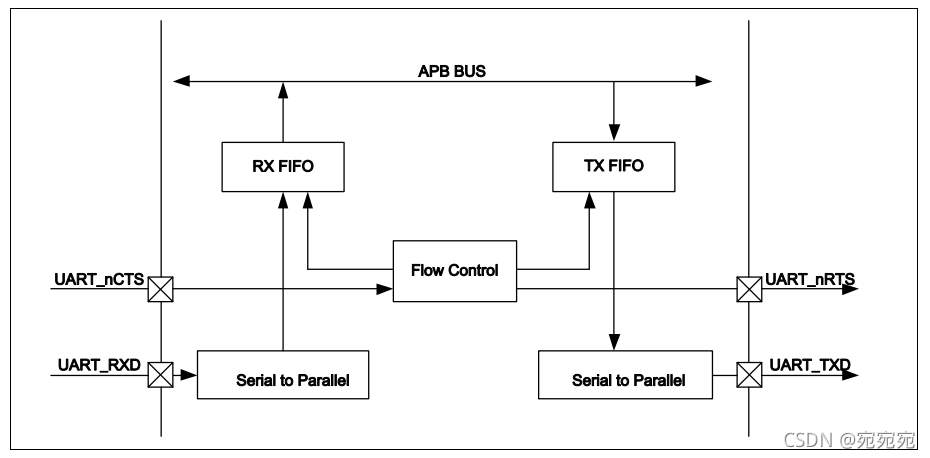

ͨ������UART_LINE�Ĵ���,UART������֧����ȫ�ɱ�̵Ĵ��нӿ����ԡ��û����Զ�UART_LINE�Ĵ������ֳ���ֹͣλ����żУ��λ���ý��б�̡���6.7�ͱ�6.18�г���UART�֡�ֹͣλ���Ⱥ���żУ��λ���á�

��6.7 UART�߿����ֺ�ֹͣ��������

��6.8 ��żУ��λ���õ�UART��·����

ע:

- ������żУ����ͨ�����������е����С�1�����,������żУ��λ���ӵ��ܱ������������,��ʹ�ܼ���Ϊ����;

- żУ��ͨ�����������е����С�1����Ӳ�����żУ��λ���ӵ��ܱ���������ż����żУ��,��ʹ����Ϊż��;

- ǿ��������żУ��:��żУ��λ������1�����ۡ�1���������Ƕ���(ż��������),�����ֽ��ϵ���żУ��λ������Ϊ��1����

- ǿ�ƿռ���żУ��:��żУ��λʼ����0�����ۡ�1���������Ƕ���(ż��������),�����ֽ��ϵ���żУ��λ������Ϊ��0����

UART�Զ��������ƹ���

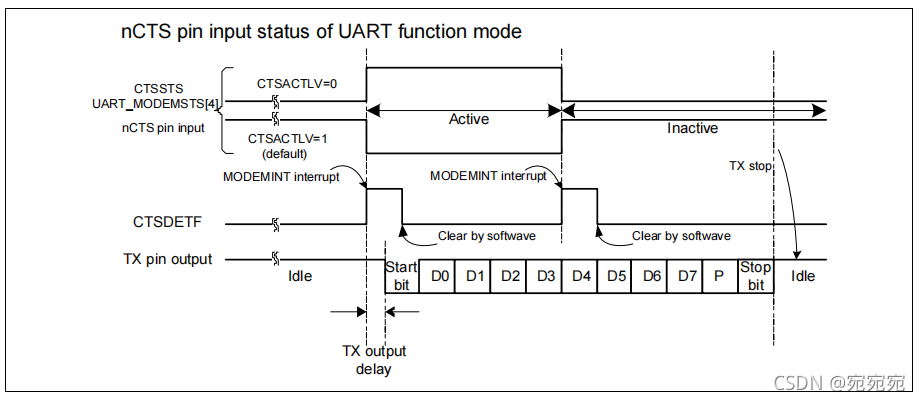

UART֧���Զ��������ƹ���,�ù���ʹ�������ź�nCTS(�������)��nRTS(������)������UART���ⲿ�豸(������ƽ����)֮������������䡣���Զ���ʹ��ʱ,��UART��nRTS��λ���ⲿ�豸֮ǰ,������UART�������ݡ���RX FIFO�д洢���ֽ�������RTSTRGLV(UART_FIFO[19:16])��ֵʱ,nRTS��������ԡ���UART�������ⲿ�豸��nCTS������ʱ,UART�������ݡ����δ����Ч�Ķ���nCTS,��UART�����������ݡ��Զ��������ƿ�ͼ��ͼ6.5-6��ʾ��

ͼ6.5-6 �Զ��������ƿ�ͼ

ͼ6.5-7չʾ��UART����ģʽ��nCTS�Զ��������ơ��û���������ATOCTSEN(UART_INTEN[13])��������nCTS�Զ��������ƹ��ܡ�CTSACTLV(UART_MODEMSTS[8])��������nCTS�������뼤��״̬����nCTS�������뷢���κ�״̬�仯ʱ,����CTSDETF(UART_MODEMSTS[0]),Ȼ���Tx FIFO�Զ�����Tx���ݡ�

ͼ6.5-7 UART nCTS�Զ���������������

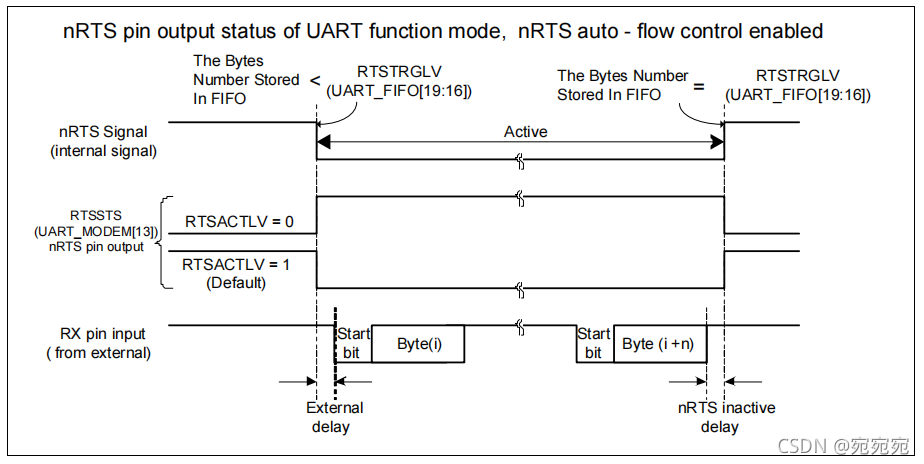

��ͼ6.5-8��ʾ,��UART NRTS�Զ���������ģʽ��(ATORTSEN(UART_INTEN[12])=1),NRTS�ڲ��ź��ɾ���RTSTRGLV(UART_FIFO[19:16])������ƽ��UARTFIFO���������ơ�

����RTSACTLV(UART_MODEM[9])���Կ���NRTS���������NRTS�ź��෴���Dz��෴���û����Զ�ȡRTSSTS(UART_MODEM[13])λ,�Ի����ʵ��NRT���������ѹ��״̬��

ͼ6.5-8 UART nRTS�Զ���������������

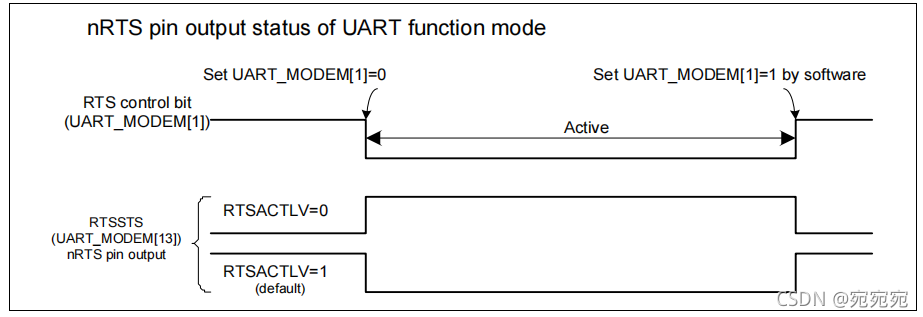

��ͼ6.5-9��ʾ,������ģʽ(ATORTSEN(UART_INTEN[12])=0)��,NRTS����ֱ����RTS(UART_MODEM[1])����λ��������̿��ơ�

����RTSACTLV(UART_MODEM[9])�ɸ���RTS(UART_MODEM[1])����λ����NRTS��������Ƿ�ת���ǷǷ�ת���û����Զ�ȡRTSSTS(UART_MODEM[13])λ,�Ի����ʵ��NRT���������ѹ��״̬��

ͼ6.5-9 ���������Ƶ�UART nRTS�Զ���ˮ��

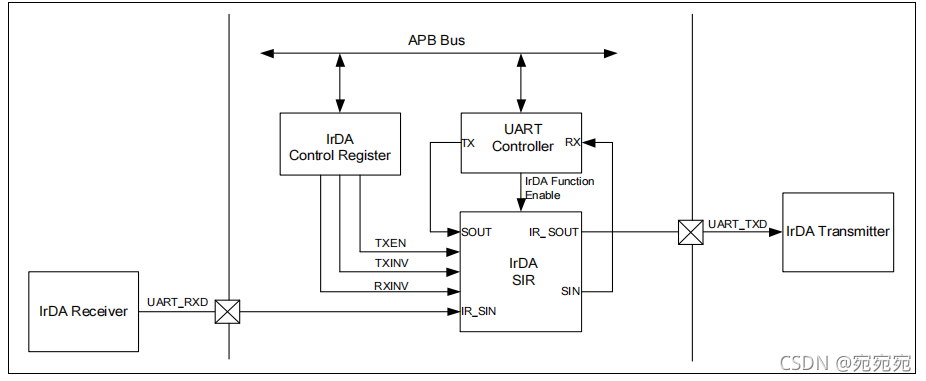

6.5.9,IrDA����ģʽ

UART���������ṩ����IrDA(SIR,���к���)����(��UART_FUNCSEL[1:0]����Ϊ��10��������IrDA����)��SIR�淶������һ�־���1����ʼλ��8������λ��1��ֹͣλ�Ķ̳̺����첽���д���ģʽ�������������Ϊ115.2 kbps��IrDA SIR�����IrDA SIRЭ�������/��������IrDA SIRЭ���Ϊ��˫�������,������ͬʱ����ͽ������ݡ�IrDA SIR������涨����ͽ���֮�����С�����ӳ�Ϊ10 ms,���ӳٹ��ܱ���������ʵ�֡�

��IrDAģʽ��,�������BAUDM1(UART_Baud[29])��

������=ʱ��/(16*(BRD+2)) ,����BRD(UART_BAUD[15:0])��UART_BAUD�Ĵ����еIJ����ʷ�Ƶ����

ע:IrDA������IrDA�ӻ�֮��IJ������ݲ�Ϊ��5%��

IrDA���ƿ�ͼ��ͼ6.5-10��ʾ��

ͼ6.5-10 IrDA���ƿ�ͼ

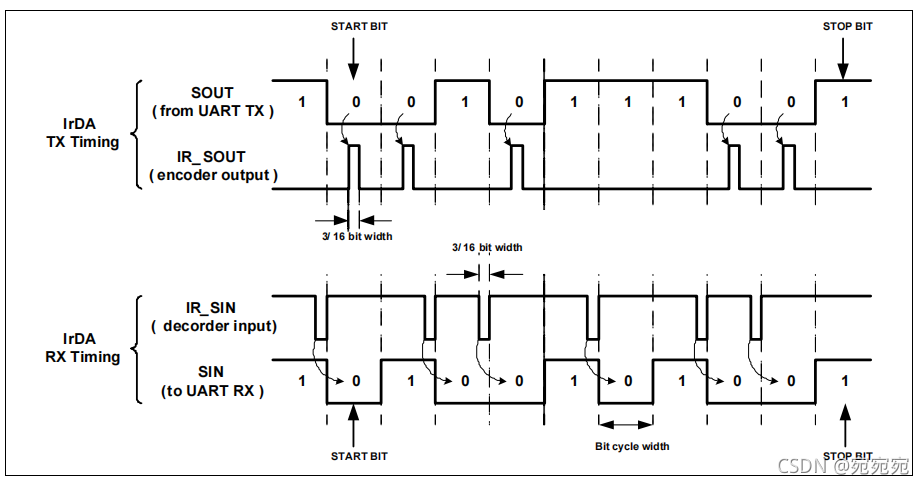

IrDA SIR���ͱ�����( IrDA SIR Transmit Encoder)

IrDA SIR���ͱ�������UART����ķǹ���(NRZ)����λ�����е��ơ�IrDA SIR������涨ʹ�ù��㷴ת(RZI)���Ʒ���,�÷�������0��ʾΪ��������塣���ƺ����������������䵽�ⲿ����������ͺ��ⷢ������ܡ�

�����������ָ��Ϊ�����ʵ�3/16����

IrDA SIR���ս�����(IrDA SIR Receive Decoder)

IrDA SIR���ս���������������������Ĺ��������,����NRZ���б����������UART���յ��������롣

�ڿ���״̬��,����������Ϊ�ߵ�ƽ��������������Ϊ��ʱ,����ʼλ��������������,RXINV(UART_IrDA[6])����Ϊ��1��,TXINV(UART_IrDA[5])����Ϊ��0����

IrDA SIR����

IrDA SIR������/�������ṩ��UART�������Ͱ�˫������SIR�ӿ�֮�����ת���Ĺ��ܡ�ͼ6.5-11ΪIrDA����������Ρ�

ͼ6.5-11 IrDA TX/RXʱ��ͼ

6.5.10,LIN����ģʽ(���ػ�������)

UART������֧��LIN���ܡ���FUNCSEL(UART_FUNCSEL[1:0])����Ϊ��01����ѡ��LINģʽ������UART������֧��LIN����ģʽ�µ�LIN�ж�/�ָ������ɺ��ж�/�ָ������,��֧��LIN��ģʽ�µı�ͷ�����Զ�����ͬ����

LIN֡�ṹ

����LINЭ��,���д������Ϣ�����Ϊ֡;֡��ͷ��(���������ṩ)����Ӧ(�ɴ������ṩ)��ɡ���ͷ(���������ṩ)��һ���ж����һ��ͬ�������,���һ��֡��ʶ��(֡ID)��֡��ʶ��Ψһ�ض���֡��Ŀ�ġ�ָ���������������ṩ��֡ID���������Ӧ����Ӧ�������ֶκ�У����ֶ���ɡ�

LIN�ֽڵĽṹ

��LINģʽ��,����LIN��,ÿ���ֽ��ֶ���һ��ֵΪ0(����)����ʼλ����,Ȼ����8������λ������żУ��λ,LSB������ֵΪ1(����)��1��ֹͣλ,�����ֵΪ1(����)��ֹͣλ��

LIN����ģʽ

UART������֧��LIN����ģʽ��Ҫʹ�ܲ���ʼ��LIN����ģʽ,��Ҫִ�����²���:

- ����UART_BAUD�Ĵ�����ѡ������IJ����ʡ�

- ��WLS(UART_LINE[1:0])����Ϊ��11����8λ�����ֳ�,���PBE(UART_LIN E[3])λ�Խ�����żУ��,�����NSB(UART_LIN E[2])λ������һ��ֹͣλ��

- ��FUNCSEL(UART_FUNCSEL[1:0])����Ϊ��01��,ѡ��LIN����ģʽ������

������,��������ֲ�

6.5.11,RS-485����ģʽ

UART����������һ�����������RS-485����(�û����뽫UART_FUNCSEL[1:0]����Ϊ��11����������RS-485����),�Լ���NRTS���Ŵ��첽���ж˿��ṩ�ķ�����ơ�RS-485�շ���������ͨ��ʹ��NRTS�����ź�ʹ��RS-485��������ʵ�ֵġ�RX��TX������������RS-485ģʽ�µ�UART��ͬ��

UART��������������ΪRS-485��Ѱַ�ӻ�,RS-485����������ͨ������żУ��(��9λ)����Ϊ1��ʶ���ַ�ַ������������ַ�,��żУ������Ϊ0��������ʹ��UART_LINE�Ĵ������Ƶ�9λ(��PBE��EPE��SPE����ʱ,��9λ����0,��PBE��SPE������EPE��0ʱ,��9λ����1)��

�ÿ�����֧�����ֹ���ģʽ:RS-485������㹤��ģʽ(NMM)��RS485�Զ���ַ����ģʽ(AAD)��RS-485�Զ�������ƹ���ģʽ(AUD)����������ͨ����UART_ALTCTL�Ĵ������б����ѡ���κι���ģʽ,��ͨ������DLY(UART_TOUT[15:8])�Ĵ����������뿪Tx FIFO�����һ��ֹͣλ���ȥ��λ֮��Ĵ����ӳ�ʱ�䡣

����ģʽ������,��������ֲ�

6.5.11,PDMA���亯��

UART������֧��PDMA���亯����ͨ������PDMA����,��UART_DAT����ΪPDMAĿ�ĵ�ַ����TXPDMAEN(UART_INTEN[14])����Ϊ1ʱ,����������PDMA�����������Զ���ʼPDMA������̵�����

ͨ������PDMA����,��UART_DAT����ΪPDMAԴ��ַ����RXPDMAEN(UART_INTEN[15])����Ϊ1ʱ,����������ʼPDMA���չ��̡���RX FIFO��������������ʱ,UART���������Զ���PDMA��������������

ע��: ���STOPn(PDMA_STOP[n])����ΪֹͣUART RXPDMA����,��UART����δ��ɡ�UART����������ɵ�ǰ���������ڽ��ջ������еĴ���ʹ洢��ͨ����ȡRXEMPTY(UART_FIFOSTS[14])�����ջ��������Ƿ�����Ч���ݡ�

6.5.12,Register Map and Register Description

��,��������ֲ�

ע:Ƶ��ֱ������͵õ�Ҫ��Ƶ�����������ĸ�����

�ο�����1: ���ڡ������ʵȸ���.

�ο�����2: �����ʡ�����/����ʱ�� ��������봫�����ʵĹ�ϵ�� .

�ο�����3: ʱ��Ƶ�ʡ������ʡ��������ӹ�ϵ���. ??