大家好,我是痞子衡,是正经搞技术的痞子。今天痞子衡给大家介绍的是i.MXRT1060/1170上的普通GPIO与高速GPIO极限翻转频率。

按照上一篇文章 《实测i.MXRT1010上的普通GPIO与高速GPIO极限翻转频率》 里的测试流程和方法,痞子衡今天带大家再测试下含有 HSGPIO 模块的 i.MXRT1060 和 i.MXRT1170 系列。从芯片整体性能上来说,它们俩都是 i.MXRT1010 的老大哥,但是老大哥未必是方方面面都碾压小老弟的,有时候芯片系统设计越复杂,细节之处反而越难优化。今天我们就来对比看看它们在 GPIO 上的表现:

- Note1: i.MXRT1064 跟 i.MXRT1060 是同一种 Die, GPIO 性能是一致的;i.MXRT1160 和 i.MXRT1170 在 GPIO 上性能也类似。

- Note2: 测量所用示波器型号是 Tektronix MSO5204,带宽 2GHz, 采样率 10GS/s。

一、i.MXRT1060(1064)上的测试

1.1 测试板卡及测试点

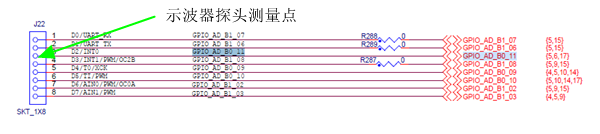

选定的板卡是恩智浦官方 MIMXRT1060-EVK,这次我们选了 Arduino J22 接口的 Pin3,即 GPIO_AD_B0_11,这个 PAD 既可以配到普通 GPIO(GPIO1[11]) 也可以配到 HSGPIO(GPIO6[11]),默认外围可选功能电路上的电阻都是 DNP 状态,因此这个 PAD 是悬空的:

1.2 I/O 翻转测试代码

测试工程我们可以直接在 \SDK_2.11.0_EVK-MIMXRT1060\boards\evkmimxrt1060\driver_examples\gpio\led_output 例程上修改,为了尽力展示 GPIO 极限性能,不受其他瓶颈因素干扰,这里选择代码执行性能最高的工程 build(即代码段在 ITCM 里,数据段在 DTCM 里)。I/O 测试代码很简单:

void io_test_init(bool useNormalGpio)

{

gpio_pin_config_t led_config = {kGPIO_DigitalOutput, 0, kGPIO_NoIntmode};

CLOCK_EnableClock(kCLOCK_Iomuxc);

IOMUXC_SetPinMux(IOMUXC_GPIO_AD_B0_11_GPIO1_IO11, 0U);

// Fast Slew Rate, R0/7, 200MHz

IOMUXC_SetPinConfig(IOMUXC_GPIO_AD_B0_11_GPIO1_IO11, 0x10F9U);

if (useNormalGpio)

{

// GPIO1

IOMUXC_GPR->GPR26 &= ~(1u << 11);

GPIO_PinInit(GPIO1, 11, &led_config);

}

else

{

// GPIO6

IOMUXC_GPR->GPR26 |= (1u << 11);

GPIO_PinInit(GPIO6, 11, &led_config);

}

}

void io_test_run(void)

{

io_test_init(false);

while (1)

{

GPIO6->DR_TOGGLE = 0x800;

}

}1.3 芯片系统时钟配置

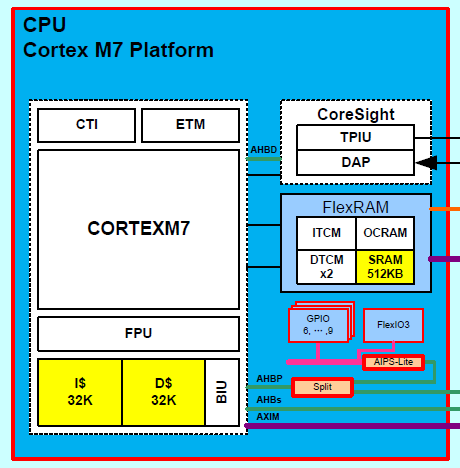

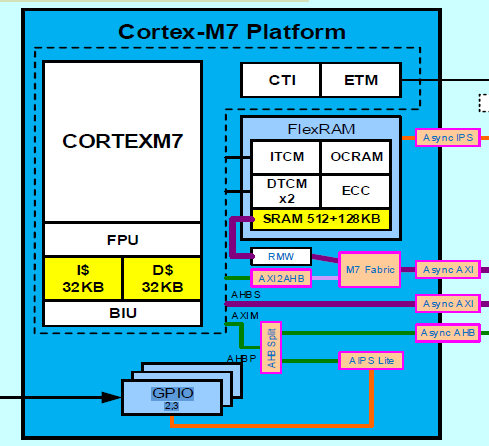

《普通GPIO与高速GPIO差异及其用法》 一文里讲了,普通 GPIO 时钟源是 IPG Bus,而 HSGPIO 时钟源是 AHB Bus,因此测试工程里 AHB/IPG 时钟配置会影响最终 I/O 翻转极限频率。下图是 i.MXRT1060 内核结构里的 HSGPIO 通路。

led_output 例程里的默认系统时钟配置,AHB/Core 时钟来自于 PLL1,将这个源配置为 1200 MHz,ARM_PODF 设 1(两分频),AHB_PODF 设 0 (即不分频),IPG Bus 时钟源固定来自于 AHB/Core,且只能在其基础上做 1/2/3/4 分频,我们知道 IPG Bus 最高仅支持 150MHz,因此在这种情况下 IPG_PODF 只能设 3(四分频),最终 AHB 时钟是 600MHz,IPG 时钟是 150MHz,HSGPIO 和 GPIO 访问可以同时得到最优性能(这点设计上是优于 i.MXRT1010 的)。

PPL1, CCM_ANALOG->PLL_ARM[DIV_SELECT] = 100,即 24MHz*DIV_SELECT/2 = 1200MHz

CCM->CACRR[ARM_PODF] = 3'b001,divide by 2

CCM->CBCMR[PRE_PERIPH_CLK_SEL] = 2'b11,derive clock from divided PLL1

CCM->CBCDR[PERIPH_CLK_SEL] = 1'b0,derive clock selected by CCM->CBCMR[PRE_PERIPH_CLK_SEL]

CCM->CBCDR[AHB_PODF] = 3'b000,divide by 1

CCM->CBCDR[IPG_PODF] = 2'b11,divide by 4

1.4 I/O 翻转测试结果

现在我们来看一下测试结果,根据实测结果,我们得到了如下结论:

- 总结1: PAD配置里的运行频率并不限制最终输出翻转频率,实际输出的波形幅值响应表现跟外围电路关系较大。

- 总结2: 置位 GPIO->DR_TOGGLE 寄存器可获得最佳 I/O 翻转性能

- 总结3: 普通 GPIO 翻转频率约是时钟源 IPG Bus 的 1/8,极限翻转频率是 18.69MHz

- 总结4: HSGPIO 翻转频率约是时钟源 AHB Bus 的 1/4,极限翻转频率是 149.24MHz

- 总结5: i.MXRT1060 的 GPIO 性能跟 i.MXRT1010 差不多,但是 HSGPIO 性能比 i.MXRT1010 差很多。

| AHB/Core时钟频率 | IPG总线时钟频率 | I/O PAD配置 | I/O翻转方法 | 普通GPIO极限翻转频率 | 高速GPIO极限翻转频率 |

|---|---|---|---|---|---|

| 600MHz | 150MHz | Fast Slew, 200MHz | 异或GPIO->DR | 6.289MHz 标准幅度方波 | 22.99MHz 标准幅度方波 |

| 600MHz | 150MHz | Fast Slew, 200MHz | 置位GPIO->DR_TOGGLE | 18.69MHz 标准幅度方波 | 149.24MHz 标准幅度正弦波 |

二、i.MXRT1170(1160)上的测试

2.1 测试板卡及测试点

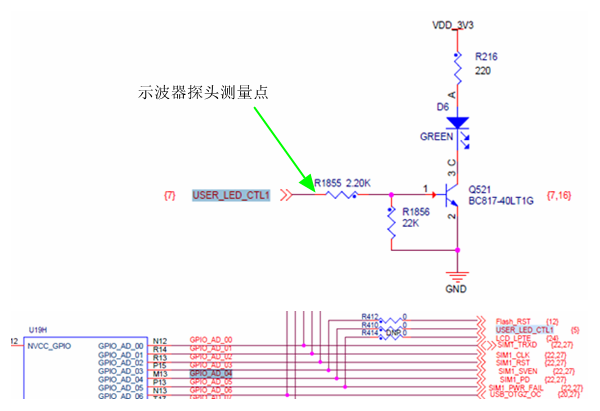

选定的板卡是恩智浦官方 MIMXRT1170-EVK,板卡上连接 LED 灯的是 GPIO_AD_04,翻看芯片参考手册,这个 PAD 既可以配到普通 GPIO(GPIO9[3] 或者 GPIO3[3]) 也可以配到 HSGPIO(CM7_GPIO3[3]),我们就选择这个 PAD 做测试。此外,最终 I/O 输出波形形态跟外围驱动电路也有关联,所以这里也有必要交待清楚:

2.2 I/O 翻转测试代码

测试工程我们可以直接在 \SDK_2.11.0_MIMXRT1170-EVK\boards\evkmimxrt1170\driver_examples\gpio\led_output\cm7 例程上修改,为了尽力展示 GPIO 极限性能,不受其他瓶颈因素干扰,这里选择代码执行性能最高的工程 build(即代码段在 ITCM 里,数据段在 DTCM 里)。I/O 测试代码很简单:

void io_test_init(bool useNormalGpio)

{

gpio_pin_config_t led_config = {kGPIO_DigitalOutput, 0, kGPIO_NoIntmode};

CLOCK_EnableClock(kCLOCK_Iomuxc);

IOMUXC_SetPinMux(IOMUXC_GPIO_AD_04_GPIO_MUX3_IO03, 0U);

if (useNormalGpio)

{

// GPIO3

IOMUXC_GPR->GPR42 &= ~(1u << 3);

GPIO_PinInit(GPIO3, 3, &led_config);

}

else

{

// CM7_GPIO3

IOMUXC_GPR->GPR42 |= (1u << 3);

GPIO_PinInit(CM7_GPIO3, 3, &led_config);

}

}

void io_test_run(void)

{

io_test_init(false);

while (1)

{

CM7_GPIO3->DR_TOGGLE = 0x8;

}

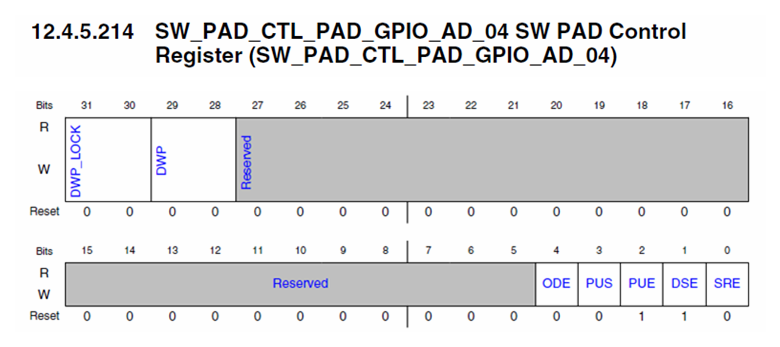

}特别提醒的是在 i.MXRT1170 IOMUXC 模块 SW_PAD_CTL 控制寄存器里取消了 SPEED 配置,并且 DSE 配置也从 3bit 减少到 1bit,这点跟 i.MXRT1010/1060 上设计不一样:

2.3 芯片系统时钟配置

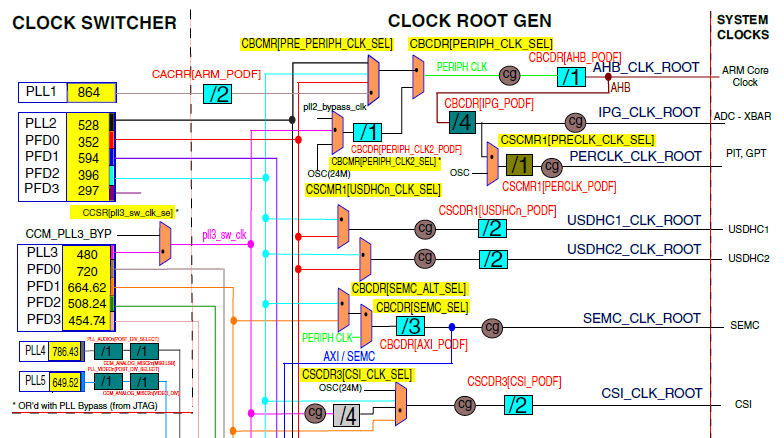

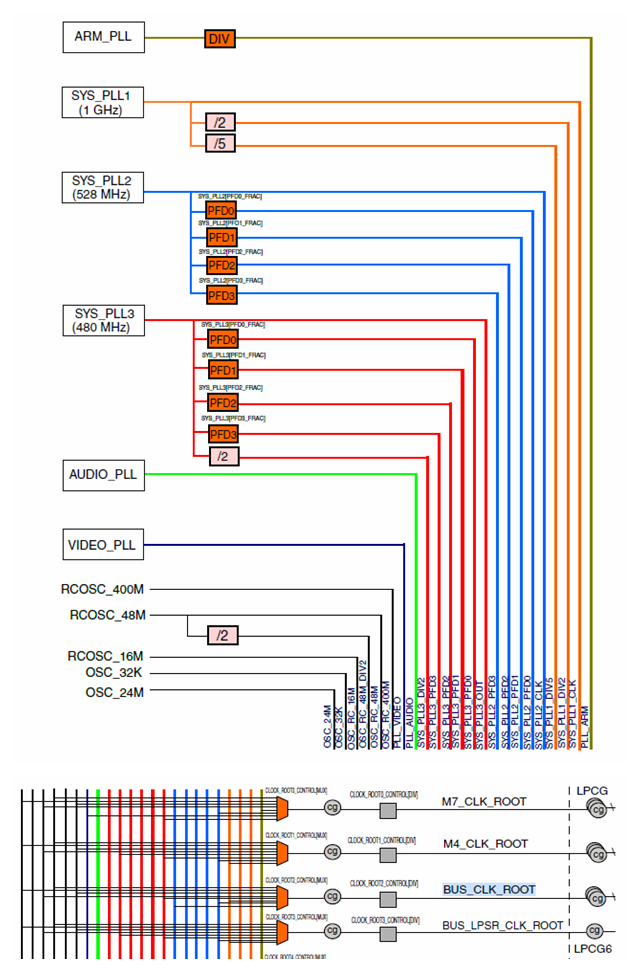

《普通GPIO与高速GPIO差异及其用法》 一文里讲了,普通 GPIO 时钟源是 IPG Bus(在 i.MXRT1170 里叫 BUS_CLK),而 HSGPIO 时钟源是 AHB Bus(在 i.MXRT1170 里叫 M7_CLK),因此测试工程里 AHB/IPG 时钟配置会影响最终 I/O 翻转极限频率。下图是 i.MXRT1170 内核结构里的 HSGPIO 通路。

- Note1: GPIO1 - 6 时钟源是 BUS_CLK,该总线最高频率 240MHz

- Note2: GPIO7 - 12 时钟源是 BUS_LPSR_CLK,该总线最高频率 160MHz

- Note3: GPIO13 时钟源是 RCOSC_32K

led_output 例程里的默认系统时钟配置,M7_CLK 时钟来自于 ARM_PLL,将这个源配置为 996 MHz。BUS_CLK 时钟来自于 SYS_PLL3,固定 480MHz,BUS_ROOT 配置里做了两分频,最终 M7_CLK 时钟是 996MHz,BUS_CLK 时钟是 240MHz(相较于 i.MXRT1010/1060 的最大 150MHz 有所提升),HSGPIO 和 GPIO 访问可以同时得到最优性能。此外,i.MXRT1170 的系统时钟设计是最灵活也最简单的。

ARM_PLL, 即 24MHz*DIV_SELECT/2/POST_DIV = 996MHz

ANADIG_PLL->ARM_PLL_CTRL[DIV_SELECT] = 166,

ANADIG_PLL->ARM_PLL_CTRL[POST_DIV_SEL] = 2'b00,Divide by 2

// 0 - CLOCK Root M7

CCM->CLOCK_ROOT[0].CONTROL[MUX] = 3'b100,PLL_ARM_CLK

CCM->CLOCK_ROOT[0].CONTROL[DIV] = 8'h00,Divider selected clock by DIV + 1.

SYS_PLL3, ANADIG_PLL->SYS_PLL3_CTRL[SYS_PLL3_GATE] = 1'b0,固定 480MHz

// 2 - CLOCK Root Bus

CCM->CLOCK_ROOT[2].CONTROL[MUX] = 3'b100,SYS_PLL3_CLK

CCM->CLOCK_ROOT[2].CONTROL[DIV] = 8'h01,Divider selected clock by DIV + 1.

2.4 I/O 翻转测试结果

现在我们来看一下测试结果,根据实测结果,我们得到了如下结论:

- 总结1: PAD配置里的运行频率并不限制最终输出翻转频率,实际输出的波形幅值响应表现跟外围电路关系较大。

- 总结2: 置位 GPIO->DR_TOGGLE 寄存器可获得最佳 I/O 翻转性能

- 总结3: 普通 GPIO 翻转频率约是时钟源 BUS_CLK 的 1/14,极限翻转频率是 17.12MHz

- 总结4: HSGPIO 翻转频率约是时钟源 M7_CLK 的 1/7.5,极限翻转频率是 131.4MHz

- 总结5: i.MXRT1170 的 GPIO 性能跟 i.MXRT1010/1060 差不多,但是 HSGPIO 性能比 i.MXRT1060 要稍差一些。

| M7_CLK时钟频率 | BUS_CLK时钟频率 | I/O PAD配置 | I/O翻转方法 | 普通GPIO极限翻转频率 | 高速GPIO极限翻转频率 |

|---|---|---|---|---|---|

| 996MHz | 240MHz | N/A | 异或GPIO->DR | 7.058MHz 标准幅度方波 | 41.24MHz 标准幅度方波 |

| 996MHz | 240MHz | N/A | 置位GPIO->DR_TOGGLE | 17.12MHz 标准幅度方波 | 131.4MHz 减半幅度正弦波 |

至此,i.MXRT1060/1170上的普通GPIO与高速GPIO极限翻转频率痞子衡便介绍完毕了,掌声在哪里~~~

欢迎订阅

文章会同时发布到我的 博客园主页、CSDN主页、知乎主页、微信公众号 平台上。

微信搜索"痞子衡嵌入式"或者扫描下面二维码,就可以在手机上第一时间看了哦。