PIC16(L)F1516/7/8/9通用,带有XLP技术的28/40/44针Flash微控制器

本数据表中包含的设备

?pic16f1516

?pic16f1517

pic16f1518 pic16lf1518

?pic16f1519

高性能的RISC CPU

?C编译器优化架构

?只有49指令

?操作速度:

- dc - 20 MHz时钟输入@ 2.5V

- dc - 16mhz时钟输入@ 1.8V

- dc - 200 ns指令周期

?中断能力与自动上下文保存

?16级深层硬件堆栈,可选溢出/下流复位

?直接、间接和相对寻址模式:

两个全16位文件选择寄存器(FSRs)

- fsr可以读取程序和数据存储器

内存

?高达28kbytes线性程序内存寻址

?高达1024字节的线性数据内存寻址

?High Endurance Flash Data Memory (HEF):

-128B的非易失性数据存储

?100 k擦除/写周期

灵活的振荡器结构

?16 MHz内部振荡器块:

-软件可选择的频率范围从16 MHz到31 kHz

?31 kHz低功率内部振荡器

?外部振荡器块:

-四种晶体/谐振模式高达20 MHz

-三种外部时钟模式,最高20 MHz

?自动防故障装置时钟监控:

-允许安全关闭,如果外围时钟停止

?双速振荡器启动

?振荡器启动定时器(OST)

模拟功能

?模拟-数字转换器(ADC):

10位分辨率

多达28个频道

汽车收购能力

-转换可在睡眠期间

?基准电压模块:

固定电压参考(FVR)与1.024V, 2.048V和4.096V输出电平

?温度指示器

ultra Low-Power (XLP) Management PIC16LF1516/7/8/9 with XLP

?睡眠模式:20 nA @ 1.8V,典型

?看门狗定时器:300na @ 1.8V,典型

?次级振荡器:600 nA @ 32 kHz

工作电流:30?A/MHz @ 1.8V,典型

特殊的微控制器的功能

?操作电压范围:

- 2.3 v - 5.5 v (PIC16F1516/7/8/9)

- 1.8 v - 3.6 v (PIC16LF1516/7/8/9)

在软件控制下可自行编程

?加电复位(运动)

?升高计时器(PWRT)

?低功率限电复位(lpor)

?扩展看门狗定时器(WDT)

通过两个引脚的在线串行编程?(ICSP?)

?通过两个引脚的在线调试(ICD)

?增强的低压编程(LVP)

?可编程代码保护

?低功耗睡眠模式

外围亮点

?多达35个I/O引脚和1个输入专用引脚:

-高电流接收器/源25 mA/25 mA

-单独可编程弱引体向上

-单独可编程中断更改(IOC)引脚

?Timer0: 8位定时器/计数器与8位预调节器

?增强Timer1:

-16位定时器/计数器与预调节器

-External Gate输入模式

-低功率32 kHz次级振荡器驱动器

?Timer2: 8位定时器/计数器与8位周期寄存器,预标器和后标器

?两个Capture/Compare (CCP)模块

主同步串行端口(MSSP)与SPI和I2C:

7位地址屏蔽

-SMBus / PMBusTM兼容性

?增强通用同步异步接收发射机(euusart)模块:

-RS-232, RS-485和LIN兼容

-Auto-Baud检测

-Auto-wake-up上开始

注1:I -调试,集成在芯片上;调试,可使用调试头文件。

2:单脚输入。

数据表索引:(无阴影的设备在本文档中进行了描述。)

数据表索引:(无阴影的设备在本文档中进行了描述。)

1: DS40001624 PIC16(L)F1512/13 Data Sheet, 28引脚Flash, 8位微控制器。

2: DS40001452 PIC16(L)F1516/7/8/9 Data Sheet, 28/40/44-Pin Flash, 8位mcu。

3: DS40001458 PIC16(L)F1526/27 Data Sheet, 64-Pin Flash, 8-bit mcu。

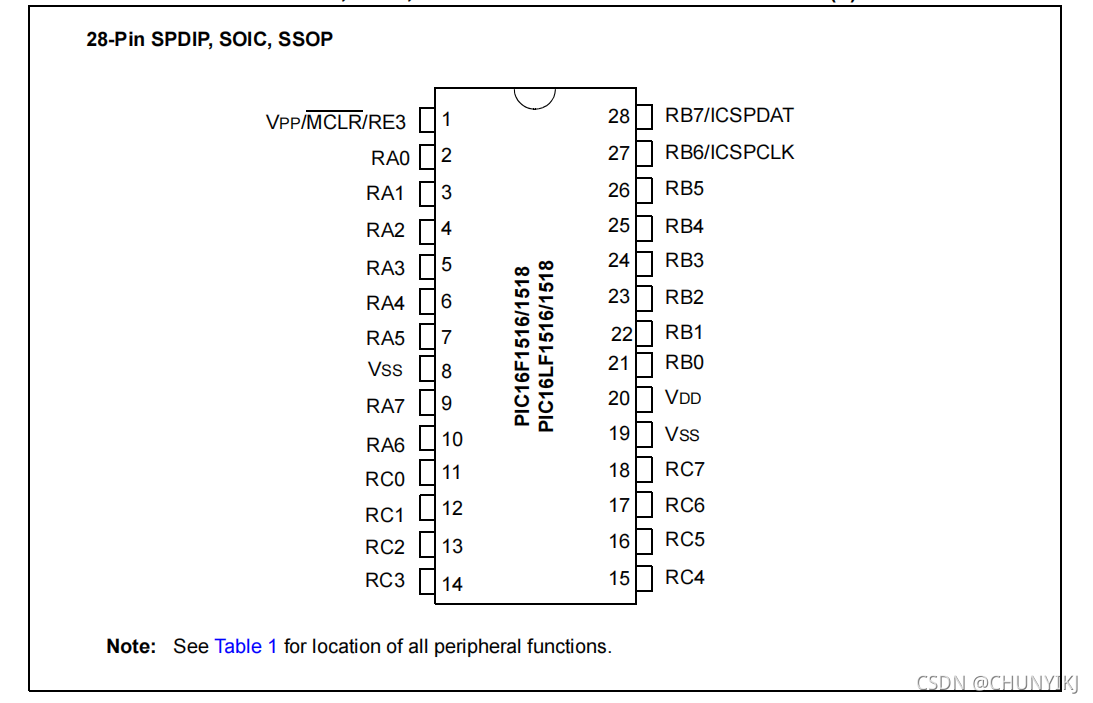

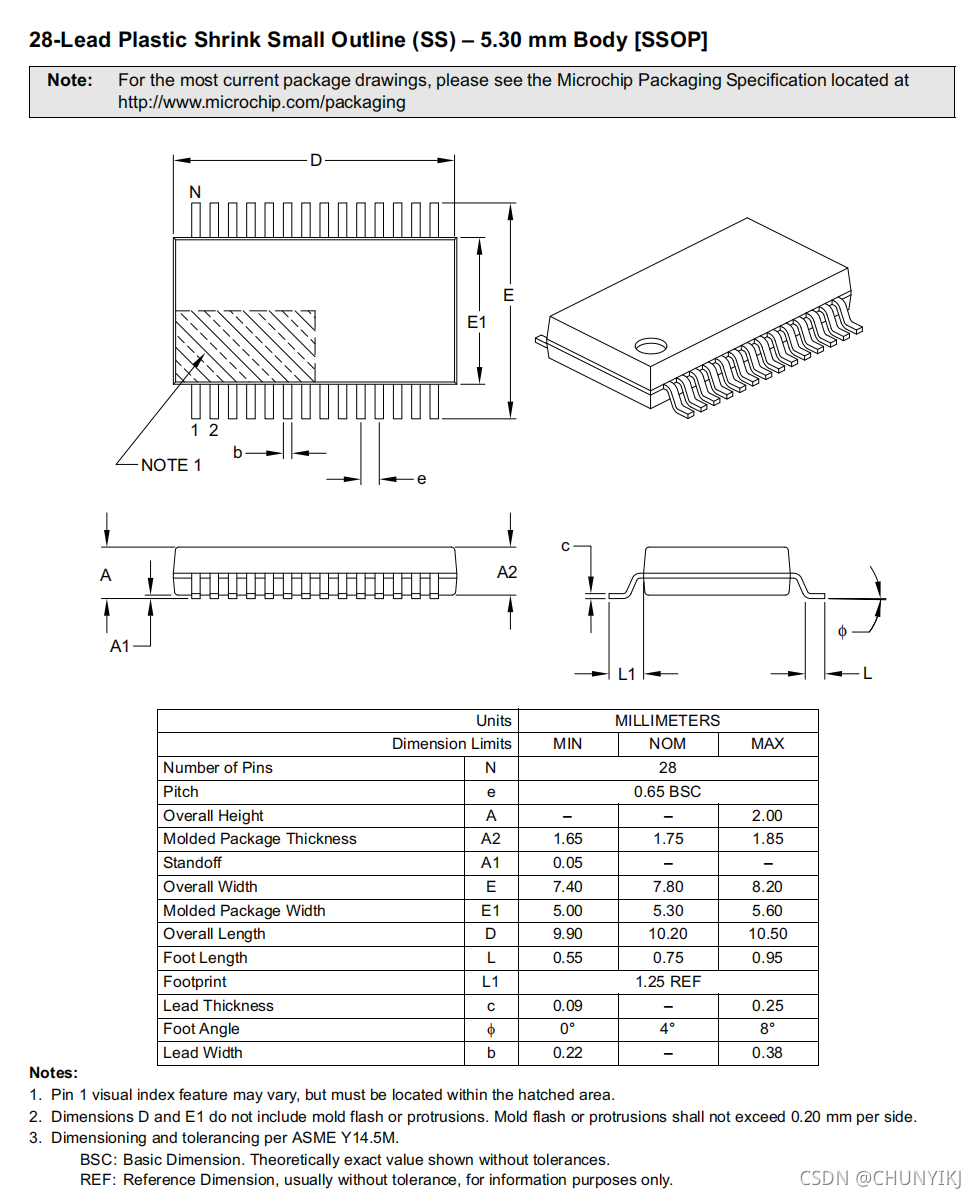

图1:pic16 (l) f1516/1518的28引脚spdip, soic, ssop包装图

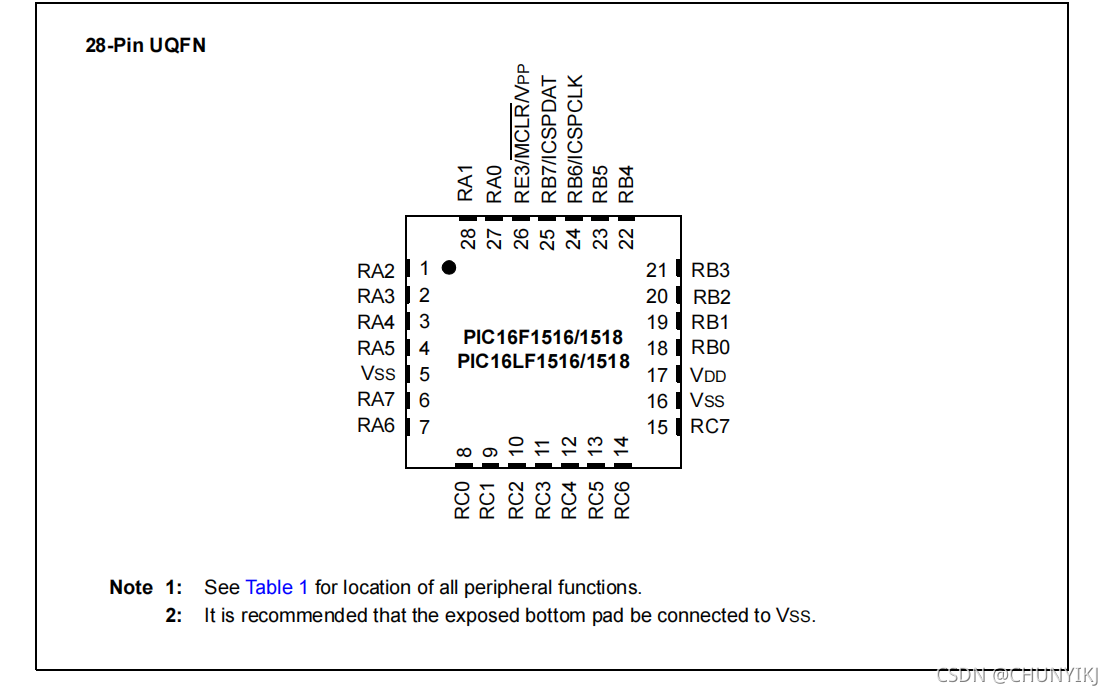

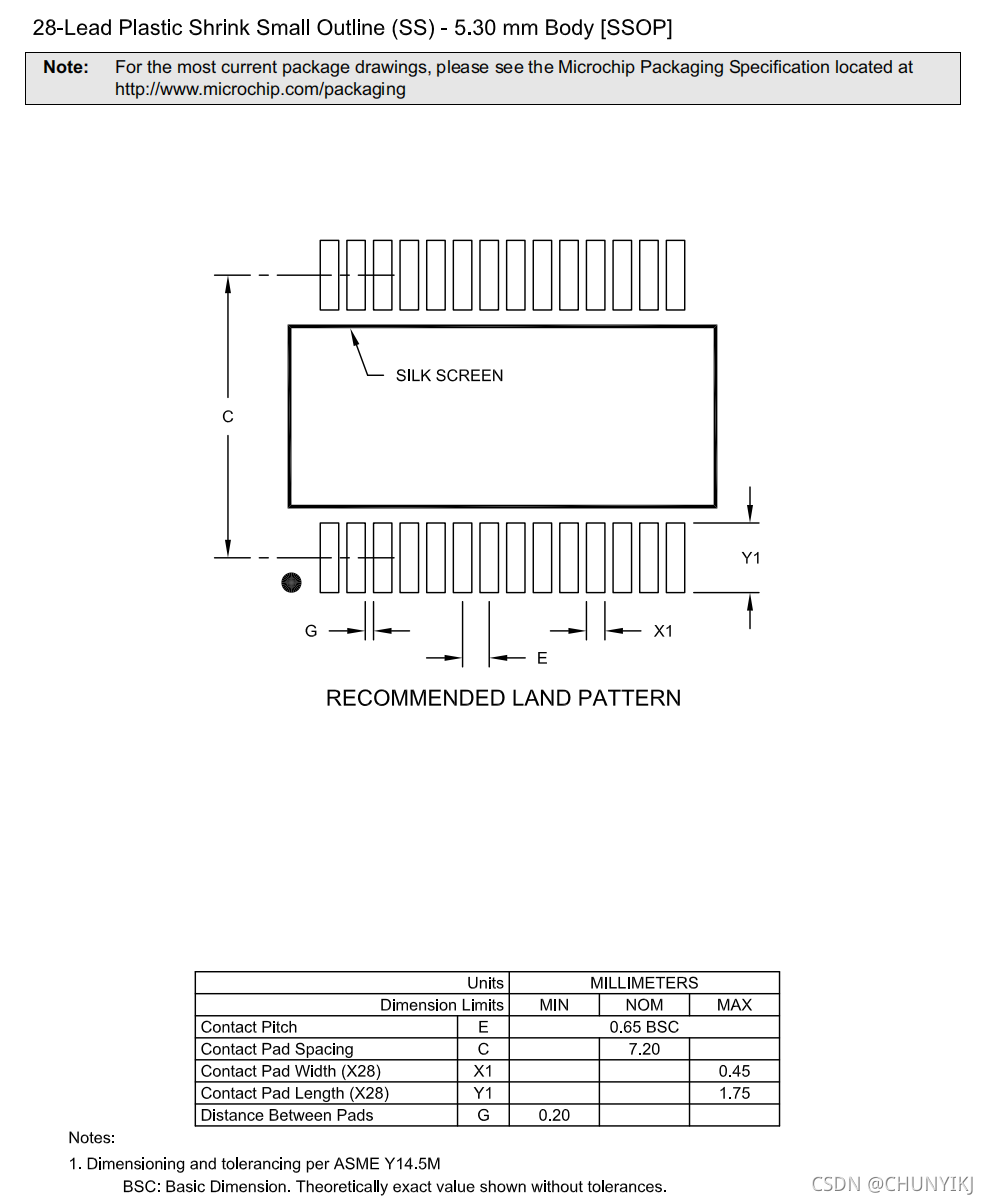

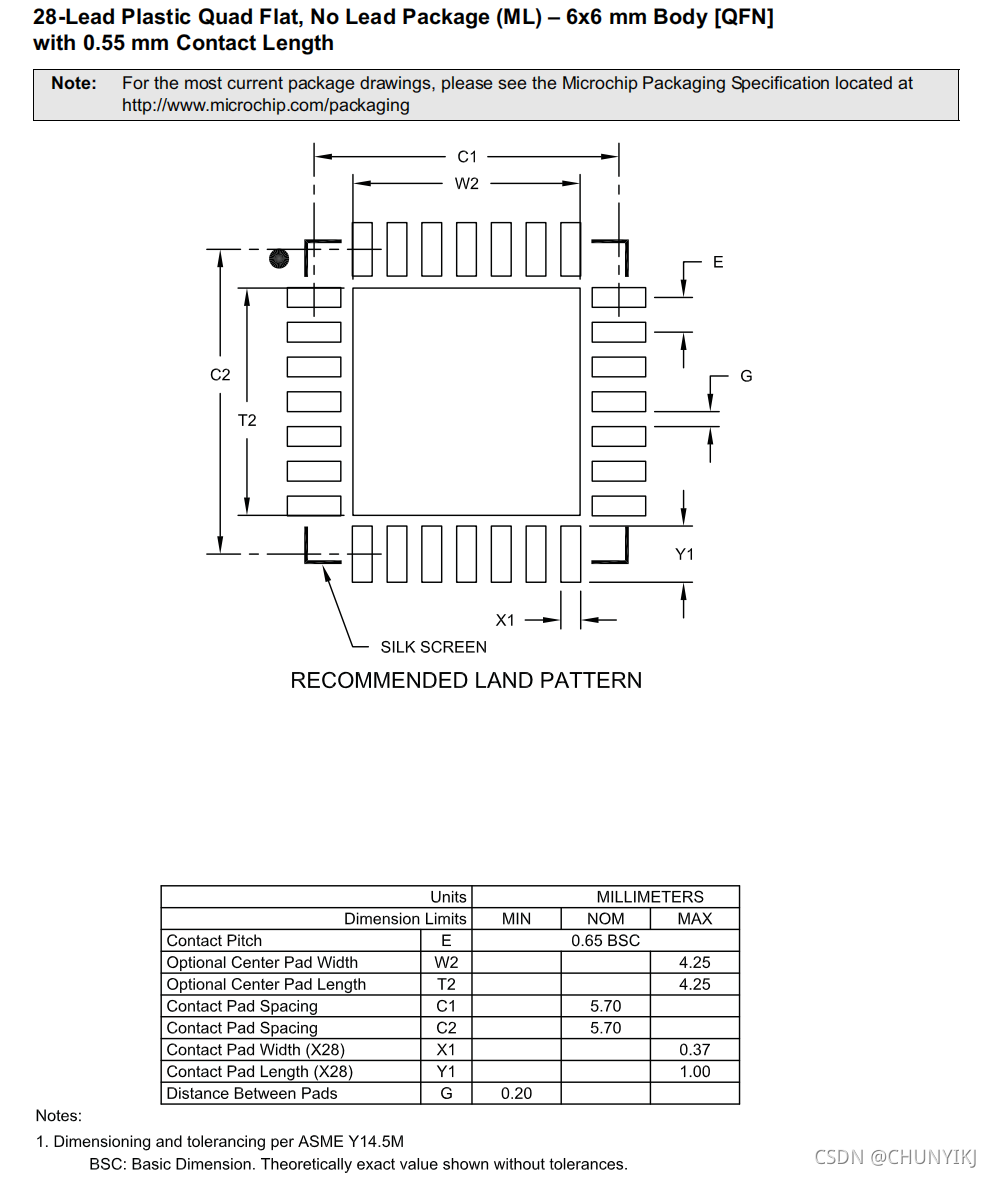

图2:pic16 (l) f1516/1518的28针uqfn (4x4)包装图

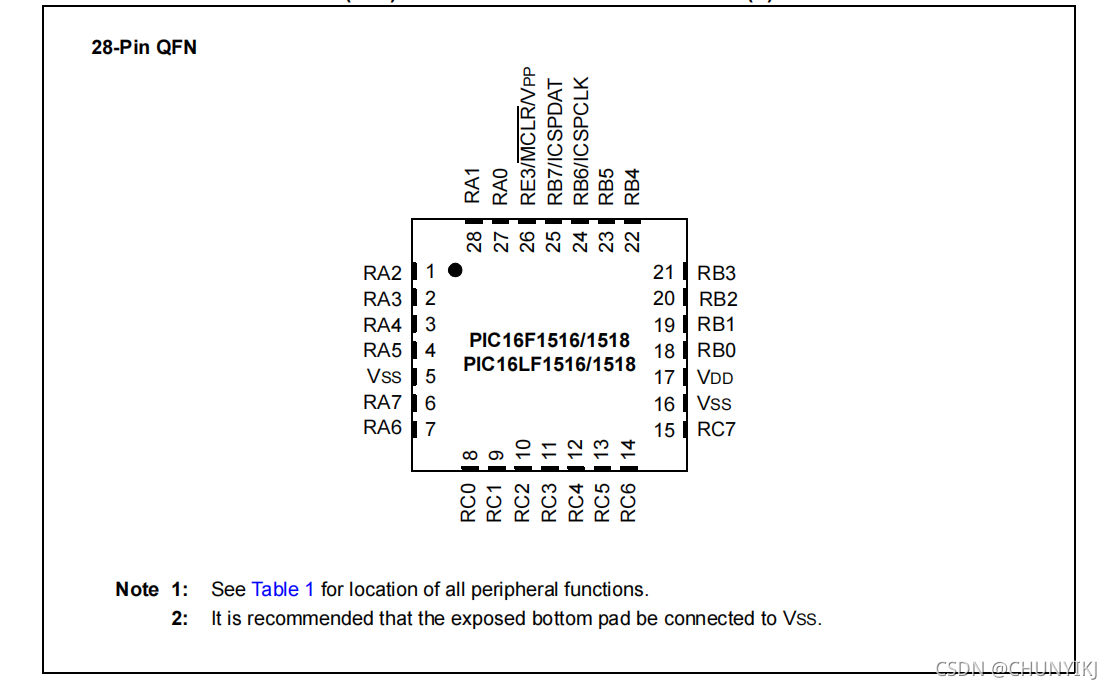

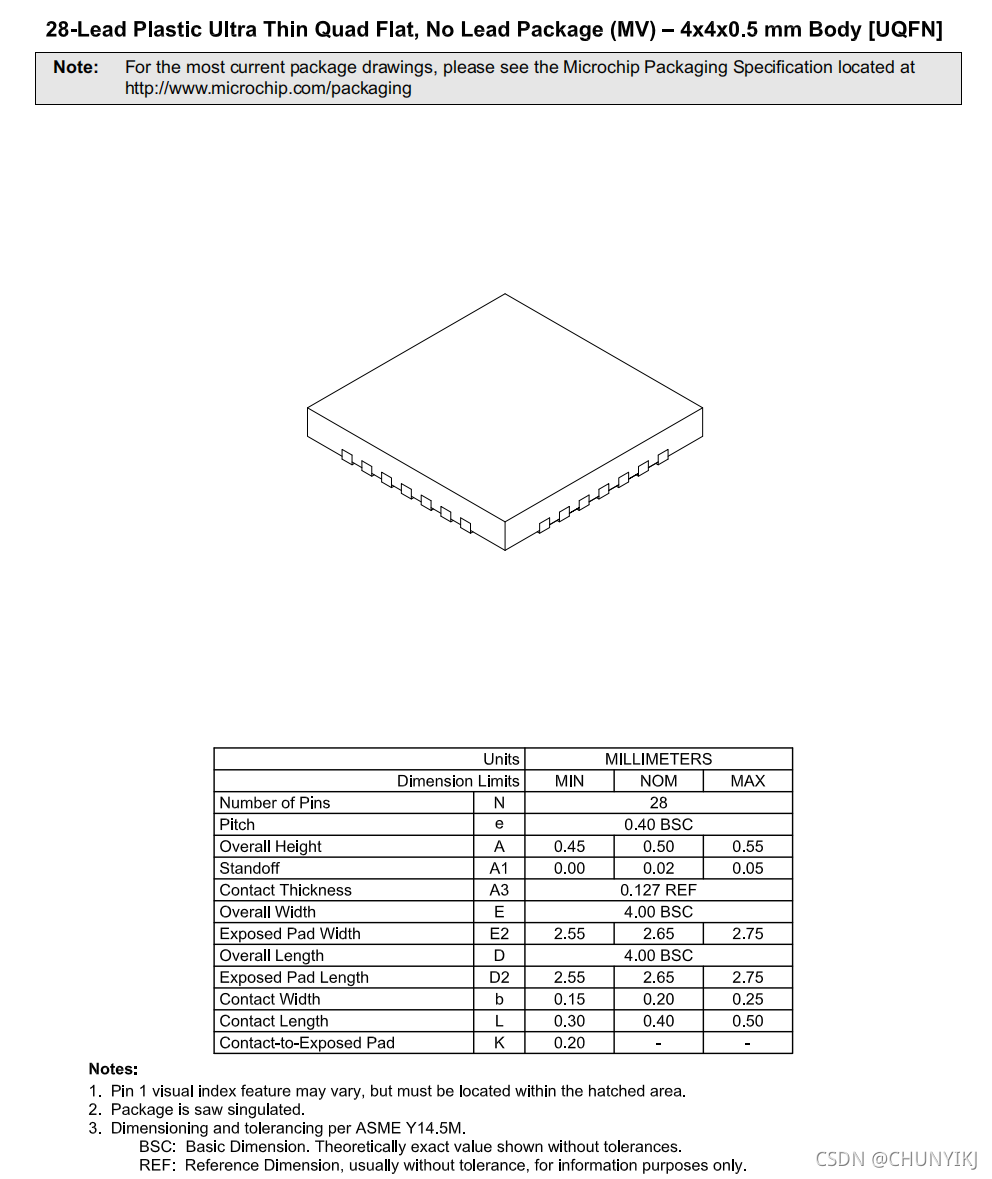

图3:pic16 (l) f1516/1518的28针QFN (6x6)包装图

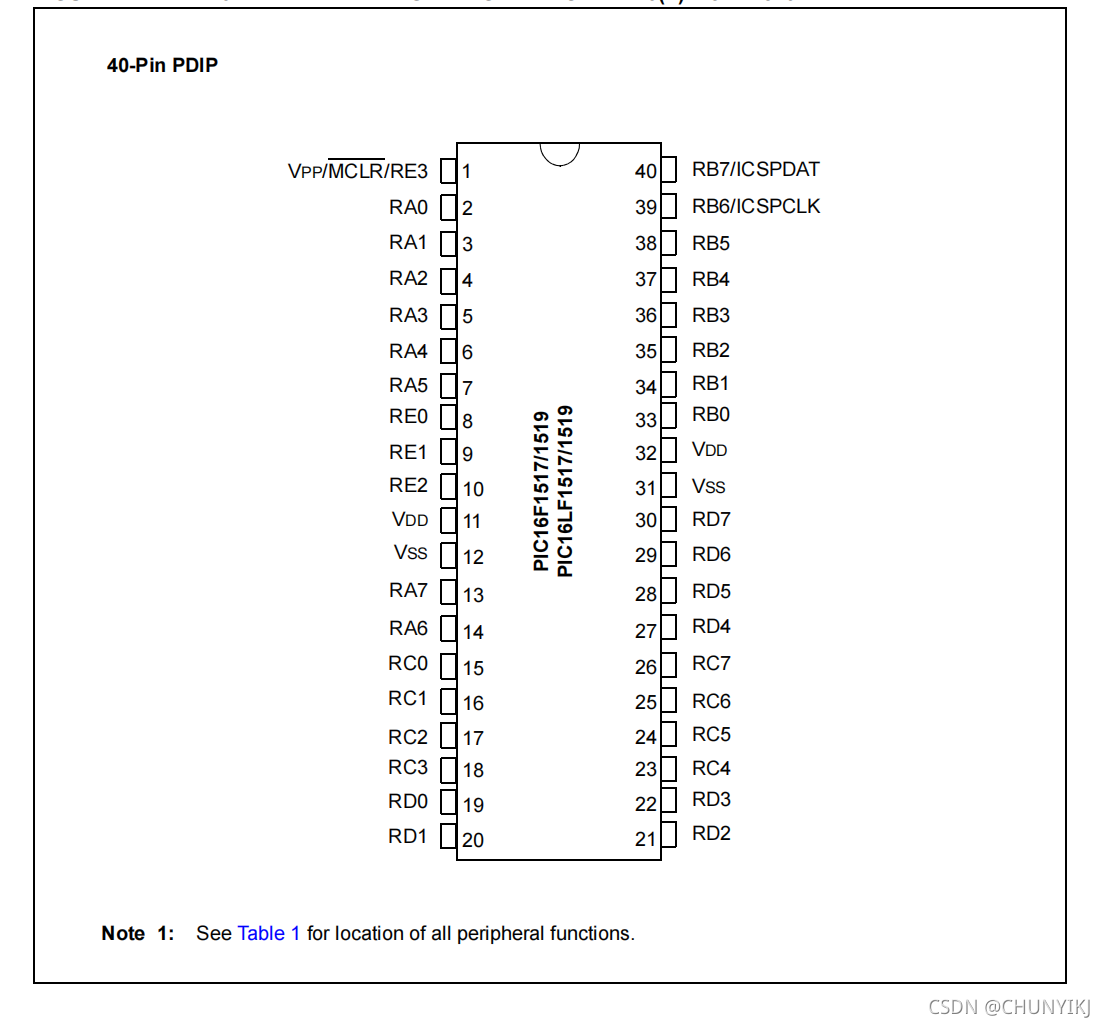

图4:pic16 (l) f1517/1519的40引脚pdip封装图

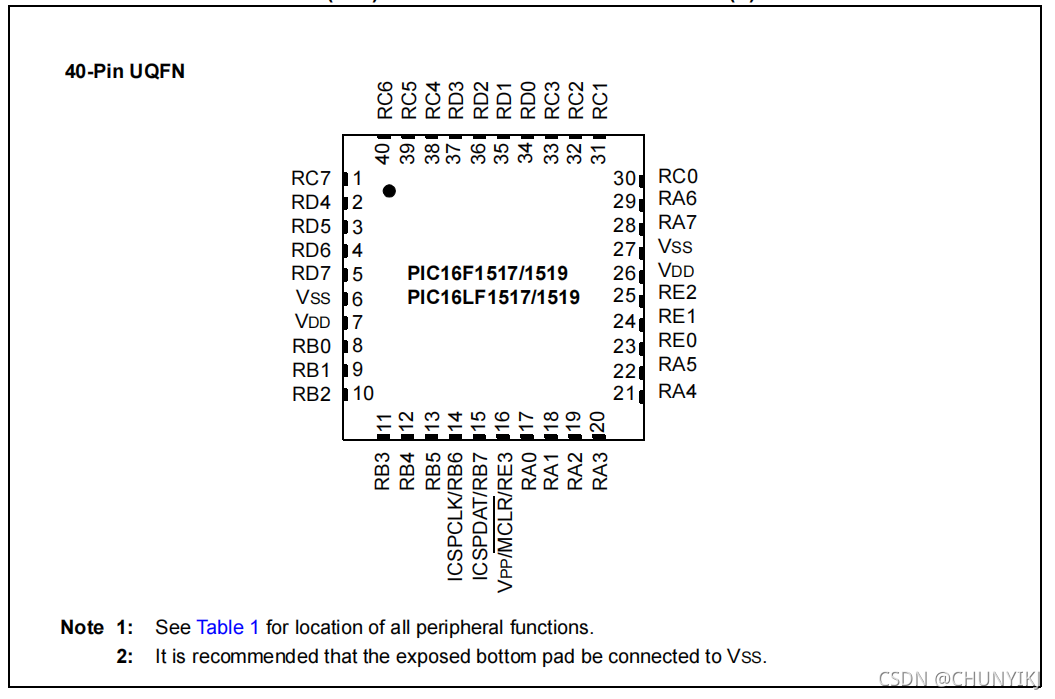

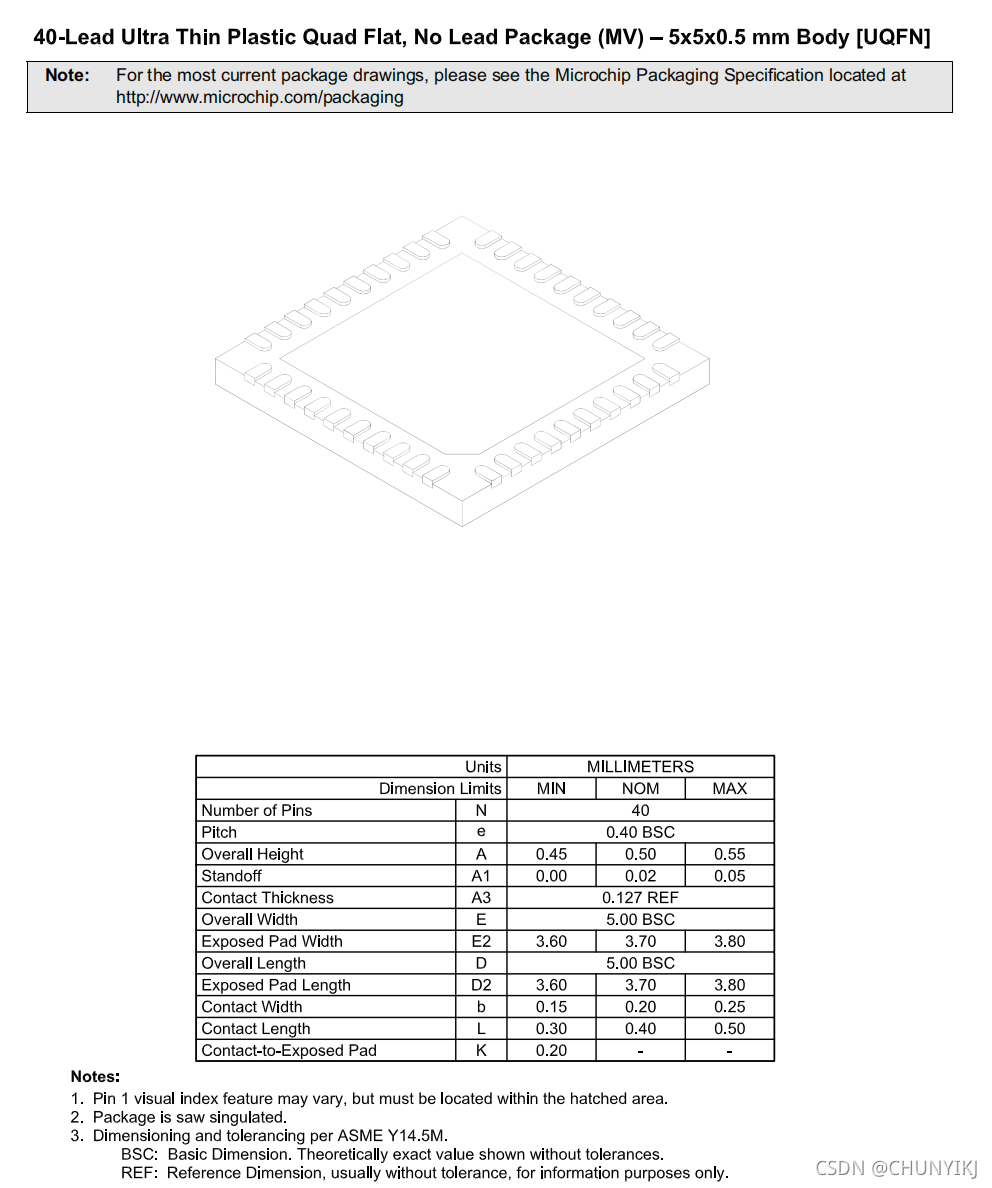

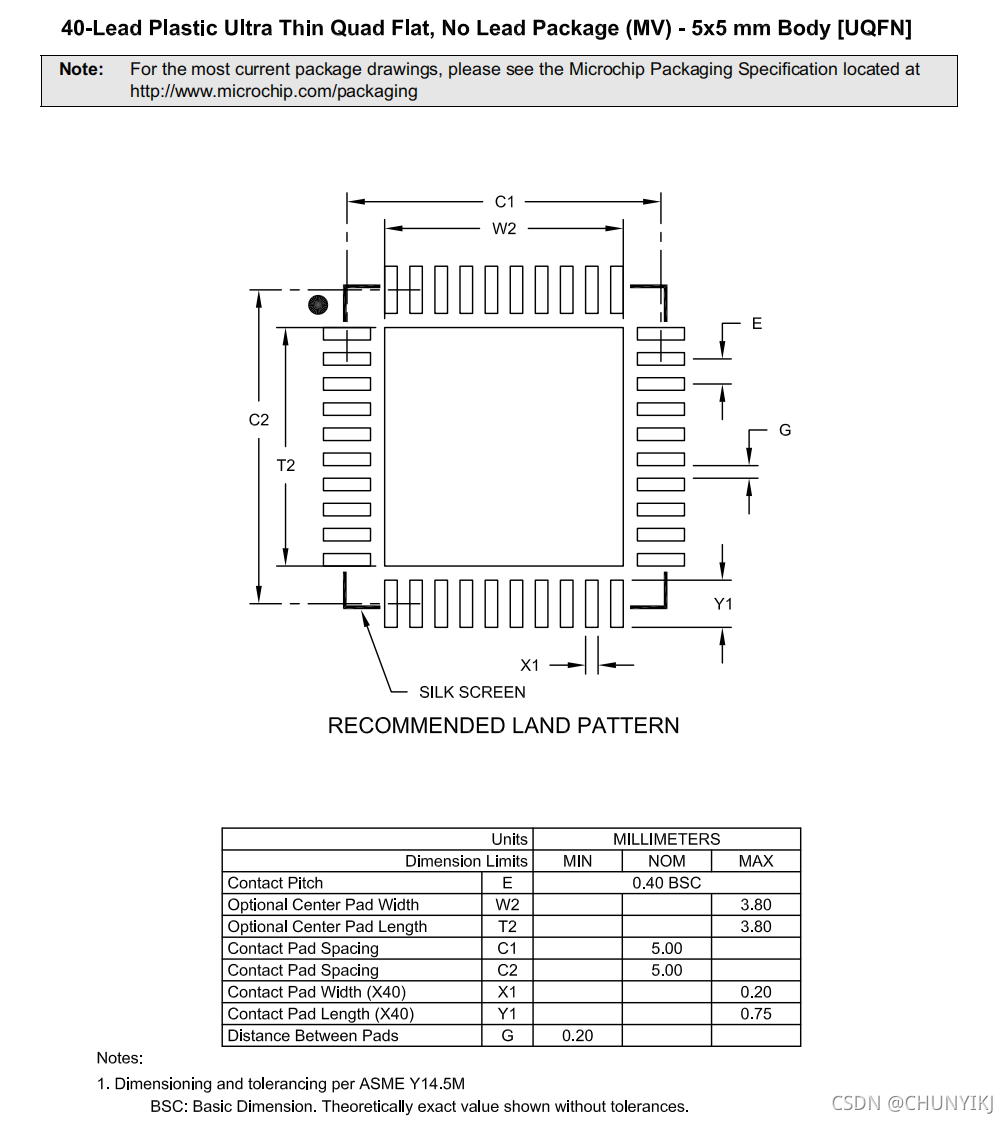

图5:pic16 (l) f1517/1519的40针uqfn (5x5)包装图

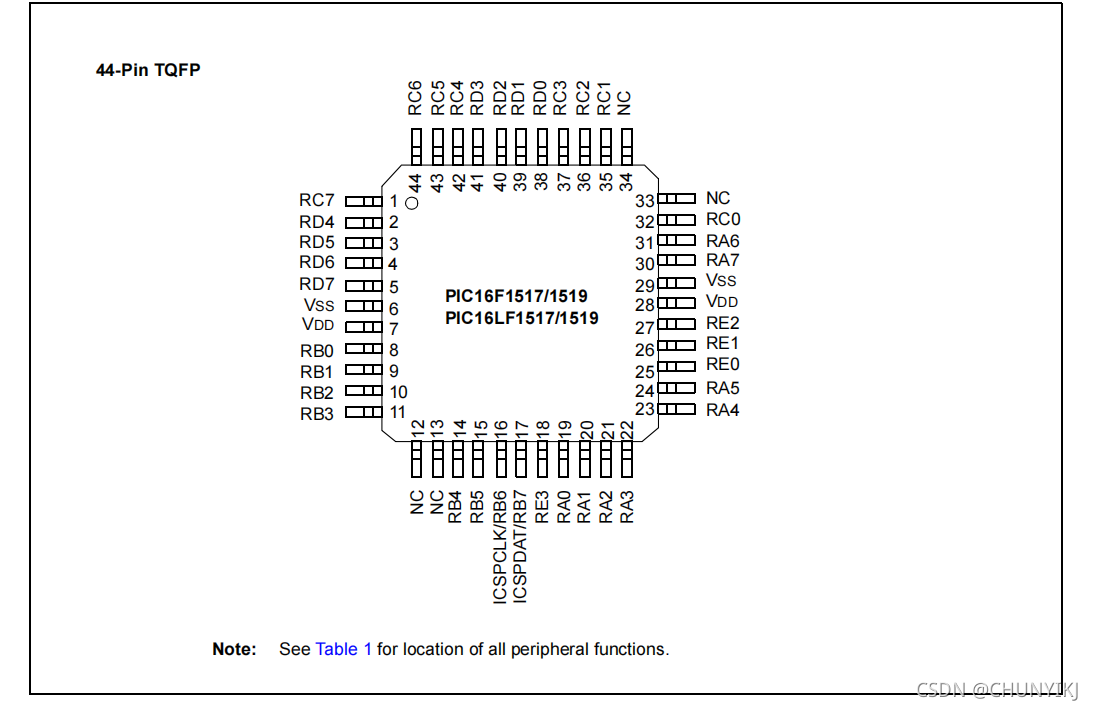

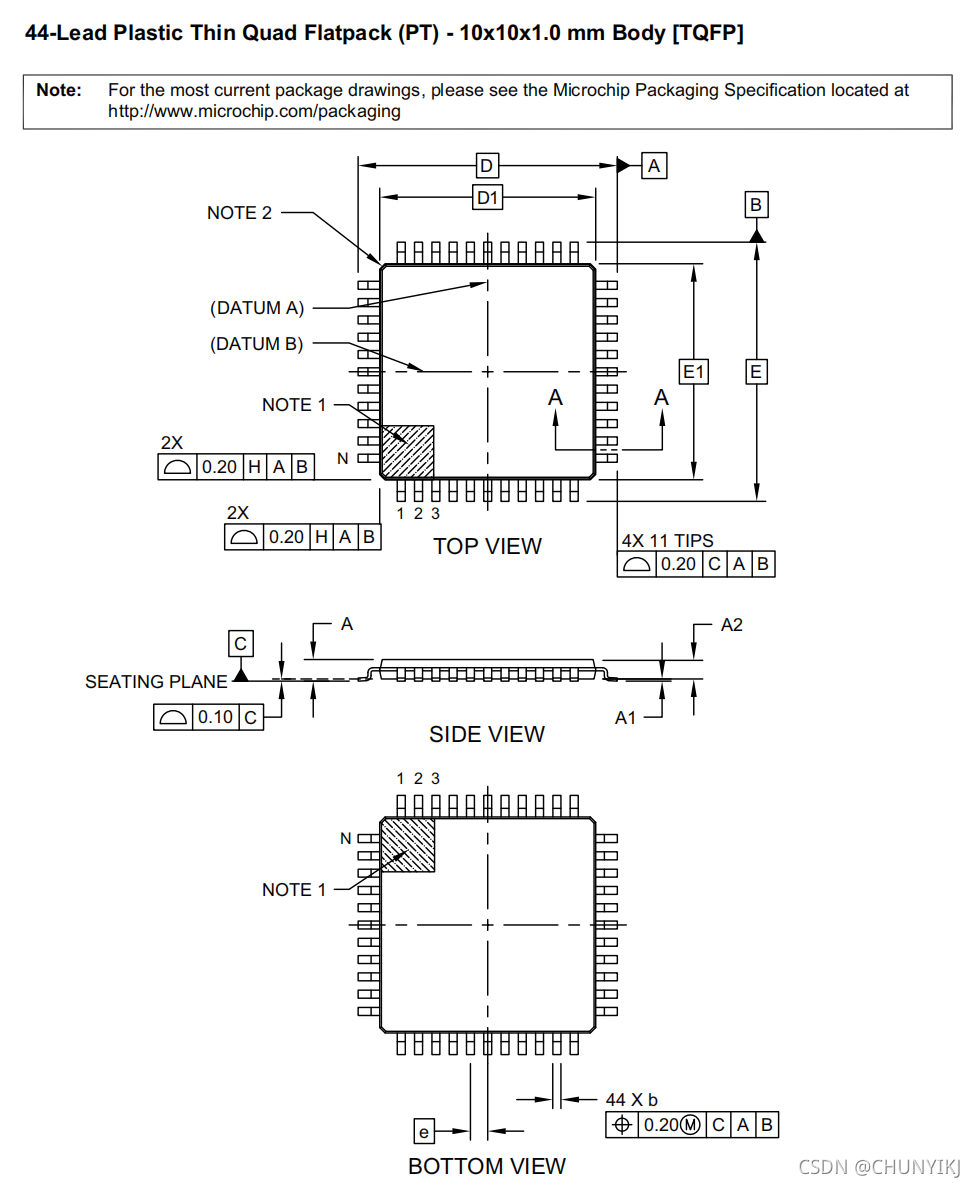

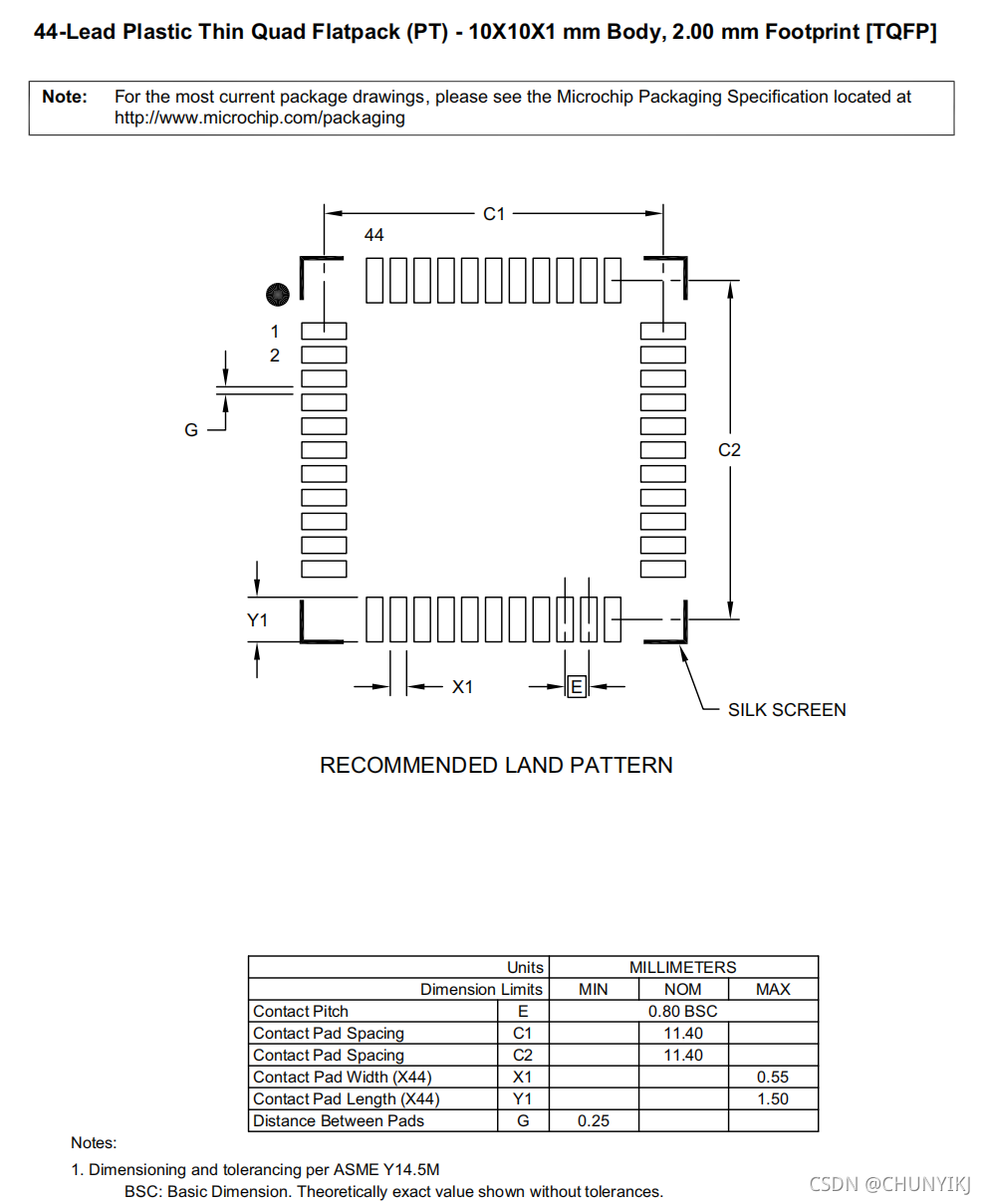

图6:pic16 (l) f1517/1519的44针TQFP封装图

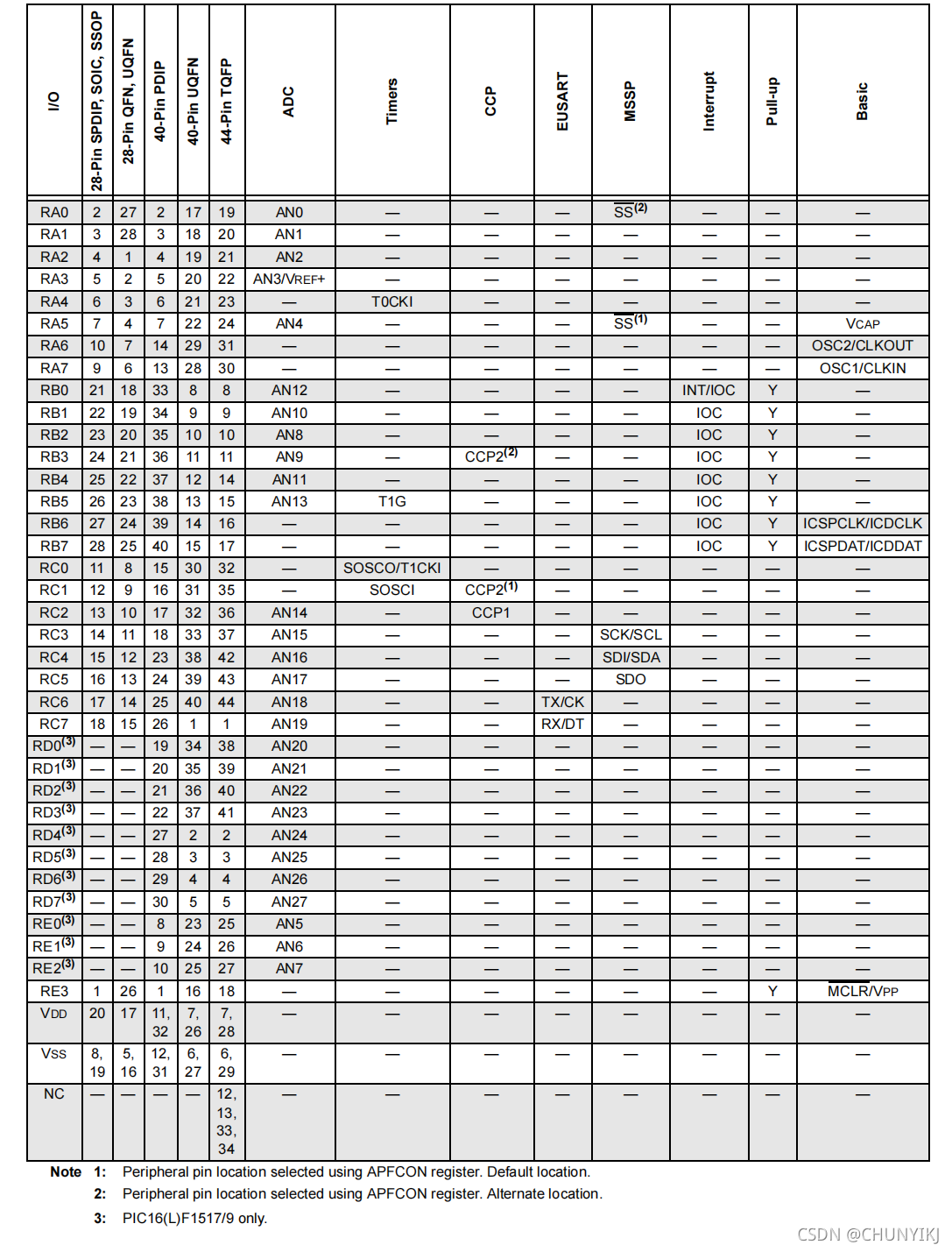

表1:28/40/44针分配表

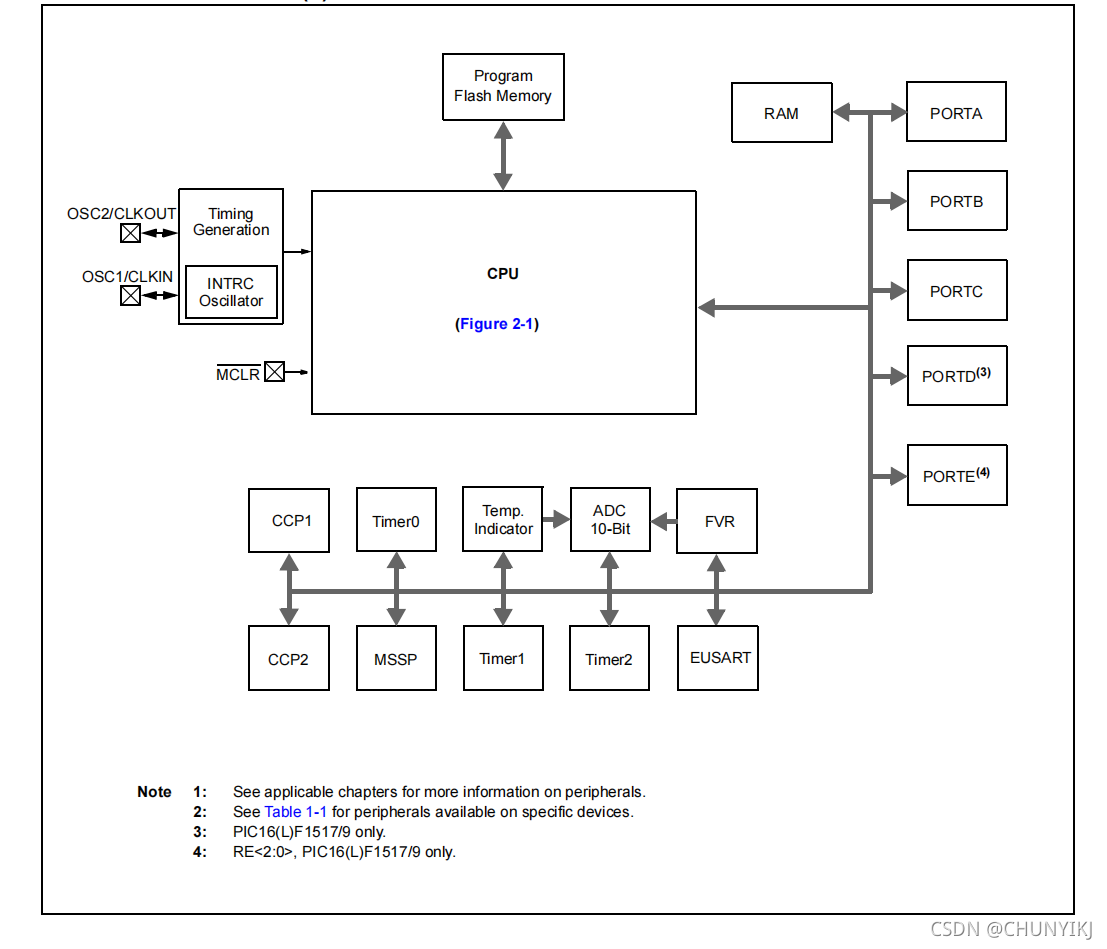

1.0设备概述

在此数据中描述了PIC16(L)F1516/7/8/9

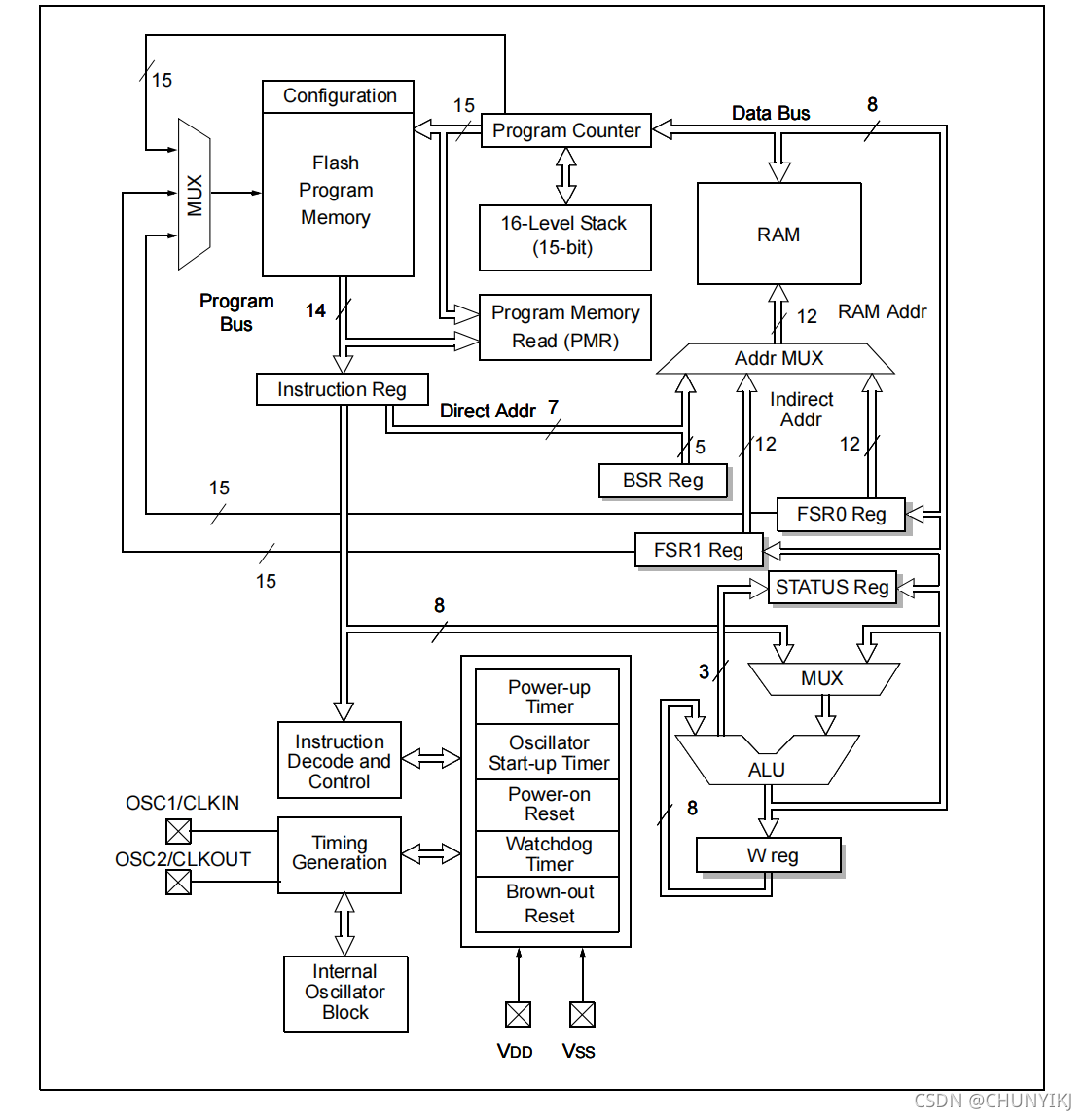

表。系统框图如图1-1所示

PIC16 (L) F1516/7/8/9设备。表1-2

引出线的描述。

参考表1-1提供的外设

设备。

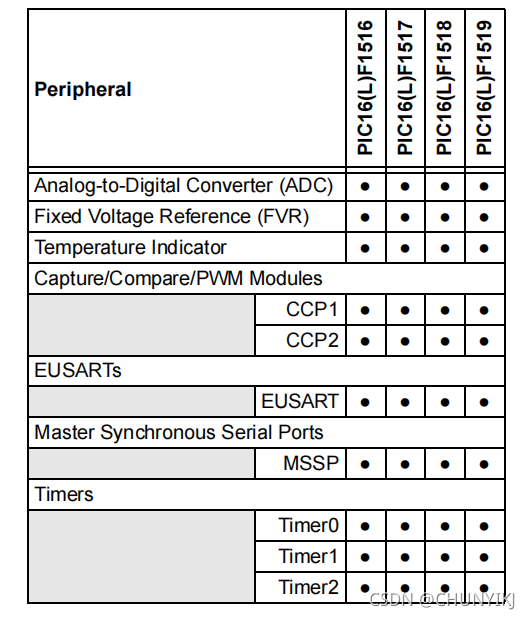

表1-1:设备外设

总结

图1-1:pic16 (l) f1516/7/8/9方框图

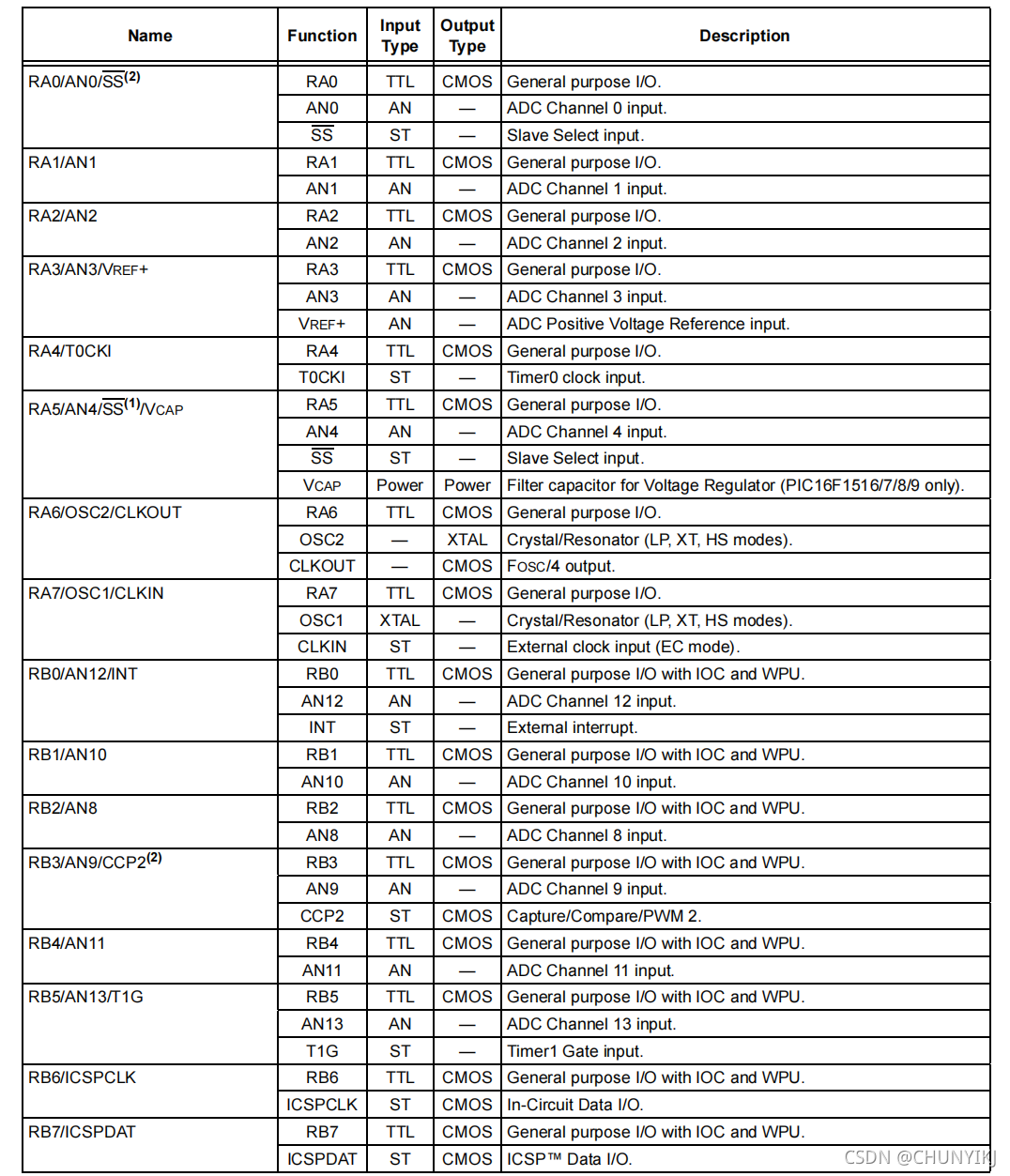

?表1-2:pinout描述

图示:AN =模拟输入或输出CMOS= CMOS兼容输入或输出OD =开路漏极

TTL = TTL兼容输入ST =施密特触发器输入与CMOS电平I2C =施密特触发器输入与I2C

HV =高电压XTAL =晶体级

注1:外围引脚位置选择使用APFCON寄存器(寄存器12-1)。默认的位置。

2:外围引脚位置选择使用APFCON寄存器(寄存器12-1)。备用位置。

3: PORTD和RE<2:0>只在PIC16(L)F1517/9上可用。

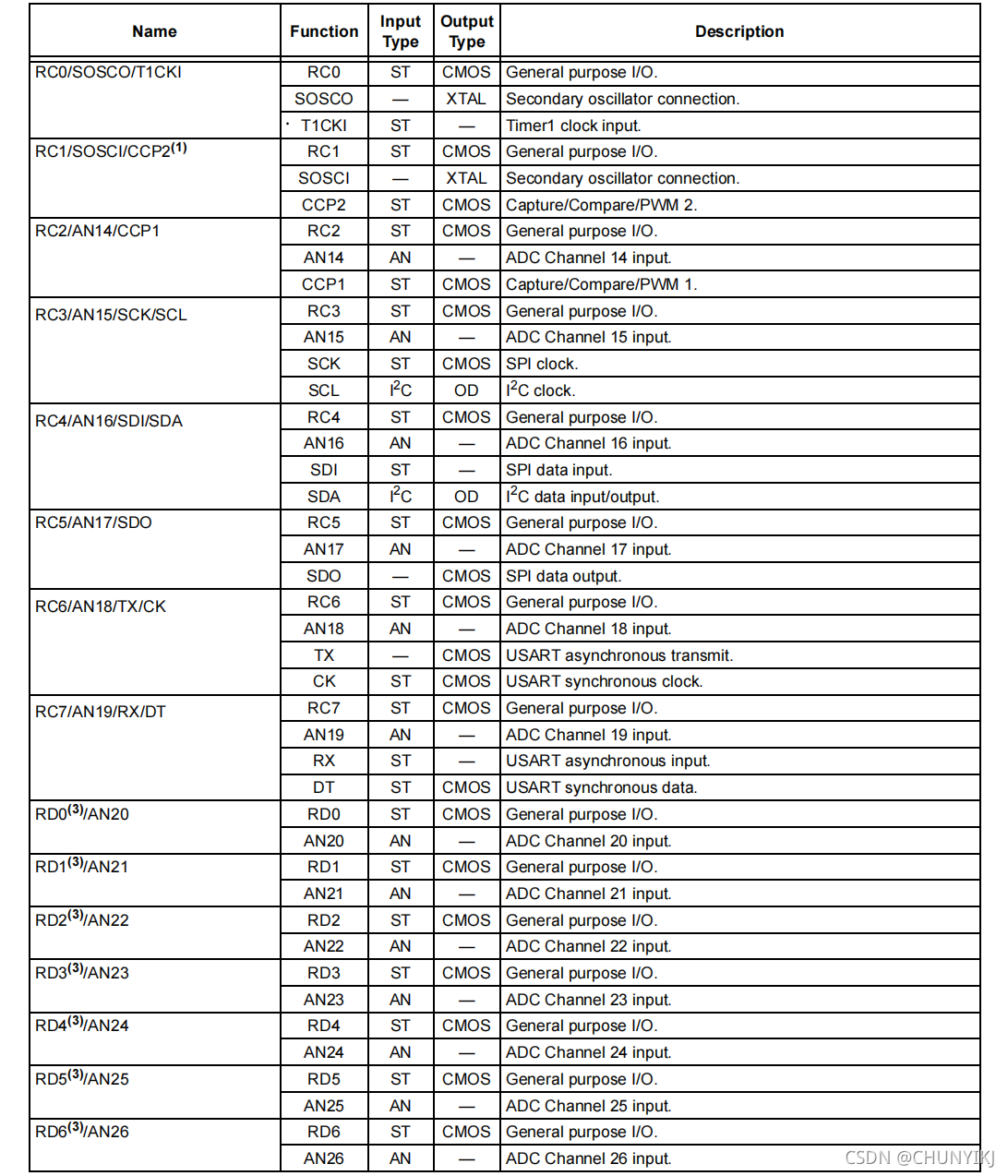

?表1-2:pinout描述(续)

图示:AN =模拟输入或输出CMOS= CMOS兼容输入或输出OD =开路漏极

TTL = TTL兼容输入ST =施密特触发器输入与CMOS电平I2C =施密特触发器输入与I2C

HV =高电压XTAL =晶体级

注1:外围引脚位置选择使用APFCON寄存器(寄存器12-1)。默认的位置。

2:外围引脚位置选择使用APFCON寄存器(寄存器12-1)。备用位置。

3: PORTD和RE<2:0>只在PIC16(L)F1517/9上可用。

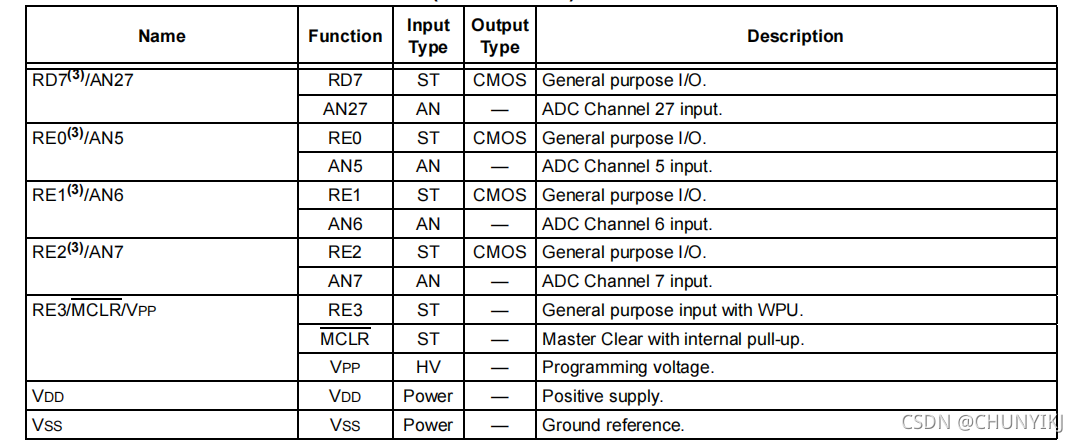

表1-2:pinout描述(续)

图示:AN =模拟输入或输出CMOS= CMOS兼容输入或输出OD =开路漏极

TTL = TTL兼容输入ST =施密特触发器输入与CMOS电平I2C =施密特触发器输入与I2C

HV =高电压XTAL =晶体级

注1:外围引脚位置选择使用APFCON寄存器(寄存器12-1)。默认的位置。

2:外围引脚位置选择使用APFCON寄存器(寄存器12-1)。备用位置。

3: PORTD和RE<2:0>只在PIC16(L)F1517/9上可用。

2.0增强的中端CPU

这个系列的设备包含一个增强的中程

8位CPU核心。CPU有49条指令。中断

功能包括自动上下文保存。的

硬件栈是16层深,并有溢出和

下溢复位功能。直接、间接、和

有相对寻址模式。两个文件

选择寄存器(fsr)提供读取能力

程序和数据存储器。

?自动中断上下文保存

?16级堆叠溢出和下流

?文件选择寄存器

?指令集

图2-1:核心框图

2.1自动中断

储蓄

在中断期间,某些寄存器是自动的

保存在阴影寄存器和恢复时返回

从中断。这节省了堆栈空间和用户

代码。参见第7.5节“自动上下文保存”,

为更多的信息。

2.2 16级堆栈溢出和

下溢

这些设备有一个外部堆栈内存15位

宽,16字深。一个堆栈溢出或流下将设置适当的位(STKOVF或STKUNF)

在PCON寄存器中,如果启用,将导致软件复位。请参阅3.6节“堆栈”了解更多细节。

2.3文件选择寄存器

有两个16位文件选择寄存器(FSR)。市场

可以访问所有的文件寄存器和程序存储器,

它允许一个数据指针用于所有内存。当一个

FSR指向程序存储器,还有一个附加的

在指令周期中使用INDF来允许

待获取的数据。通用记忆现在可以了

也是线性的,提供了能力

访问大于80字节的连续数据。有

还有支持fsr的新指令。看到

更多细节请参阅3.7节“间接寻址”。

2.4指令集

有49条增强中程的说明

CPU,支持CPU的特性。看到

第24.0节“指令集摘要”了解更多信息

细节。

3.0组织记忆

这些设备包含以下类型的内存:

?程序内存

――配置的话

――设备ID

――用户ID

- Flash程序内存

?数据存储器

――核心寄存器

-特殊功能寄存器

-通用内存

――常见的内存

以下特性与访问和关联

程序存储器和数据存储器的控制:

?PCL和PCLATH

?堆栈

?间接寻址

3.1程序内存组织

增强的中程核心有一个15位程序

计数器能够寻址一个32K x 14程序

内存空间。内存大小如表3-1所示

为这些设备实现。访问一个位置

超过这些界限将导致一个环绕内部

实现的内存空间。重置向量是

而中断向量在0004h(见

图3-1和图3-2)。

Flash 3.2高耐用性

这个设备有一个128字节的高耐久段

程序闪存(PFM)代替数据

eepm。这个地区特别适合

预期的非易失性数据存储

在最终产品的生命周期内经常更新。

参见第11.2节“Flash程序内存”

的详细信息

烤瓷。参见第3.2.1.2节“用FSR间接读取”

,以获取有关使用FSR寄存器的更多信息

读取存储在PFM中的字节数据。

?

?

?

?

3.2.1读取程序内存为

数据

中有两种访问常量的方法

程序内存。第一种方法是使用表

RETLW指令。第二种方法是设置

指向程序内存的FSR。

3.2.1.1 RETLW指令

可以使用RETLW指令来提供访问

到常数表。例3-1所示为推荐的cre吃这样一个表的方法。

?

?

简单的实现。如果代码必须保持可移植性

与前几代的微控制器相比,然后

BRW指令不可用,所以旧的表读取

方法必须使用。

3.2.1.2 FSR间接读

程序内存可以作为数据访问

设置FSRxH寄存器的第7位并读取

匹配INDFx登记。MOVIW指令会

将寻址词的下八位放在

W登记。写入程序内存是不可能的

通过INDF寄存器执行。指令

通过FSR访问程序内存需要一个

额外的指令周期要完成。例3 - 2

演示通过控件访问程序内存

身上。

HIGH指令将设置位<7>,如果标签指向a

程序存储器中的位置

数据内存被划分为32个内存组

银行里有128个字节。每行由

(图3 - 3):

?12核寄存器

?20个特殊函数寄存器(SFR)

?高达80字节的通用RAM (GPR)

?16字节的普通RAM

通过写银行号码来选择活动银行

进入银行选择登记(BSR)。未实现的

内存将读取为' 0 '。所有数据均可存储

直接访问(通过使用

文件注册)或间接通过两个文件选择

寄存器(FSR)。见第3.7节“间接”

地址是“获取更多信息”。

数据存储器使用12位地址。上五位

的地址定义了银行地址,较低的

7位选择单个SFR, GPR和普通

银行的内存位置。

核心寄存器直接包含这些寄存器

影响基本操作。核心寄存器占用

每个数据存储库的前12个地址

(地址:x00h/x08h至x0Bh/x8Bh)。这些

表3-2列出了寄存器。的详细

信息,如表3-7所示。

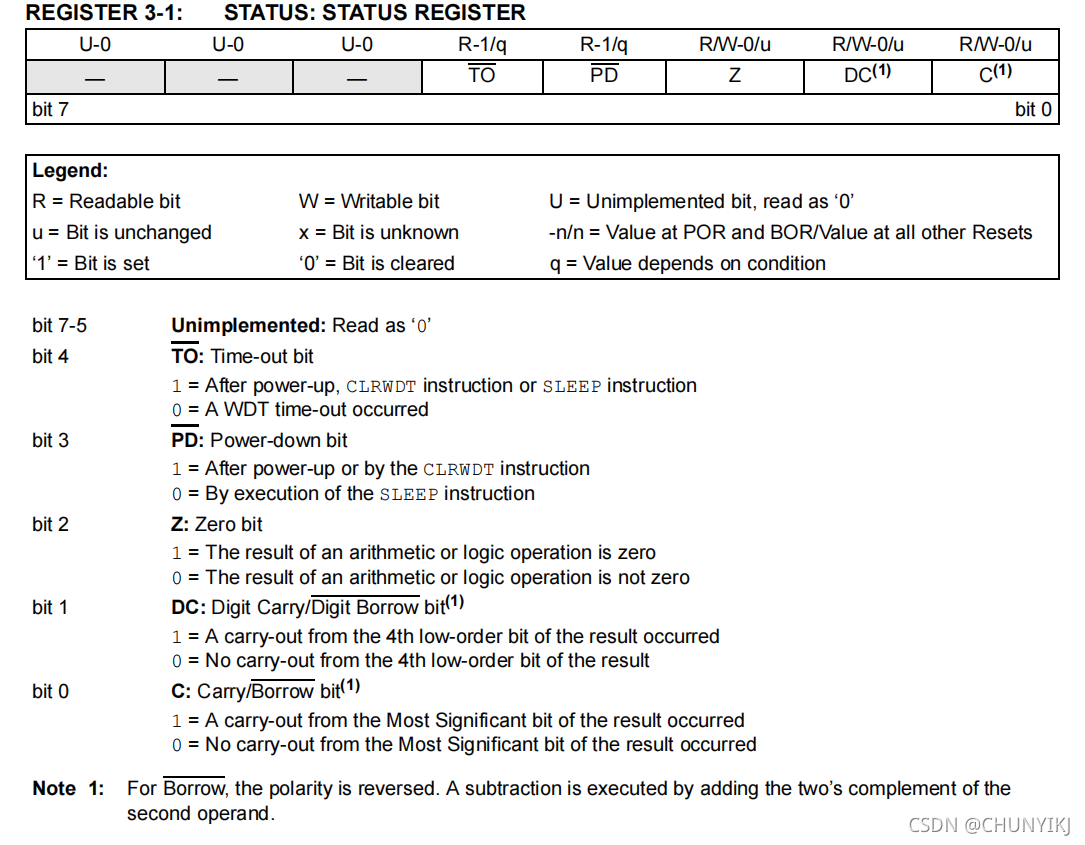

STATUS寄存器,如寄存器3-1所示,包含:

?ALU的算术状态

?Reset状态

STATUS寄存器可以是任何

指令,就像其他寄存器一样。如果状态

寄存器是受影响指令的目的地

Z, DC或C位,然后写入这三个位是

禁用。这些位是根据

设备的逻辑。此外,TO和PD位不是

可写的。因此,使用的指令的结果

作为目的地的状态寄存器可能不同于

的意图。

例如,CLRF STATUS将清除上面三个

位,并设置Z位。这就剩下STATUS寄存器了

如' 000u u1uu '(其中u = unchanged)。

因此,建议只使用BCF、BSF、

SWAPF和MOVWF指令用于修改

状态寄存器,因为这些指令没有

影响任何状态位。对于其他指示,请不要

影响任何状态位(参见24.0节)

“指令集总结”)。

3.4注册定义:状态

注1:C位和DC位操作为Borrow

和Digit Borrow out bits,分别为in

减法。

3.4.1专用函数寄存器

特殊函数寄存器是由

控制所需操作的应用程序

设备中的外围功能。特殊的功能

的核心寄存器之后占用20个字节

每个数据存储器(地址为x0Ch/x8Ch

通过x1Fh / x9Fh)。关联的寄存器

外围设备的操作在

适当的外围章节的这一数据表。

3.4.2通用滑块

在每个数据存储器中有多达80字节的GPR

银行。特殊功能寄存器占20个

每个数据存储器的核心寄存器后面的字节

银行(地址:x0Ch/x8Ch至x1Fh/x9Fh)。

3.4.2.1 GPR线性访问

一般用途的RAM可以在

非银行方法,通过fsr。这可以简化

访问大内存结构。参见3.7.2章

“线性数据存储器”获取更多信息。

3.4.3常见的内存

有16个字节的公共RAM可从所有

银行。

?

?

3.4.4设备内存映射

内存映射为PIC16(L)F1516/7和

PIC16(L)F1518/9如表3-3和

表3 - 4,分别。

?

?

?

?

?

?

?

?

?

?

?记下

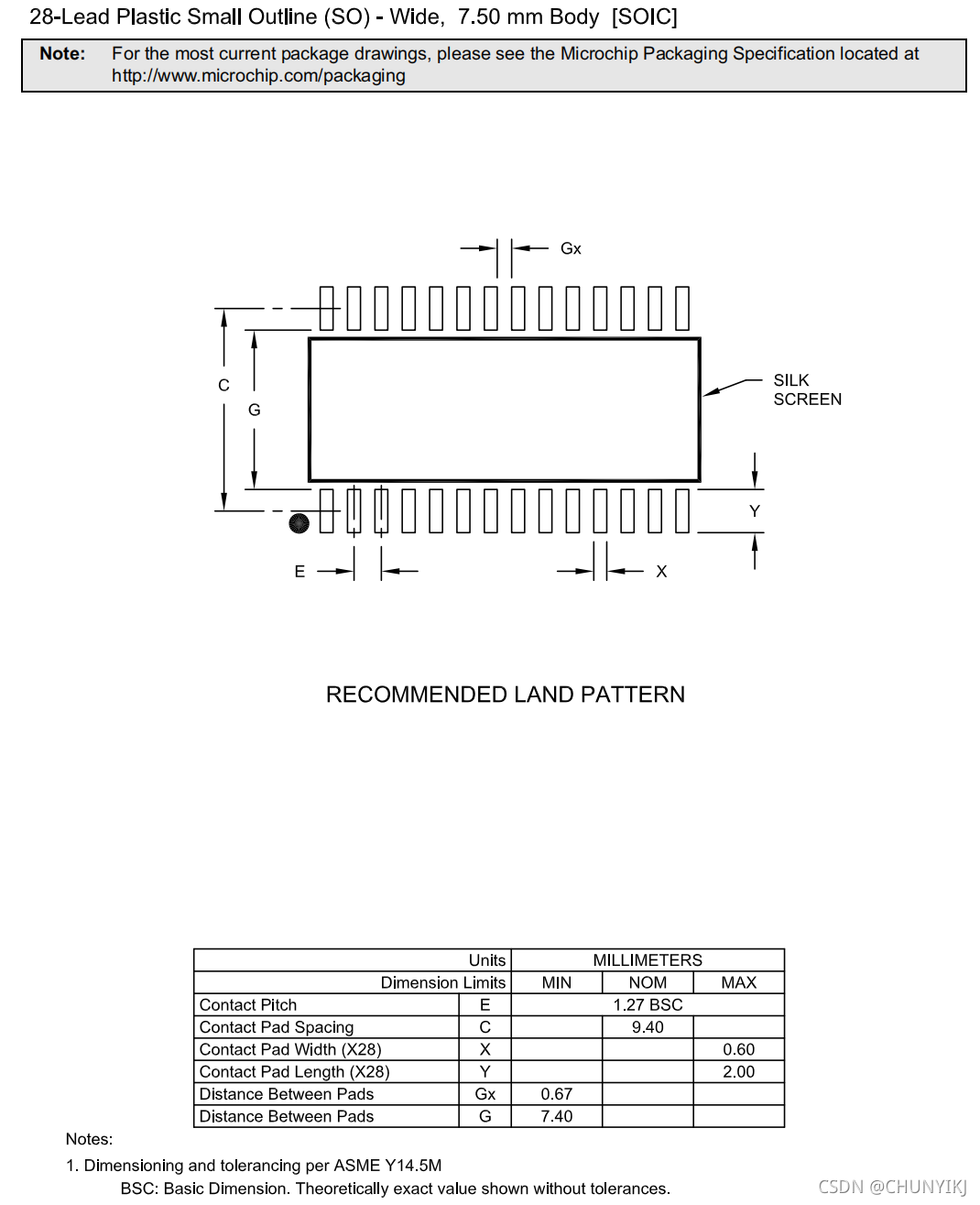

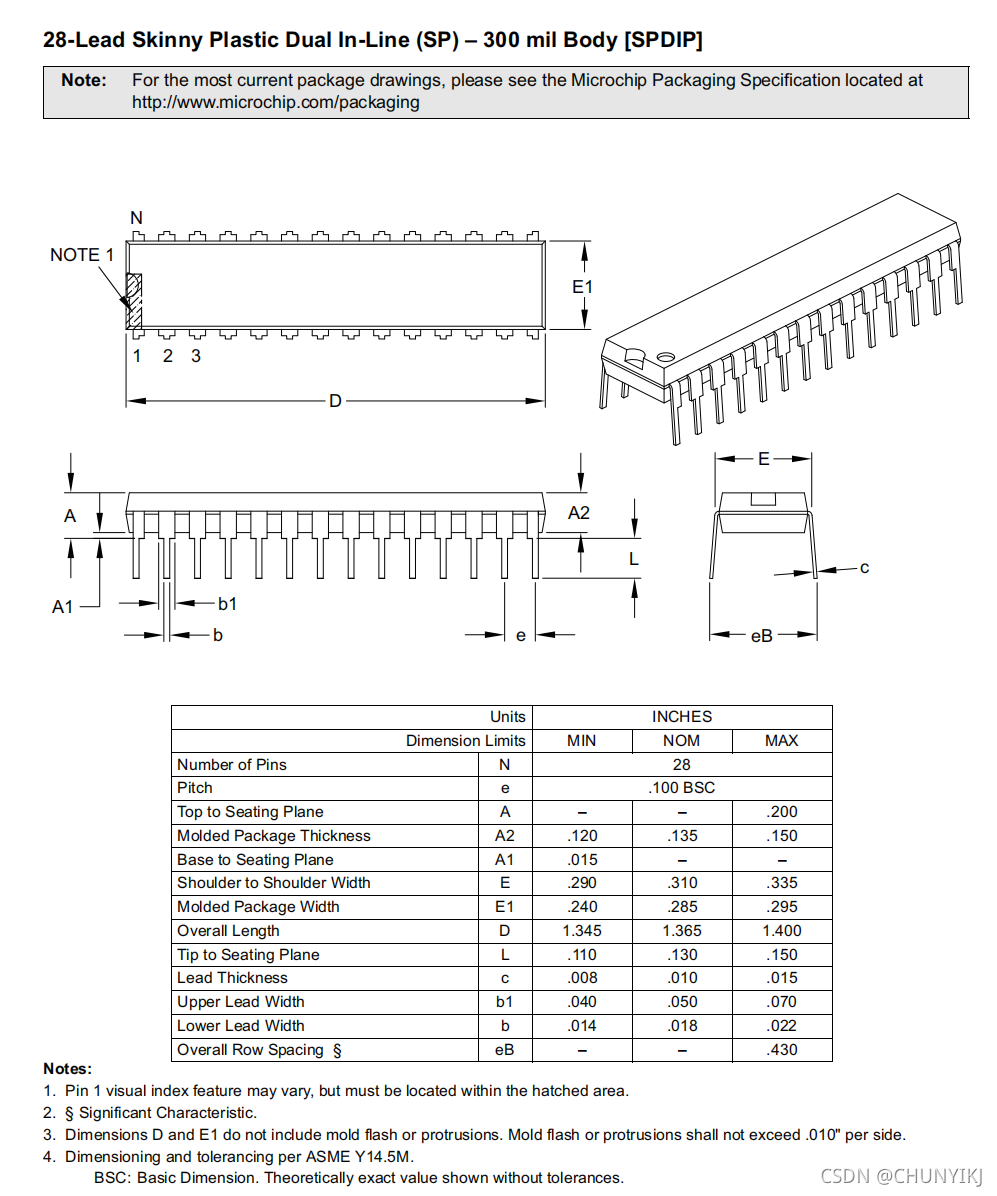

1.Pin1的视觉索引特征可能会有所不同,但必须位于孵化区域内。 2.§的显著性特征

3.尺寸D不包括模具闪光灯、突出物或门式毛刺,其中应

每端不超过0.15毫米。尺寸E1不包括铅间闪光或突出物,每边不得超过0.25mm。 4.按每台ASMEY14.5M计算的尺寸和公差

BSC;基本尺寸。理论上精确的值显示,没有公差。

参考文献:参考尺寸,通常没有公差,仅供参考使用。 5.基准A和B将在基准H中确定。

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?

?在具体调试过程中,我们会遇到各种奇怪的显示异常,需要具体情况具体分析。本人调试PIC16F1519-I/PT也有9年多了,基本上没有解决不了的问题。如有疑问,欢迎大家加Q?1547237878 ? Tel 18620382326?

?

?

?