DDR3Ӧ���ܽ�(��)

4.ʹ��MIG IP�˹���DDR3Ӧ��

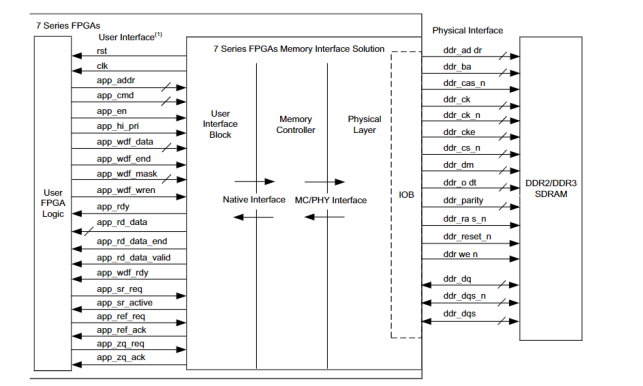

��ͼȡ��Xilinx�ٷ��ֲ�ug586,figure1-51,MIG IP����һ����ģ��,�൱��������������DDRоƬ,���ڸ��û���װ�˽ӿ�,�����û�ʹ�á���ͼ�п��Կ���,���û����������ͨ�����������������ϵĻ���,�ɴ�Ҳ�������û����һϵ�����⡣�������MIG IP�˵Ľӿں�ʱ���Լ�MIG IP�����ý���˵����

4.1MIG IP�ӿ��ź�

?init_calib_complete:output�ź�,�忨�ϵ��,DDR3 IP�˻��DDR��ʼ��У��,���֮��IP�����ߴ��ź�,����û�ֻ�м����ź�Ϊ�ߵ�ƽ����ܶ�DDR���ж�д����(PHY asserts init_calib_complete when calibration is finished)

?app_addr:input�ź�,��DDRʵ�ʵ����ź�,���ź�,bank�ź�ת��Ϊ����ַ�ź�,����ź�Ӧ�õ���30bit=1bit rank+3bit bank+16bit row address + 10bit row address(��MT41K512M16HA-125AITΪ��),30bit�е����λrankΪ������λ,��û���õ���

?app_cmd:input�ź�,3bit��IP�˲���������,000Ϊд����,001Ϊ������

?app_en:input�ź�,IP�˵�����ʹ������:This is the active-High strobe for the app_addr[], app_cmd[2:0] inputs

?app_rdy:output�ź�,IP�������,����ready�ź�:This output indicates that the UI is ready to accept commands. If the signal is deasserted when app_en is enabled, the current app_cmd and app_addr must be retried until app_rdy is asserted

?app_rd_data:output�ź�,��ǰ��ȡ��������,��app_rd_data_validͬ����

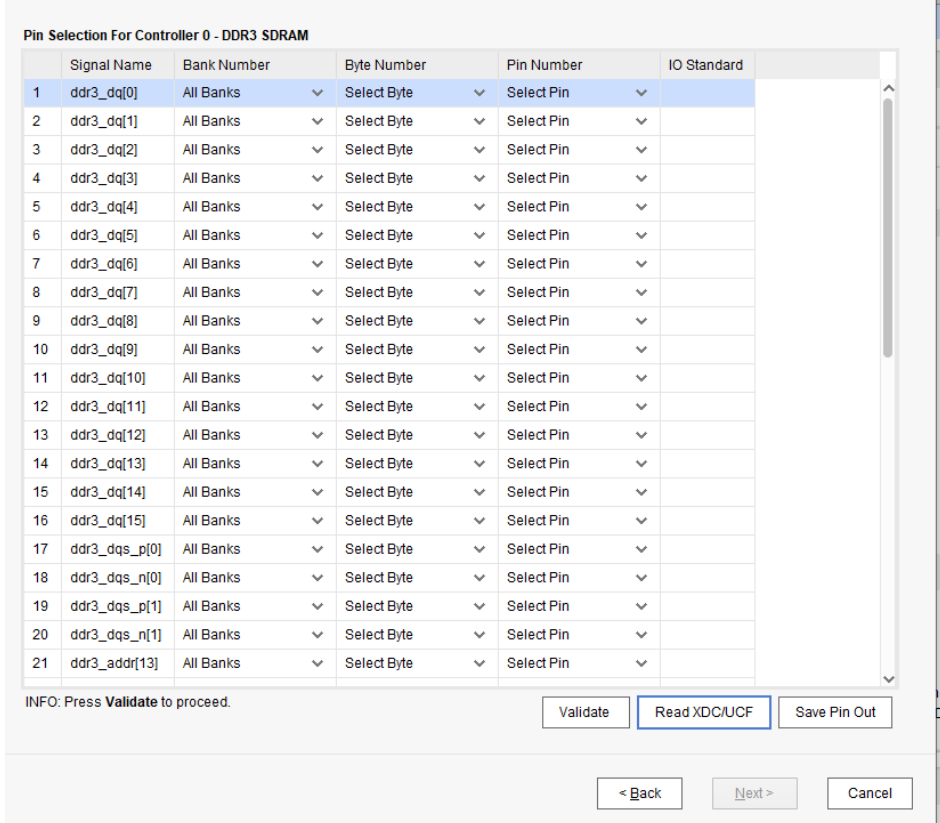

?app_rd_data_end:output�ź�,�˸ߵ�ƽ��Ч���ָʾ��ǰʱ��������app_rd_data []��������ݵ����һ�����ڡ� ����app_rd_data_validΪactive-Highʱ��Ч��(����ź����û�����û��)This active-High output indicates that the current clock cycle is the last cycle of output data on app_rd_data[]. This is valid only when app_rd_data_valid is active-High��ʵ��Ӧ�ù�����,ͨ����������źš�

?app_rd_data_valid:output�ź�,�ߵ�ƽ��ʾ��ǰ�� app_rd_data ������Ч��This active-High output indicates that app_rd_data[] is valid.

?app_wdf_data:input�ź�,��ǰ��Ҫд�������,This provides the data for write commands.

?app_wdf_end:input�ź�,�˸ߵ�ƽ��Ч����ָʾ��ǰʱ�������� app_wdf_data ���������ݵ����һ�����ڡ�This active-High input indicates that the current clock cycle is the last cycle of input data on app_wdf_data[]��Ӧ����ͨ����app_wdf_wrenͬ��,����:

assign app_wdf_end = app_wdf_wren;

?app_wdf_mask[APP_MASK_WIDTH �C 1:0]:input�ź�,��ǰ�������ݵ�����,maskΪ1��λ��Ӧ�����ݽ������ε���This provides the mask for app_wdf_data[]��

?app_wdf_rdy:output�ź�,���������д����FIFO�����ý������ݡ� ��app_wdf_rdy = 1��b1��app_wdf_wren = 1��b1ʱ,����д�����ݡ�This output indicates that the write data FIFO is ready to receive data. Write data is accepted when app_wdf_rdy = 1��b1 and app_wdf_wren = 1��b1.

?app_wdf_wren:input�ź�,�ߵ�ƽ��ʾ app_wdf_data ������Ч�� This is the active-High strobe for app_wdf_data[].

?ui_clk:output�ź�,MIG������û���ʱ��(ע����2.3�ڵĺ���ʱ���빤��ʱ������),��4:1(�������������IP��������)ģʽ����DDR��Ƶ��1/4�����ʱ������MIG���ɵ�,��ͬƵ������ʱ��ҲҪ��ʱ����ĸ��롣

?ui_clk_sync_rst:output�ź�,MIG������û��˸�λ�ź�,�ߵ�ƽ��λ��

?sys_clk_i:����MIG��ʱ��(ע������,�˴�������IP������)��

?clk_ref_i:����MIG�IJο�ʱ��,ֵ�̶�Ϊ200MHz��

?sys_rst:����MIG�ĸ�λ�ź�,�͵�ƽ��Ч��

4.2MIG IP�ӿ�ʱ��

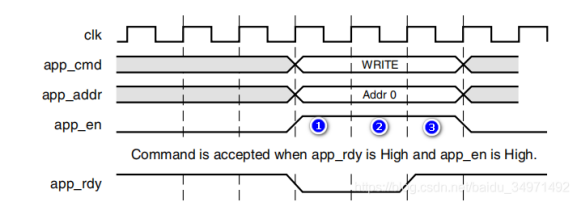

?�addr��cmd:

����ͼ��ʾ��,��,�����,ֻ���ڢ�ʱ��app_en��app_rdyͬʱΪ�ߵ�ƽapp_cmd(����)��(app_addr)��ַ����Ч,���Ե���Ҫapp_cmd,app_addr��Чʱapp_en���뱣�ֵ�app_rdyΪ�ߵ�ƽ����Ч��

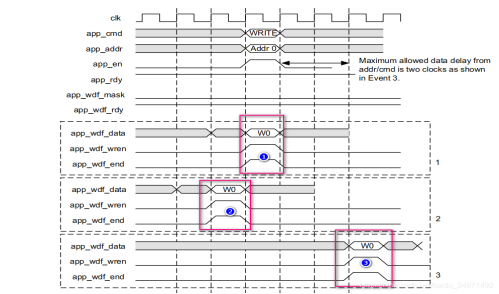

?дʱ��:

����ͼ��ʾ��,��,�������,д�����д����ֱ�Ӵ�����������ϵ��

�ٱ�ʾд����(app_cmd),д��ǰ��ַ(app_addr)��д����(app_wdf_data)�Լ�д�����ź�(app_en,app_rdy,app_wdf_rdy,app_wdf_wren,app_wdf_end)ͬʱ��Ч���Ƽ���������ʱ��

�ڱ�ʾд����(app_wdf_data)��д�����ź�(app_wdf_wren,app_wdf_end)����д����(app_cmd)��д��ǰ��ַ(app_addr)�Լ�����д�����ź�(app_en,app_rdy,app_wdf_rdy)һ���û�ʱ��(ui_clk)��

�۱�ʾд����(app_wdf_data)��д�����ź�(app_wdf_wren,app_wdf_end)����д����(app_cmd)��д��ǰ��ַ(app_addr)�Լ�����д�����ź�(app_en,app_rdy,app_wdf_rdy)����������û�ʱ��(ui_clk)��

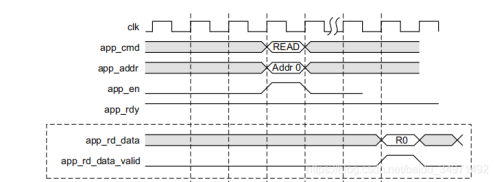

?��ʱ��:

����ͼ��ʾ,��������(app_cmd)�͵�ǰ����ַ(app_addr)�Լ��������ź�(app_en,app_rdy)ͬʱ��Чʱ,�ȴ���������Ч�ź�(app_rd_data_valid)��Чʱ������(app_rd_data)��Ч��

4.3MIG IP����

1.�� IP Catalog ������ Memory Interface Generator,˫����������ҳ��,��� Next ,���� MIG Output Options ��

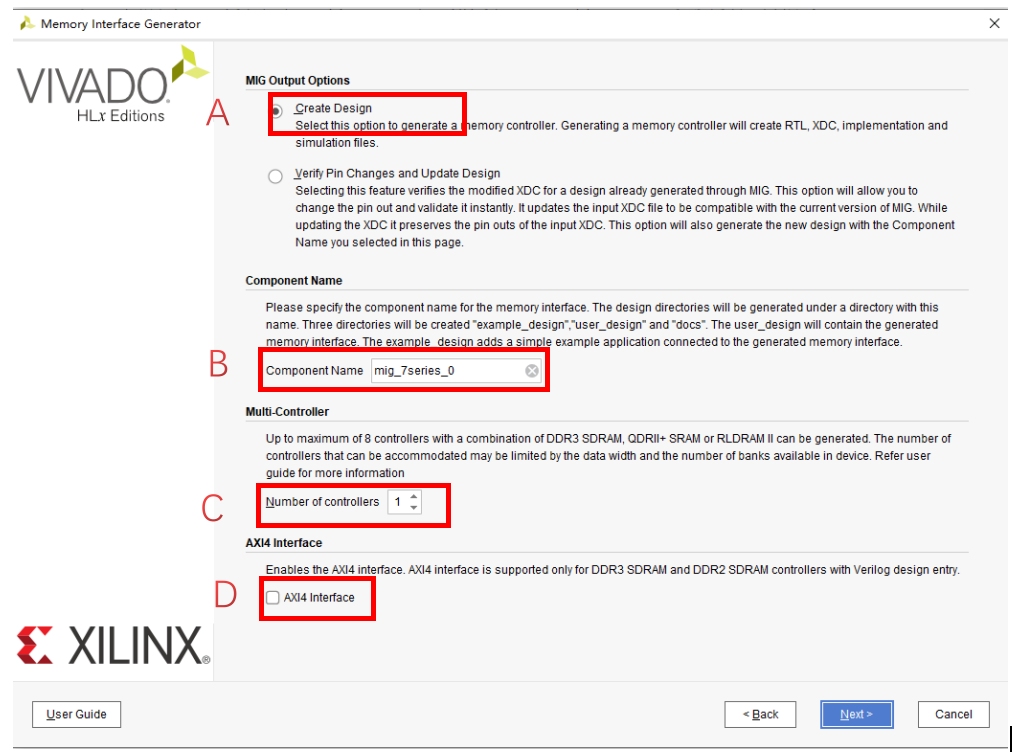

2.ѡ��A��������Դ����µ��ڴ���������;��B��Component Name field��һ��������IP���������;��Cѡ��Ҫ���ɵĿ���������;D��,DDR2��DDR3 SDRAM���֧���ڴ�ӳ���AXI4�ӿڡ� AXI4�ӿڽ�֧��Verilog���ԡ� �����ҪAXI4�ӿ�,���ڵ���MIG����֮ǰ��Vivado Design Suite�н�����ѡ��Ϊ�� Verilog���� ���δѡ��AXI4����,���û�����(UI)����Ҫ���档

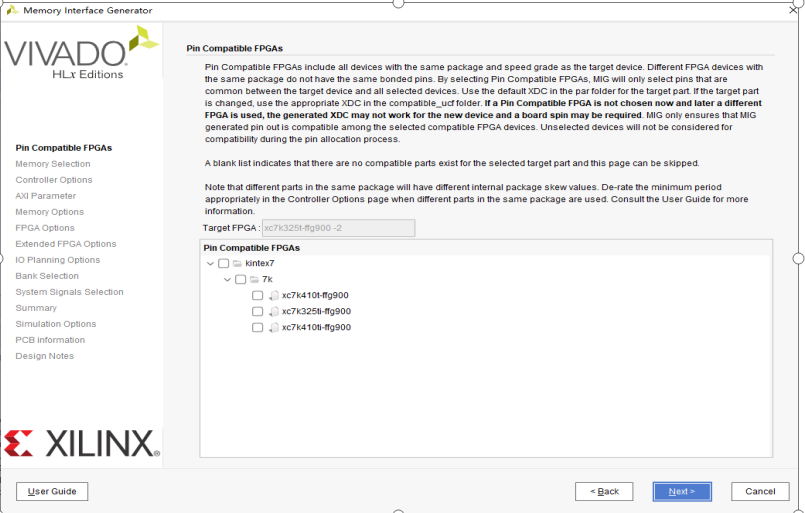

3.���ż��ݵ�FPGAҳ���г�����ѡϵ���о�����ͬ��װ��FPGA�� �����MIG�������ɵ�������Ҫ�������κ�FPGA����,��Ӧʹ�ô�ѡ����ѡ����������ż��ݵ�FPGA��

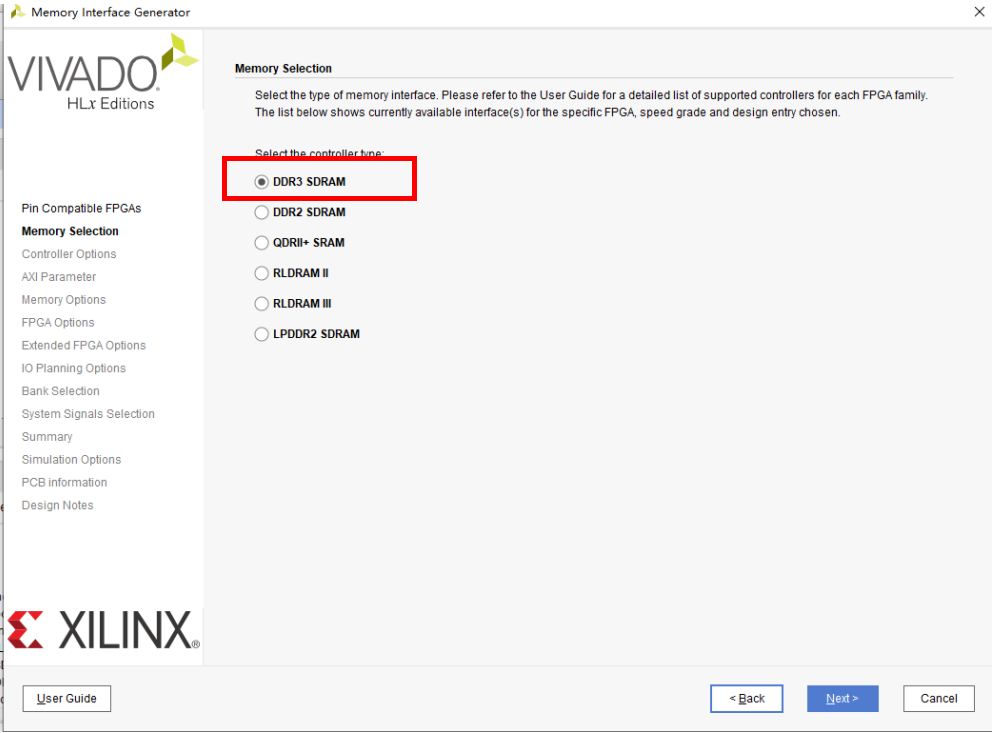

4.��ҳ����ʾ��ѡFPGAϵ��֧�ֵ����д洢�����͡�ѡ��DDR3 SDRAM����������,������һ������ʾ��������ѡ�ҳ�档

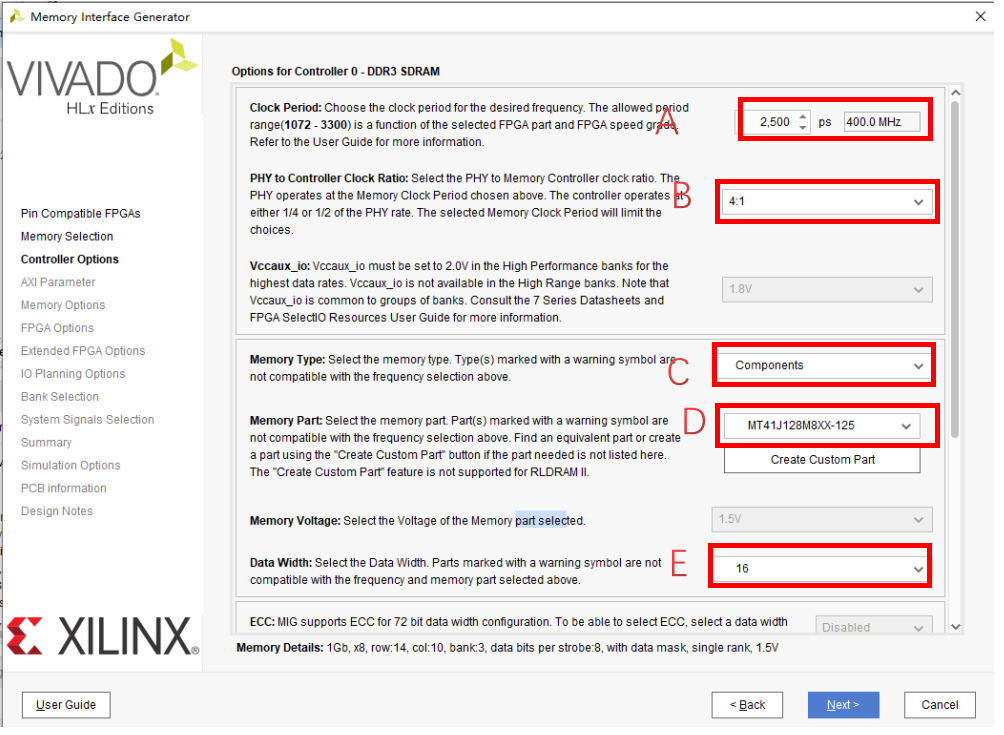

5.��ҳ����ʾ�˿���ѡ��ĸ��ֿ�����ѡ�

A.ʱ������,Ƶ�ʷ�Χ����ѡFPGA�������ٶȵȼ������ص����ơ���������Ϊ400MHz�����DDR3�������ŵĹ���Ƶ��,��IO�������Ĺ���Ƶ��,��������Ϊ400MHz��

B.PHY�������ʱ�ӱ��ʨC�˹���ȷ��������(�洢��)ʱ��Ƶ�����û�����ʱ��Ƶ�ʵı���,����ѡ��4:1,����Ƶ��Ϊ400MHz,��ô�û�ʱ��ui_clkΪ100MHz������FPGA��ʱ�������,2:1�ı��ʽ��������洢���ӿ�Ƶ�ʡ�2:1�������û������������߿����������ڴ�ӿڿ��ȵ��ı�,��4:1���������߿����������ڴ�ӿڿ��ȵİ˱�(�����ù���Ƶ��Ϊ400MHz,��ΪDDR,���Ե�Ч��ÿһ��800MHz������Ҫ16bit����,�˴�����Ϊ2:1,���û�ʱ��ui_clkΪ200MHz,��ôһ��200M������ʱ���ϵ���4��800M����,�ɴ�һ���û�ʱ������Ӧ�ṩ4����16bit���ݲ�������ƥ��,ͬ��,����Ϊ4:1ʱ,��ô�û�����Ӧ����8����16bit)��2:1�ı������нϵ͵��ӳ١�4:1�ı��ʶ��ڻ��������������DZ�Ҫ�ġ�ͨ������4:1��

C.�˹���ѡ�������ʹ�õ��ڴ沿�ֵ����͡�ʹ��Ĭ��

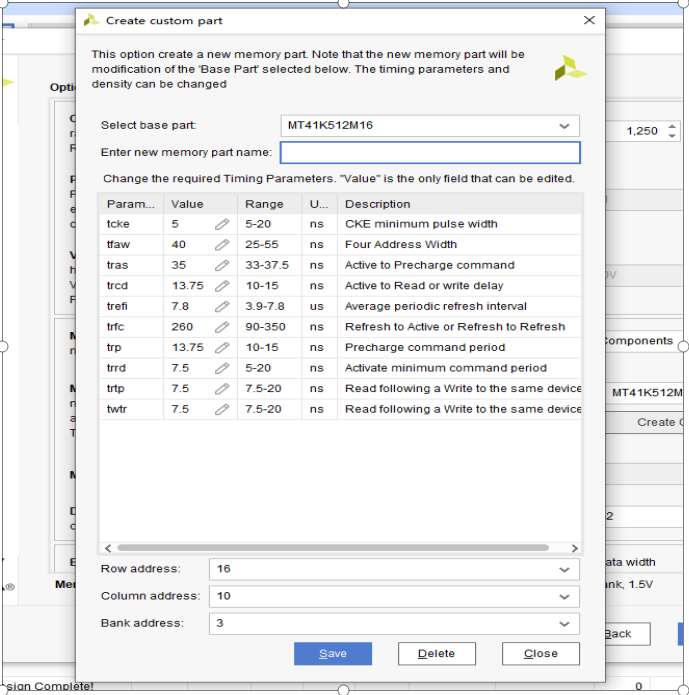

D.ѡ�����������ͺ����ݿ��ȨC���Ը���֮ǰѡ��Ĵ洢�����ڴ˴�ѡ�����ݿ���ֵ�� ���б���ʾ����ѡpart������֧�ֵ����ݿ��ȡ�����б��в�û���Լ���оƬ����,����ѡ�����Ƶ�(ָ������λ��һ��),Ҳ���Ե�������creat custom port�����Զ�����ͺš�ע��,Ӧ��select base part��ѡ����ʵ��оƬλ����Сһ�������е��ͺ���Ϊ����,������ʱ�����(DDR datasheet���ṩ)�Լ�ʵ�ʵ������߿�,�Լ�bankλ��,�����Զ�����ͺš�

E.���ݿ��ȨC���Ը���֮ǰѡ��Ĵ洢�����ڴ˴�ѡ�����ݿ���ֵ�� ���б���ʾ����ѡpart������֧�ֵ����ݿ��ȡ����ֻ��һ��DDR3,��˴���ֵӦ���ڿ���������λ�������ɵ���,���������DDR3,�������?������������𰸡�

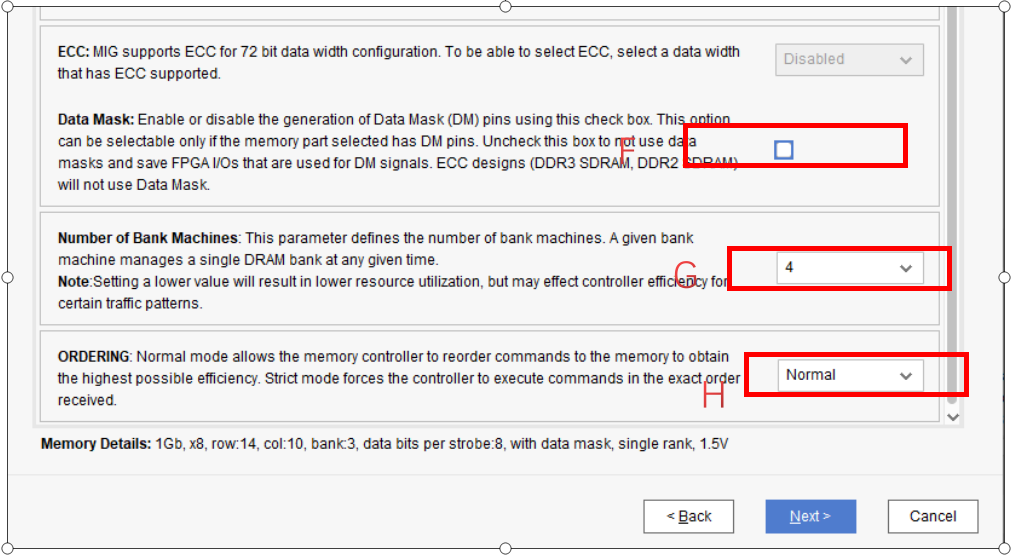

F.Data mask ����Ҫ������

G.Bank Machines�����C�б���ʾ��ѡ�������֧�ֵ�Bank Machines������һ������Ϊ4��

H.����C����ģʽ�����ڴ���������������������ڴ�,�Ի����ߵ�Ч�ʡ� �ϸ�ģʽǿ�ƿ������Խ��յ���ȷ��˳��ִ�����һ������ΪNormal��

�����Զ����DDR3�ͺ�,Ӧ��עMemory Details,�Ƿ���DDR3ʵ�����һ��,����һ����Ӧ��һ�¼���ʹ�á��˴���������һƬDDR3�������

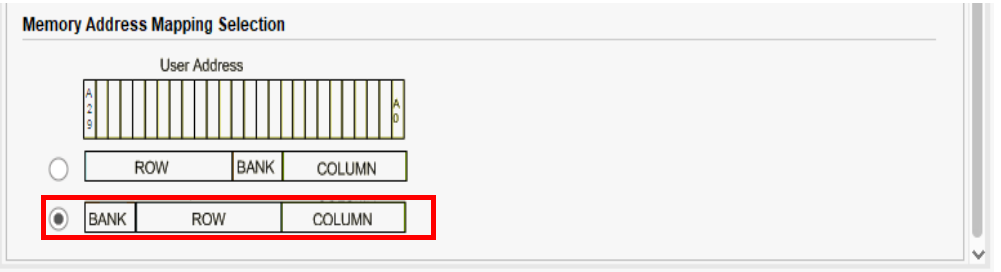

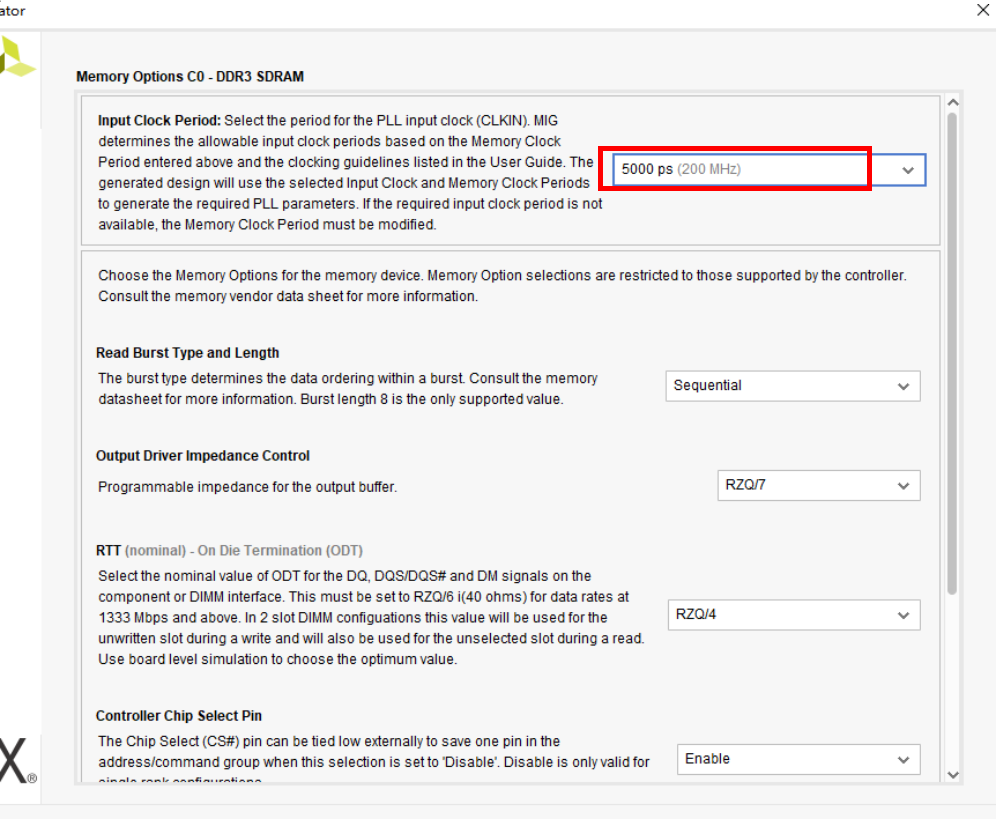

6.����һ����������IP��ʱ��Ϊ200MHz֮��(�˴����õ���sys_clk_i),���ౣ��Ĭ�ϡ��ù�������ѡ������йش洢ģʽ�ļĴ���ֵ���ڳ�ʼ���ڼ�,��ģʽ�Ĵ�����ֵ���ص�����ģʽ�Ĵ����С��ڴ��ַӳ���ѡ��ѡ���ɫ�������ݡ�

7.����������ѡ����������,���ౣ��Ĭ�ϡ�

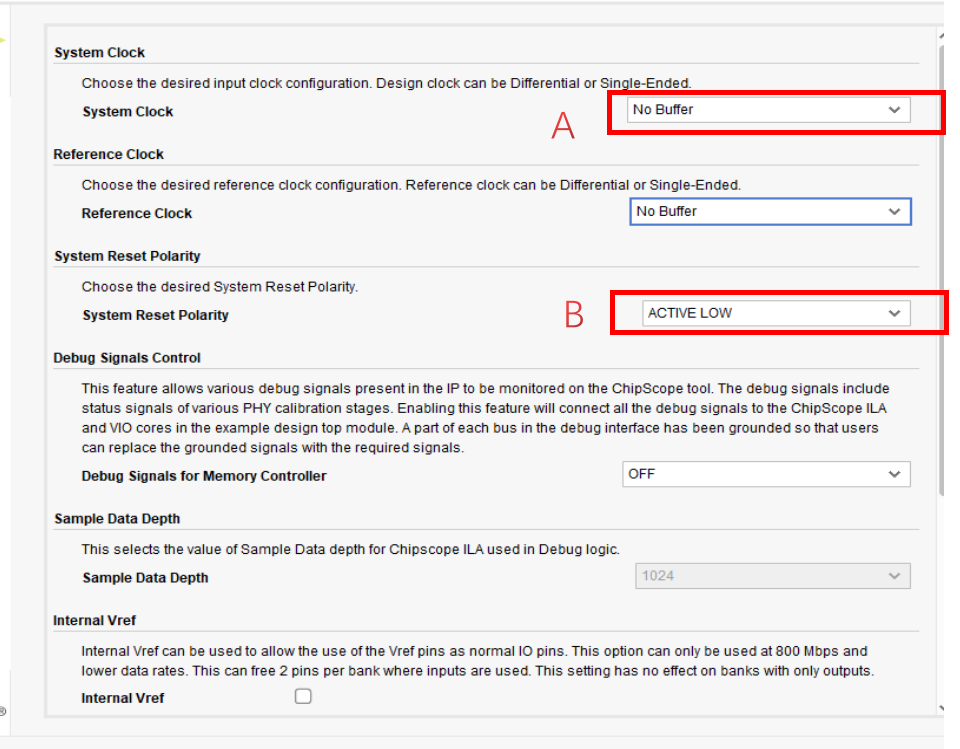

Aϵͳʱ�ӨC��ѡ��Ϊsys_clk�źŶ�ѡ��ʱ������(����,��ֻ�������)�� ѡ����������ѡ��ʱ,������RTL������ʵ����IBUFԭ��,���Ҳ���Ϊϵͳʱ�ӷ������š������û��ִ�и��ĵ������ʵ���˴�MIGΪNo Bufferѡ�����ɵ����,����ƿ��ܻ�����δ���sys_clk_i�ź�ʵ������IBUF����ʵ�֡� ���,��������������,��Ҫ��sys_clk_i�ź����ӵ��ڲ�ʱ�ӡ�

Bϵͳ��λ��ƽ�C����ѡ��ϵͳ��λ�ĵ�ƽ(sys_rst)�� �����ѡ��ѡ��Ϊactive-Low,�����RST_ACT_LOW����Ϊ1;�������Ϊactive-High,�����RST_ACT_LOW����Ϊ0��

����I/O���ĨC��ѡ��ͨ���ڿ��������ڿ���״̬ʱ�Զ�����DQ��DQS IBUF������ƽ��I/O���ġ�

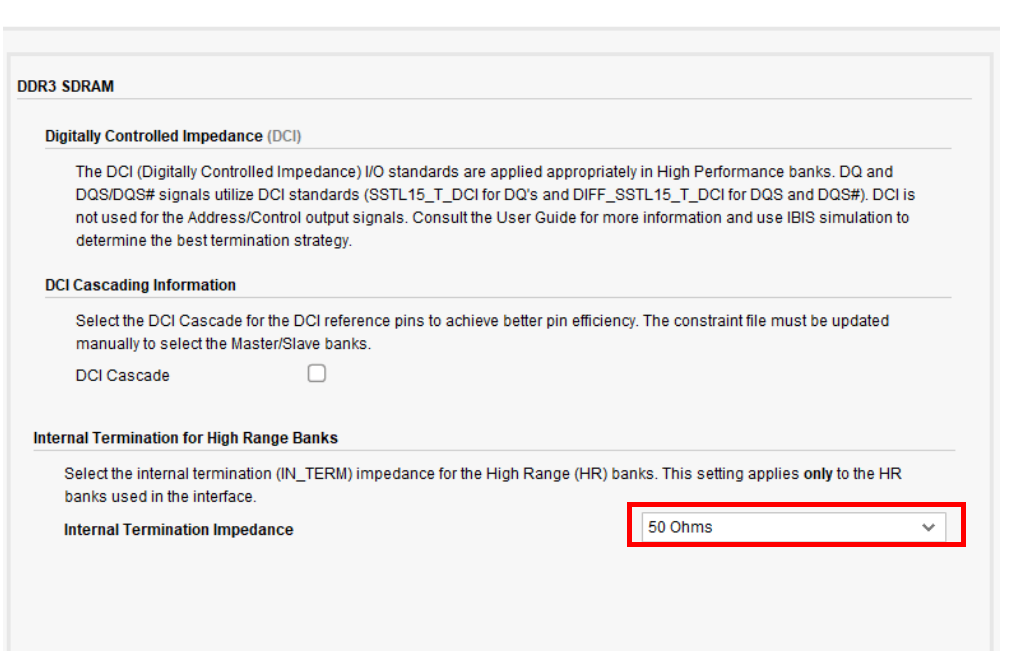

8.HR Bank���ڲ��ն�ƥ�����C�ڲ��ն�ѡ���������Ϊ40��50��60������á� ��ѡ���������HR Bank��ͨ������Ϊ50���ɡ�

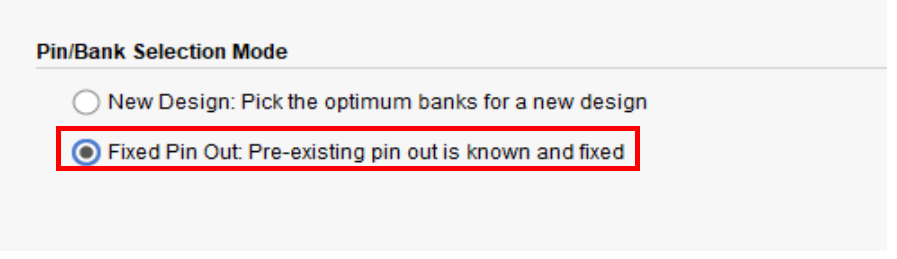

9.����ģʽѡ��ڶ���,֮����UCF�ļ�,��������Լ�����á�

10.��ʼһ����������DDR3�źŶ�Ӧ�Ĺܽ�,�������д���˹ܽ�Լ���ļ�,Ҳ����ֱ�����롣��д��ɺ�,�����Validate�����,��д���Ƿ�����

����ĵ�next���ɡ�

ע:MIG����һ��200MHz��ʱ��sys_clk_i,������һ��200MHz�IJο�ʱ��clk_ref_i����Ƶ����DDR3�Ĺ���ʱ��400MHz(����ʱ��,IO����ʱ��),��Ƶ����һ��100MHz���û�ʱ��ui_clk����֮ǰ��Ĺ���ʱ��,����ʱ��,����ط������

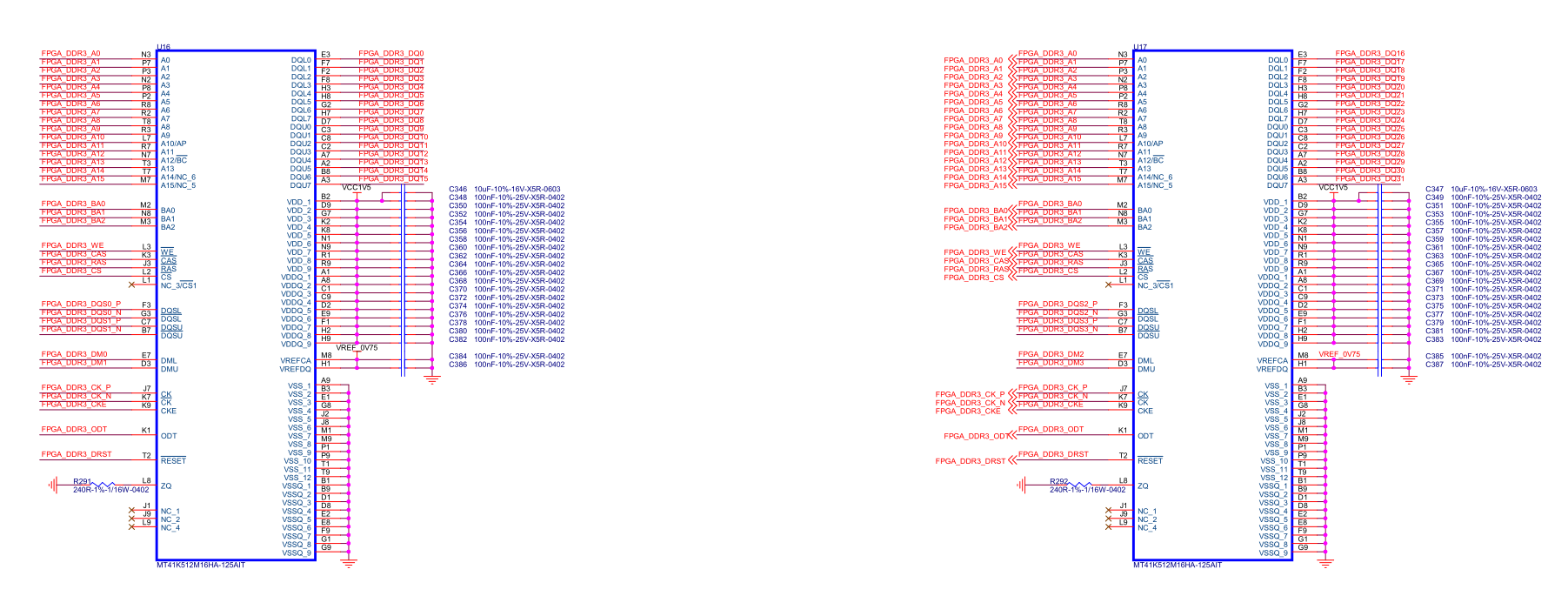

5.һ��IP��������DDR3

����ԭ��ͼ,��������Ŀ���,����DDR3����ͬ�Ŀ�����������һ������������ͬ����,���������Ǹ������ġ���ôҲ����˵,����FPGA����,���ⲿ��λ��Ϊ16bit������DDR������һ��λ��Ϊ32bit��DDR3�����ơ�����������Ϊ����������;����Ϊ��ƥ��rankλ��;����Ϊ����������,����Ƭ������Ƭ��������ƬDDR3����һ��

�������ֳ���,MIG���õ�ʱ����ɶע��������?ֻ��Ҫ��4.3��IP���õ�5���е�data width����Ϊʵ��оƬ��������λ�����ɡ�����Ƭ16bitλ����������,������λ��Ϊ32bit���ɡ��������ɵ�IP�˵Ľӿ���app_addr�Ի���һλ,��һλ��Ȼ��rank������λ,����ʵ�����塣������û����Ұ�������һƬλ��Ϊ32bit��DDR3���ɡ�

ʵ����,�û������32bit������ʵ�ʴ��ʱ,��λ16bit�͵�λ16bit�����ݱ��ŵ���ͬ����ƬDDR3��,Ψһ�Ĺ�������,������λ�õ�����ֵ����ȵĶ��ѡ�

6.DDR3��ƹ��Ӧ��

�Բɼ�����ͷ����Ϊ��,��DDR3��������оƬ,��ôƹ�Ҳ�����˼������DDR�п��������СΪ1֡ͼ��Ļ�����,�����ȡ�ٶȴ���д���ٶȵ�ʱ��,��Ҫ����ƹ�Ҳ����ķ�ʽ����DDR���Ի�������á���������д��ʱ��,1�Ż�����д��֮��,�л���2�Ż�����д,2��д��֮��,����1��ȥд,������������ڶ�ȡ�ٶȴ���д���ٶ�,���,��һ�������뵱ǰд��ͬ����һ�黺����ȥ��,�ڵײ�,���ܻ��ͬһ�黺���������ݶ�ȡ�ܶ��,�����Ⲣ��Ӱ�������Ӿ��϶��ڻ���������Ӱ�졣�����ͨ��ƹ�Ҳ���ʵ�������ݻ���,ƥ���˶�д���˵��ٶȡ�����ͼ��ʾ,

˵��:1.ÿһ��bank�洢һ֡ͼ������,bank��ÿһ��Ϊͼ���һ������(��ÿһ�ζ�д��ͻ��������һ����������),����д�˴˶�������;2.bank֮����л���״̬��ʵ��,���ڶ��ٶȴ���д�ٶ�,��ÿд��һ��bank�л���һ��bankȥд;ÿ����һ��bank,�жϵ�ǰдbank,ѡ��ͬ��дbank��bank���ж���3.���ڶ��ٶȴ���д�ٶ�,�����Զ���ᷢ����ͻ,ֻ�ǿ���ijһ֡�ᱻ�ظ�����,������ƵӦ����,����û����Ӿ��������κ�Ӱ�졣��ô��������,����Ƕ����ٶ�С��д���ٶ�,����η���DDR3��������?�������˼��,�����������л��ἰ��