�ֲ�ѧϰ:

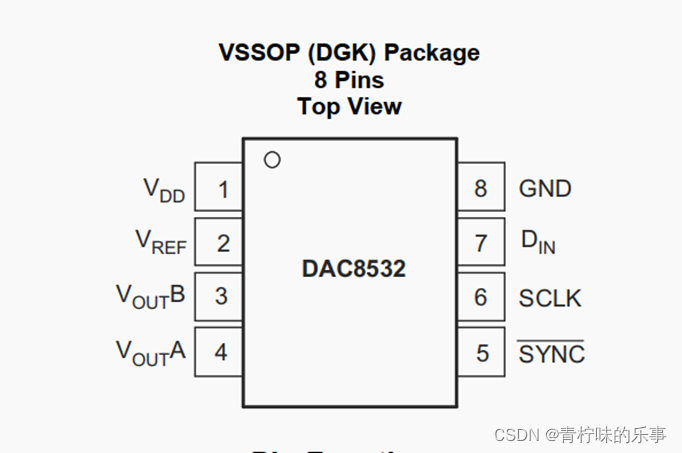

һ���ӿڲ���:

Vdd:��Դ����,2.7 V��5.5 V;

Vref:�ο���ѹ����;

VoutA/VoutB:DAC A/B ��ģ�������ѹ;

SYNC:�������ݵ�֡ͬ���ź�����,�͵�ƽ��Ч,�� SYNC ���ڵ͵�ƽ,��ʹ��������λ�Ĵ���,������ SCLK ���½��ش���;

SCLK: ����ʱ������,���ݿ����Ըߴ� 30 MHz �������� 5 V �´���;

VDD �� 3.6 V ~ 5.5 V ʱ,SCLK���30M;

VDD �� 2.7 V ~ 3.6 V ʱ,SCLK���20M;

DIN :������������,�����ڴ���ʱ��������½��ر���ʱ�� 24 λ������λ�Ĵ���;

GND:

���� ʱ��Ҫ��

�����豸����ģʽ

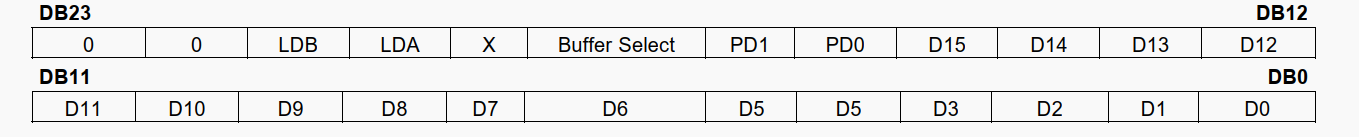

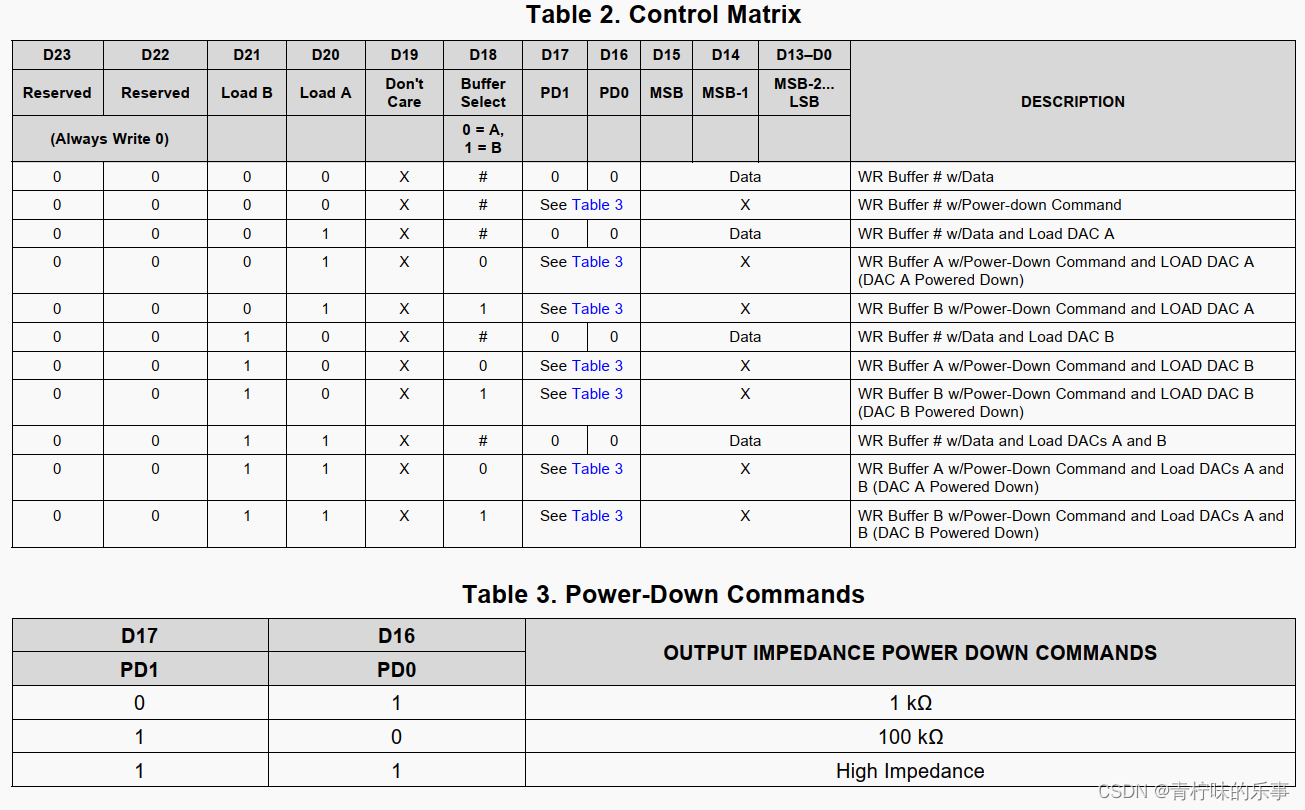

DAC8532 ��������λ�Ĵ���Ϊ 24 λ��(��ͼ),�� 8 ������λ,(DB16�CDB23) �� 16 ������λ (DB0�CDB15) ��ɡ�ǰ��������λ(DB22 �� DB23)�DZ�����,����Ϊ 0 �����������С� LD A (DB20) �� LD B (DB21) ����ÿ��ģ������ĸ���ָ���� 16 λ����ֵ��������λ DB19 ����λ,��Ӱ��DAC8532 �IJ���,������ 1 �� 0������Ŀ���λ,������ѡ�� (DB18),����DAC A �� DAC B ֮������(���������)��Ŀ�ĵء������������λ,PD0(DB16) �� PD1 (DB17),ѡ��һ�������� DAC ͨ���ĵ���ģʽ������ģʽ������ģʽ�����ֵ���ģʽ�е��κ�һ�֡��������IJ���ģʽ����DAC8532 ���ڡ�����ģʽ�������ҵ��� 24 λ��������� 16 λ���������λ����Щ�����͵�ָ�������ݻ������� DAC �Ĵ���,����ȡ���ڿ����ֽڷ���������,�� SCLK �ĵ� 24 ���½��ء�

һ���������ģʽ

�ġ���������

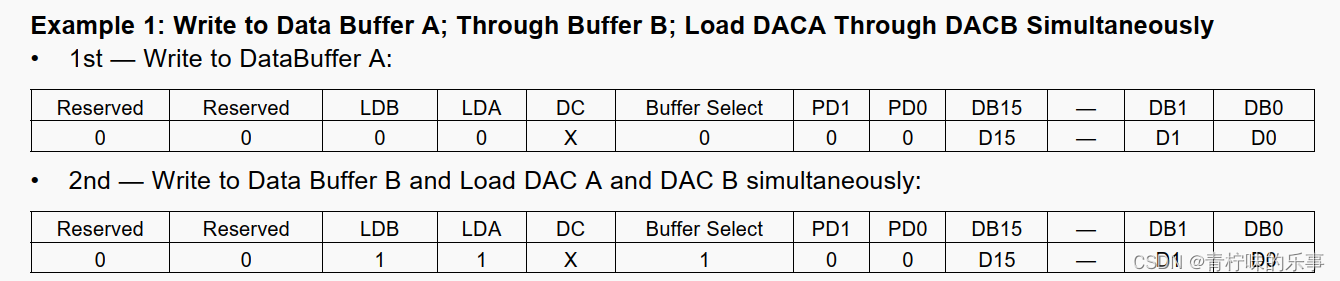

�������õ�������1:DACA �� DACB ģ������ڵڶ�����ɺ�ͬʱ�ȶ���ָ��ֵ��д˳��(�ڸüĴ���ת��������ģ��������µ�ͬʱ,Load ����������ݴ����ݻ������ƶ��� DAC �Ĵ�������SYNC LOW ��ĵ� 24 ��SCLK�½������)

�塢����

�ײ� dac8532_drive.v

module dac8532_drive(

input wire sys_clk,

input wire sys_rst,

input wire [15:0] data_dout,

input wire start,

output reg done,

output wire P_SCLK,

output reg P_SYNC,

output reg P_DIN

);

reg div_clk;

reg sclk_en;

reg [7:0] DAC_ctrl_state;

reg [7:0] SPI_cnt;

reg [7:0] div10_cnt;

reg [23:0] DAC_buf_A;

reg [23:0] DAC_buf_B;

assign P_SCLK = sclk_en ? sys_clk : 1'b0 ;

//--����ʽ״̬��

always@(posedge sys_clk or negedge sys_rst)

begin

if(sys_rst == 1'b0)

DAC_ctrl_state <= 8'd0;

else

begin

case (DAC_ctrl_state)

8'd0:

begin

if(start == 1'b0)

DAC_ctrl_state <= 8'd0;

else

DAC_ctrl_state <= 8'd1;

end

//--д24b���ݵ��Ĵ���

8'd1:

begin

if(SPI_cnt < 8'd24)

DAC_ctrl_state <= 8'd1;

else

DAC_ctrl_state <= 8'd2;

end

8'd2:

DAC_ctrl_state <= 8'd3;

//--�Ĵ�������ͬʱװ�ص�DAC�Ĵ���

8'd3:

begin

if(SPI_cnt < 8'd24)

DAC_ctrl_state <= 8'd3;

else

DAC_ctrl_state <= 8'd0;

end

default:

DAC_ctrl_state <= 8'd0;

endcase

end

end

//--

always@(posedge sys_clk or negedge sys_rst)

begin

if(sys_rst == 1'b0)

begin

sclk_en <= 1'b0;

P_SYNC <= 1'b1;

P_DIN <= 1'b0;

done <= 1'b0;

SPI_cnt <= 8'd0;

DAC_ctrl_state <= 8'd0;

DAC_buf_A[23:0] <= 24'h0;

DAC_buf_B[23:0] <= 24'h0;

end

else

begin

case(DAC_ctrl_state)

8'd0:

begin

done <= 1'b0;

DAC_buf_A[23:0] <= {8'b00000000, data_dout};

DAC_buf_B[23:0] <= {8'b00110100, data_dout};

end

8'd1:

begin

P_SYNC <= 1'b0;

sclk_en <= 1'b1;

if(SPI_cnt < 8'd24)

begin

P_DIN <= DAC_buf_A[23];

DAC_buf_A[23:1] <= DAC_buf_A[22:0];

DAC_buf_A[0] <= 1'b0;

SPI_cnt <= SPI_cnt + 8'd1;

end

else

begin

sclk_en <= 1'b0;

P_SYNC <= 1'b1;

SPI_cnt <= 8'd0;

end

end

8'd3:

begin

P_SYNC <= 1'b0;

sclk_en <= 1'b1;

if(SPI_cnt < 8'd24)

begin

P_DIN <= DAC_buf_B[23];

DAC_buf_B[23:1] <= DAC_buf_B[22:0];

DAC_buf_B[0] <= 1'b0;

SPI_cnt <= SPI_cnt + 8'd1;

end

else

begin

sclk_en <= 1'b0;

SPI_cnt <= 8'd0;

P_SYNC <= 1'b1;

done <= 1'b1;

end

end

default:

P_SYNC <= P_SYNC;

endcase

end

end

endmodule

���� dac8532_demo.v

module dac8532_demo(

input wire sys_clk,

input wire sys_rst,

output wire DAC_SCLK,

output wire DAC_SYNC,

output wire DAC_DIN

);

reg [15:0] DAC_data;//--���ݹ�ʽ��:Vout = Vref * ( DAC_data / 65536 )

wire DAC_done;//--���һ��ת������

reg DAC_start;//--��ʼת��

reg [23:0] cnt;

always @(posedge sys_clk or negedge sys_rst)

begin

if(sys_rst == 1'b0)

begin

DAC_data <= 16'hFFFF;

DAC_start <= 1'b0;

cnt <= 24'd0;

end

else

begin

if(cnt < 24'd10_0000)

begin

cnt <= cnt + 24'd1;

DAC_start <= 1'b0;

end

else

begin

cnt <= 24'd0;

DAC_start <= 1'b1;

end

end

end

dac8532_drive dac8532_drive_1(

.sys_clk (sys_clk),

.sys_rst (sys_rst),

.data_dout (DAC_data),

.start (DAC_start),

.done (DAC_done),

.P_SCLK (DAC_SCLK),

.P_SYNC (DAC_SYNC),

.P_DIN (DAC_DIN)

);

endmodule

���� tb_sim1.v

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2021/12/02 14:25:02

// Design Name:

// Module Name: tb_sim1

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module tb_sim1;

reg clk;

reg rst;

parameter SYSCLK_PERIOD = 100;

initial begin

clk = 0;

rst = 0;

end

initial

begin

#(SYSCLK_PERIOD * 10 )

rst = 1'b1;

end

always #(SYSCLK_PERIOD / 2.0) clk = ~clk; //һ������

wire DAC_SCLK;

wire DAC_SYNC;

wire DAC_DIN ;

dac8532_demo dac8532_demo_1(

.sys_clk (clk),

.sys_rst (rst),

.DAC_SCLK (DAC_SCLK ),

.DAC_SYNC (DAC_SYNC ),

.DAC_DIN (DAC_DIN )

);

endmodule

vivadoǰ����: