录

一、Keil虚拟仿真逻辑仪

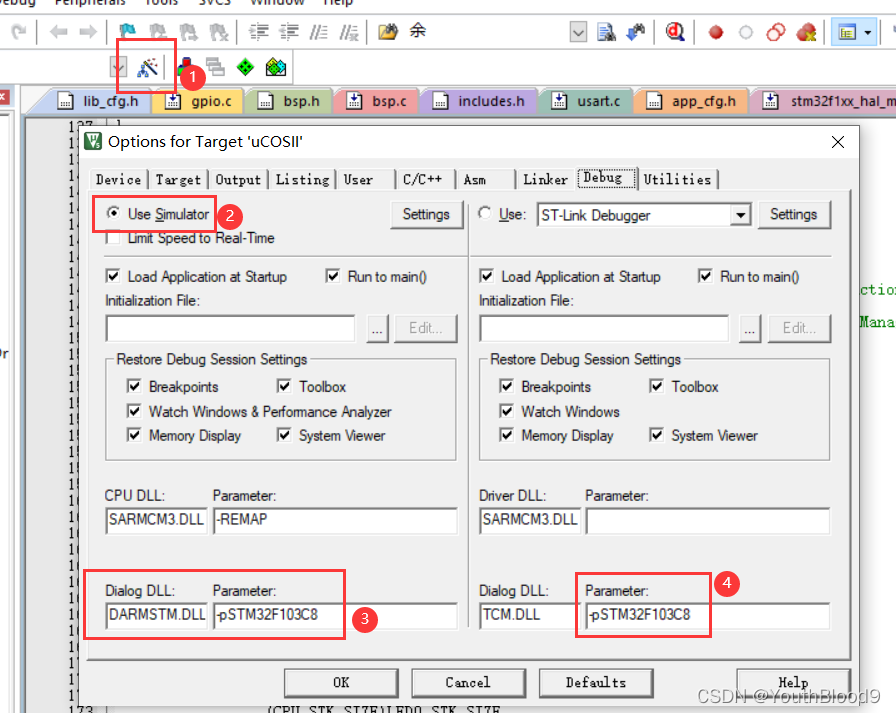

1.1 设置

- 打开一个Keil工程,笔主这里是uCOSII移植项目文件

- 设置

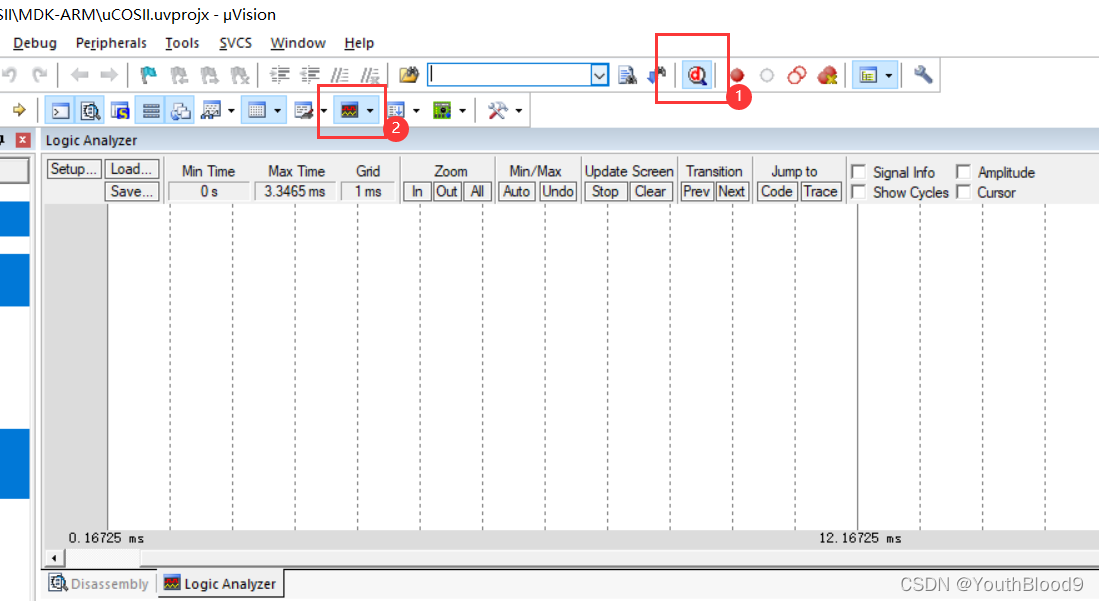

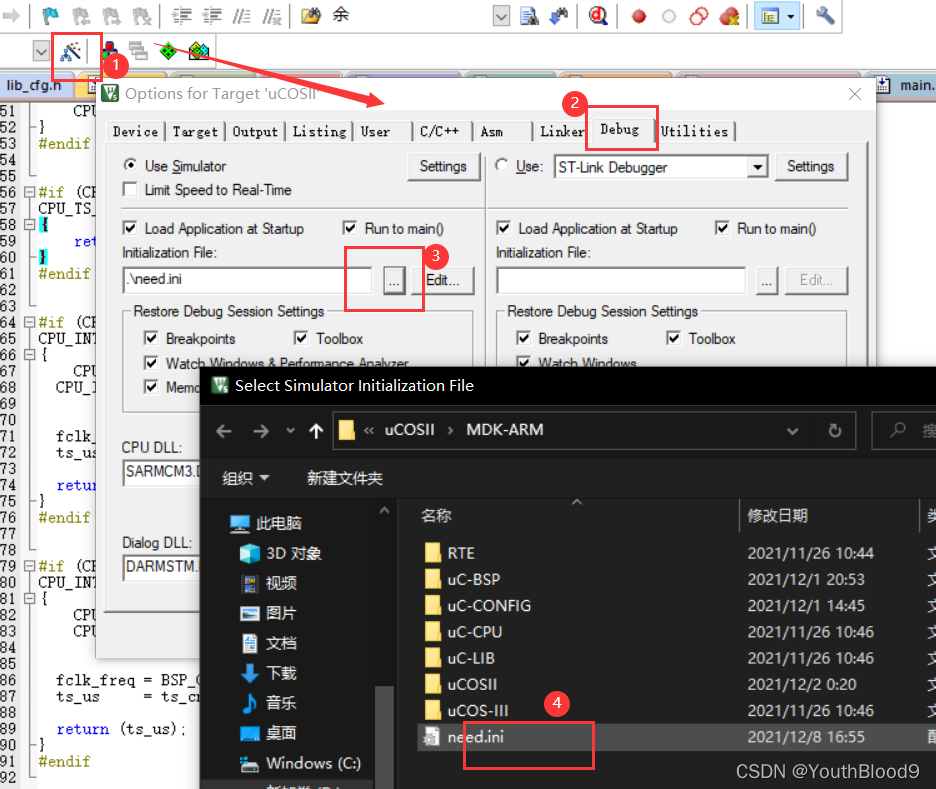

- 进入仿真,先点击①处,再点击②处,就会出现下图界面:

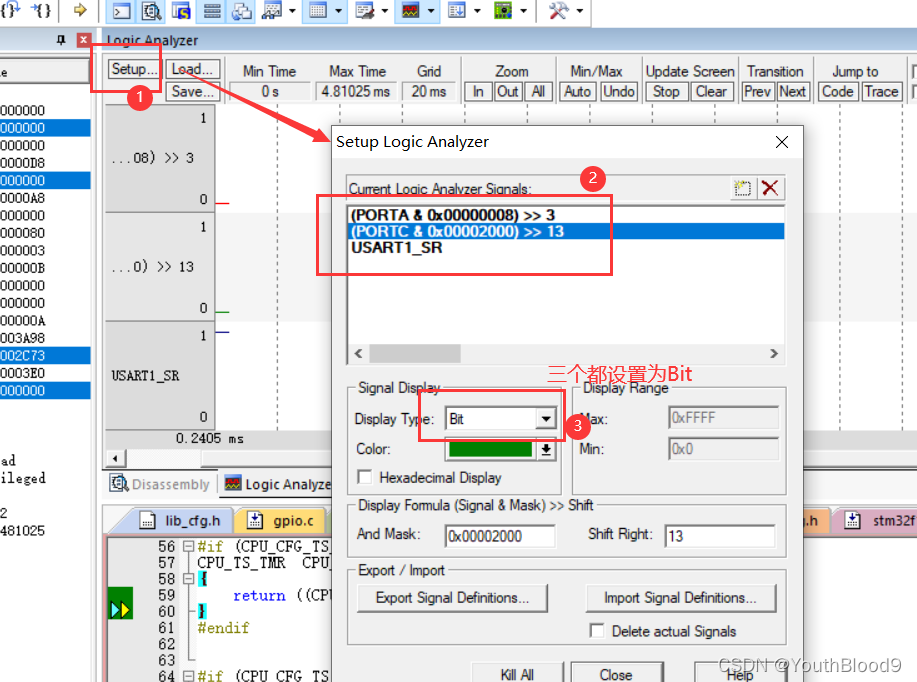

- 仿真设置,添加三个:分别用PORTA.3、PORTC.13、USART1_SR来添加,如下图

- 运行

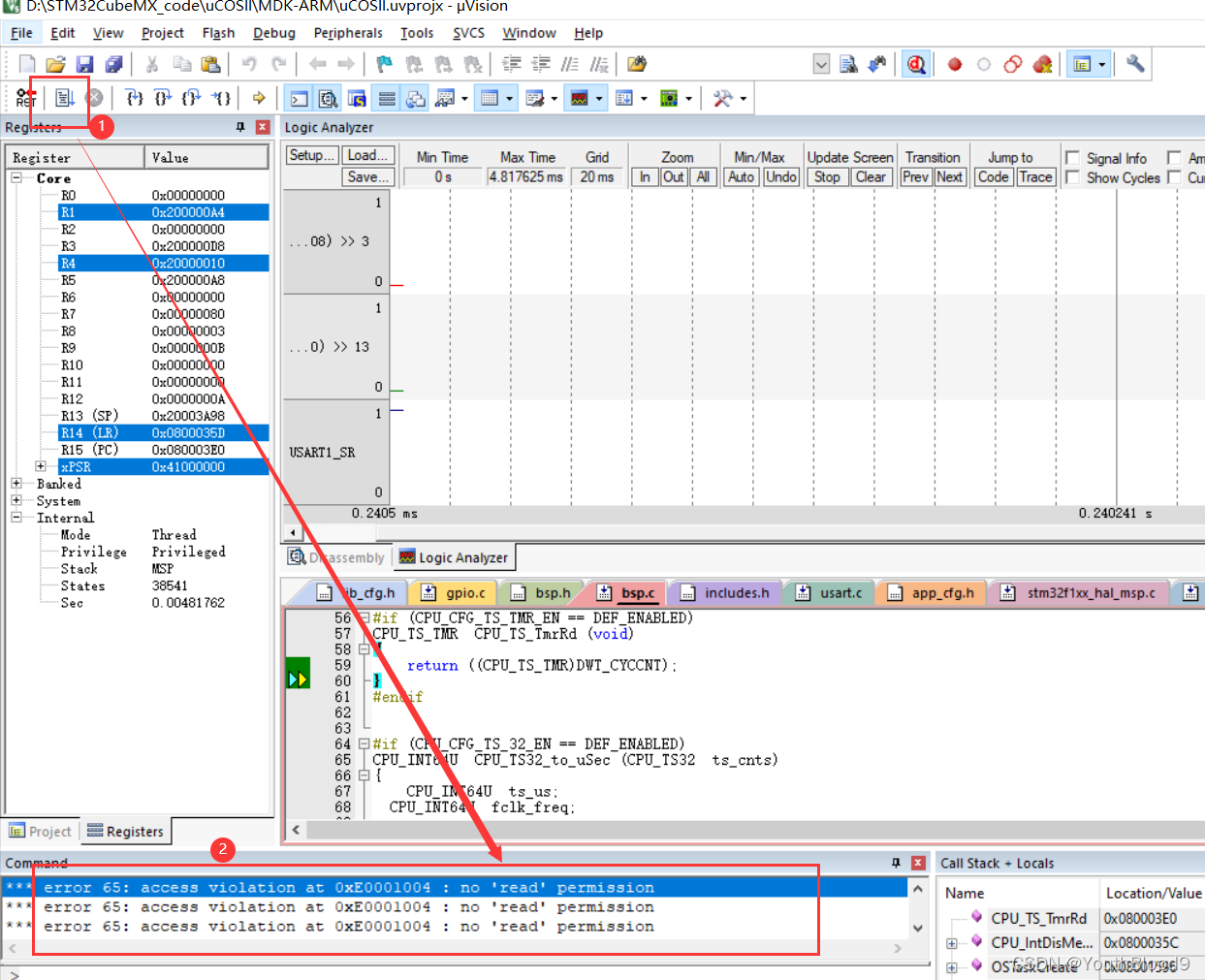

- 我们点击①处,发现有问题出现

1.2 解决自动停止问题

- 这时直接打开仿真示波器运行时会自动停止,并报错某些地址没有写的权限。

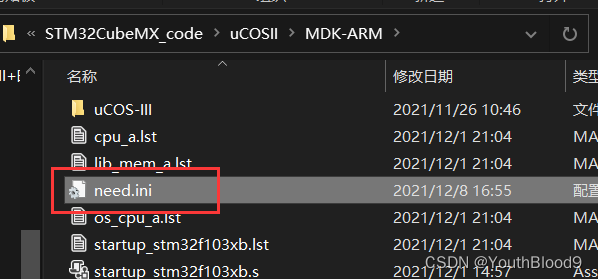

此时需要在工程下添加一个文件。 - 先创建一个TXT文件,并添加以下内容(位置在MDK-ARM下):

map 0x40000000, 0x40007FFF read write // APB1

map 0x40010000, 0x400157FF read write // APB2

map 0x40020000, 0x4007FFFF read write // AHB1

map 0x50000000, 0x50060BFF read write // AHB2

map 0x60000000, 0x60000FFF read write // AHB3

map 0xE0000000, 0xE00FFFFF read write // CORTEX-M4 internal peripherals

-

然后修改文件后缀为.ini

-

将文件添加到项目

1.3 运行结果

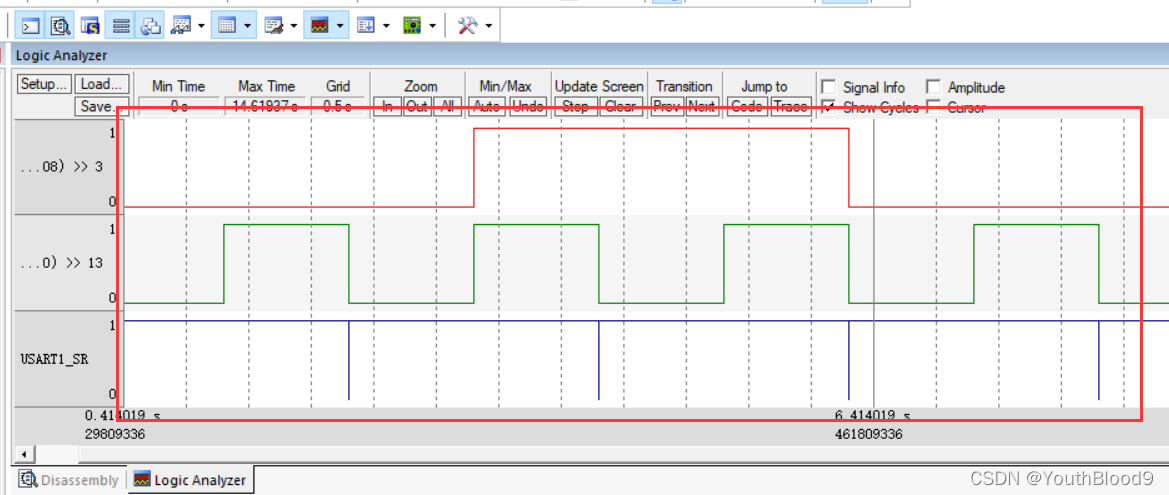

- 此时我们编译后,再打开仿真逻辑

- 运行,就会出现以下结果:

- 可观察到PC13引脚电平变化周期为2s,PA3引脚电平变化周期为6s,串口USART1周期为2s。

- 与代码一致。

二、使用真实仿真仪

2.1 SaleaeLogic16 功能特点简介

- Saleae16逻辑分析仪,界面操作简单,易学,易用,是电子开发人员调试、分析的好工具

- Saleae16是将采样出来的实时数据送入电脑内存中,应用压缩算法,深度最高可达10G

- Saleae16可以自动分析多种常用通信协议,直接得到分析数据,其中SaleaeLogic_1.1.15 支持10种协议解释,SaleaeLogic_1.1.16支持17种协议解释,包括: AtmelSWI,Biss ,CAN,DMX-512, I2C, I2S/PCM, JTAG,LIN,Manchester,MDIO,1-Wire,PS/2Keyboard/Mouse,AsyncSerial,Simple Parallel, SPI, UNI/O,USB1.1

- Saleae16采用资源动态复用,3个通道最高采样率100M,6个通道最高采样率50M,9个通道最高采样率32M,16个通道最高采样率16M

- Saleae16使用的USB接口,必须是USB2.0接口

- Saleae16采集的数据可以选择存储, 导出表格,数据显示支持数据显示成为10进制、16进制、二进制、ASCII码,便于进行数据分析和数据比较

- 支持上升沿、下降沿、高电平、低电平等多种触发方式,也可选取多个通道“与逻辑”的关系进行触发选择,方便、实用

- 软件支持多种采集频率和采集深度, 可根据实际应用需求自由结合

- 还支持模拟输出功能,可以对软件本身支持的协议格式进行模拟演试输出

2.2 下载

- 百度网盘

链接:https://pan.baidu.com/s/1VvR8i3kS5VWZ44x9YWpeAQ

提取码:0011 - 下载成功后解压安装,一路NEXT即可

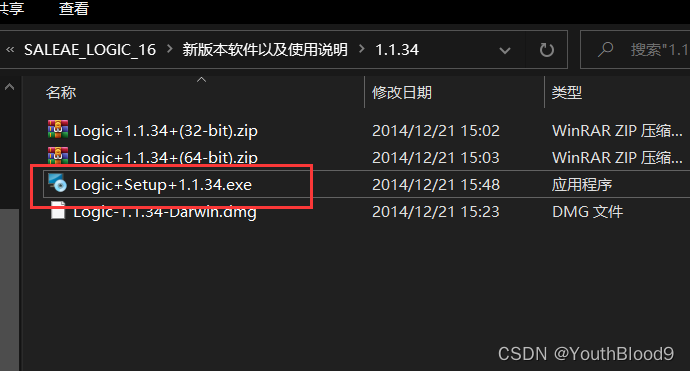

- 笔主安装的下面这个

- 安装成功后,打开

2.3 使用

2.3.1 了解软件

-

打开软件

在安装软件的同时,驱动程序已经被注册到系统了了,当插入 SALEAE 16 逻辑分析仪后就可以自动安装安装驱动。

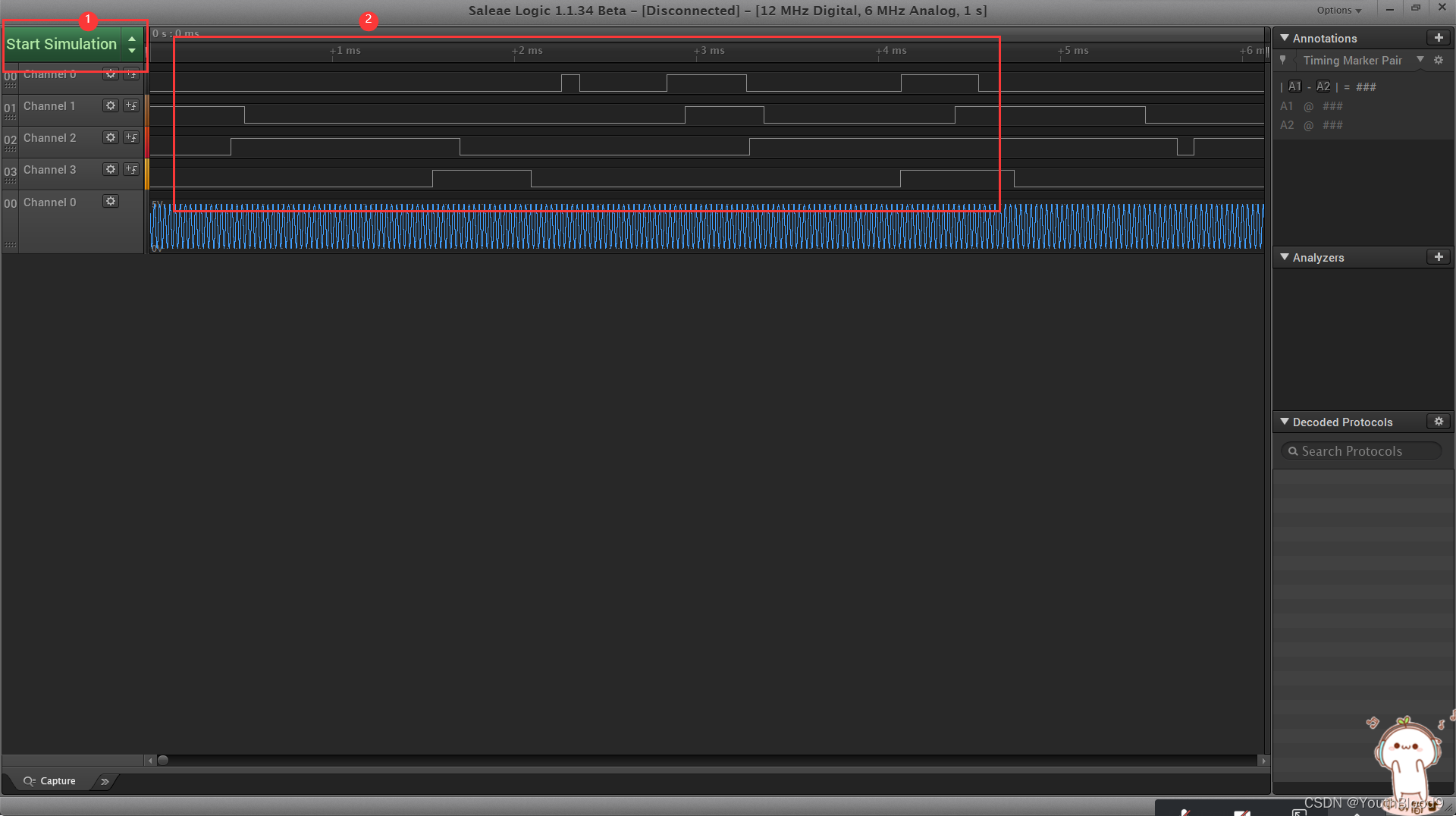

打开界面如下图,软件界面基本是左中右的布局,左边主要是采集和显示设置,右边是分析和解析设置,中间是波形显示区域。 -

软件支持脱机模拟采集,没有实际的硬件也可以感受一下软件的界面和操作。

-

如:点Start Simulation ,可以在波形区域模拟显示出一些软件生成的数据,如果设置了解析,可以根据所设置的协议,生成一些符合协议解析要求的模拟数值。

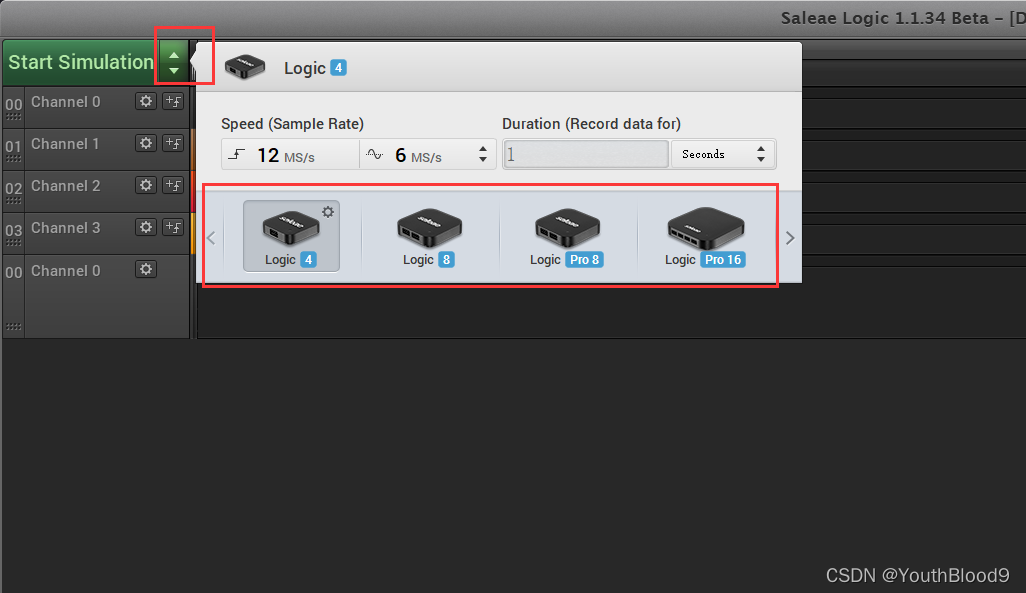

- 设备选择,可以自行选择,但接入逻辑仪之后,会自行发生改变

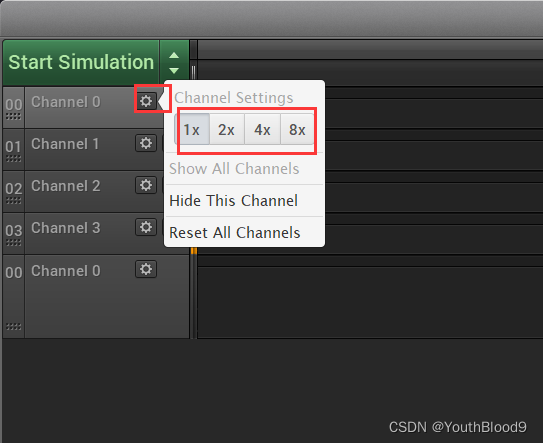

- 单个通道设置

第一项是波形幅值比例,可以通到进行修改不同的比例。

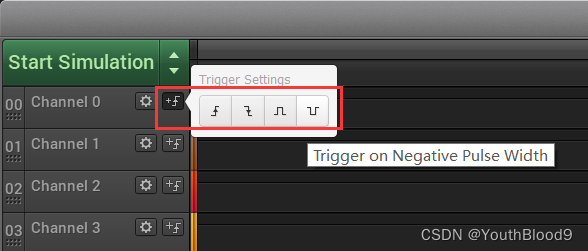

- 修改触发方式

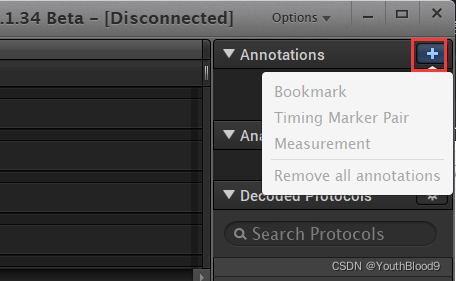

- Annotations选项

Timing Marker Pair增加电平时间的组数

- Analyzers选项

包含了多种协议,如串口,SPI,IIC,CAN等。

2.3.2 示例

- 这里以uC/OS移植的代码为例:

- 接入逻辑仪后,自动变为16通道的:

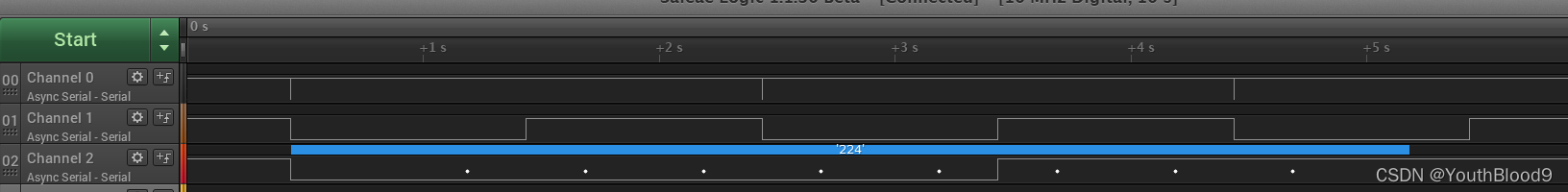

- 这里使用通道0,1,2

- 分别将stm32f103c8t6的引脚PA9,PC13,PA3接到通道0,1,2,同时将一个GND接地。

- 点击start,得到:

- 可以看到PA9电平变化周期2s,PC13电平变化周期2s,PA3电平变化周期6s。

- 这与上述使用Keil仿真逻辑分析仪得出结果一致,与代码中的设置也是一致的。

小小的总结

本次是使用Keil自带的仿真调试查看示波器输出,也新学使用真的逻辑仪来进行显示波形。

了解到了逻辑仪的基本操作和Logic软件的基本原理。