zynq7020的arm cortex A9核降频实录

zynq7020的arm核默认配置下运行频率666.666Mhz;DDR3的默认频率为533.333Mhz。好端端的为啥要降频呢,答案是烫!对于只用到PL部分,或者PS部分用得少(不跑os,不做UI等)的情况,降频对于功耗、温度控制来说将是一个有效途径。

操作依据

-

数字芯片动态功耗 P 正比于 C*V^2 * f,C是开关等效电容、V电压、f 即开关频率,显然f降,功耗会降。

-

zynq7000的降频相关教程目前比较少(至少我没有搜到),所以为数不多的参考依据只有看官方的英文手册了。

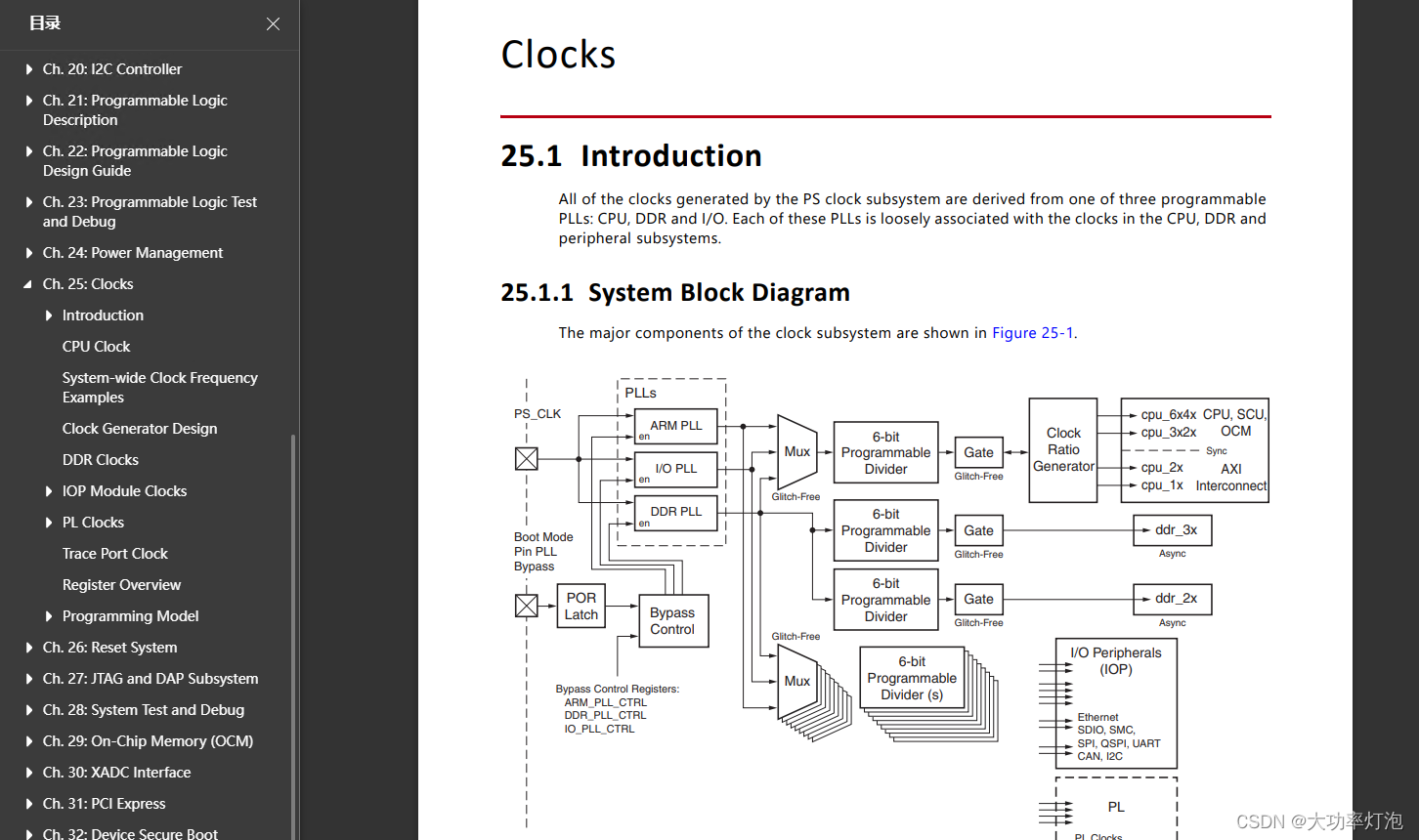

手册又多又杂,首先从ug585着手,有一章节专门讲CLOCK的,大家可以去看下。这一章主要讲了PS部分的时钟逻辑树,时钟关系等,但全然没提降频或者变频一事,但反复提到要去datasheet看实际允许频率,还提到一个power management似乎和低功耗有些关联。

-

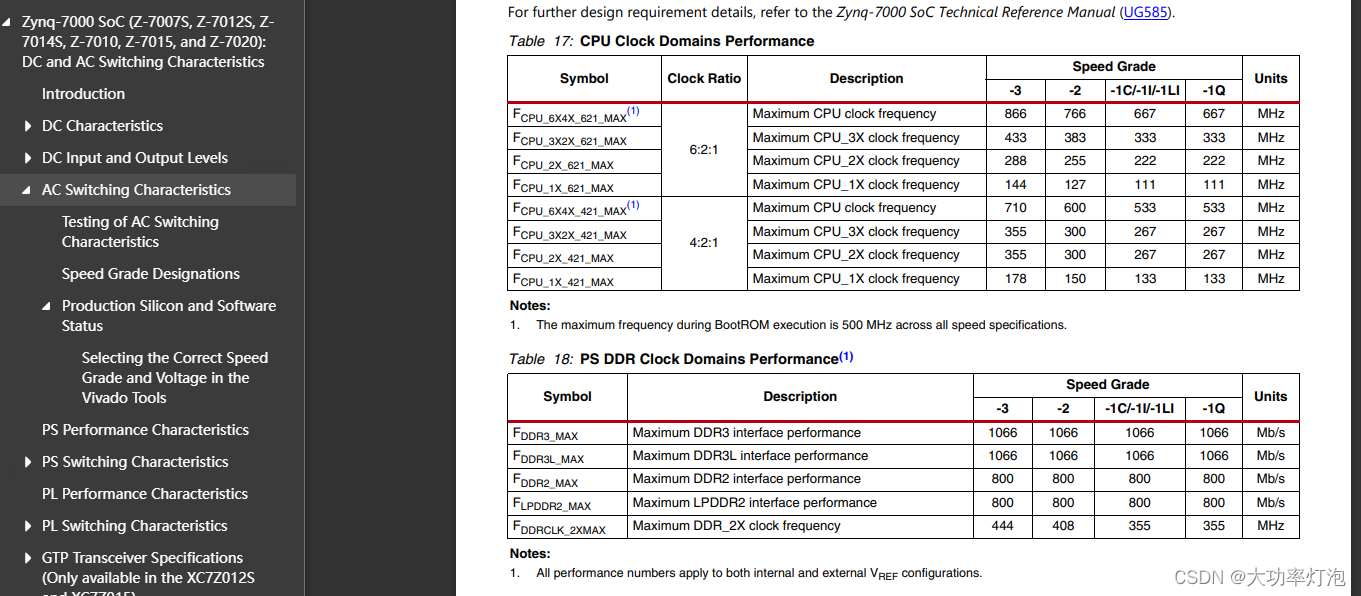

承接ug585提到的datasheet,那么多datasheet,我想应该是指da/ac switch特性手册,我们又来到ds187-XC7Z010-XC7Z020-Data-Sheet。70多页翻上翻下,也就只有这个AC switching章节和cpu、ddr频率有点关系,但全是讲Maximum的,吹的全是极限上限频率。这仿佛在告诉我们没有下限?

-

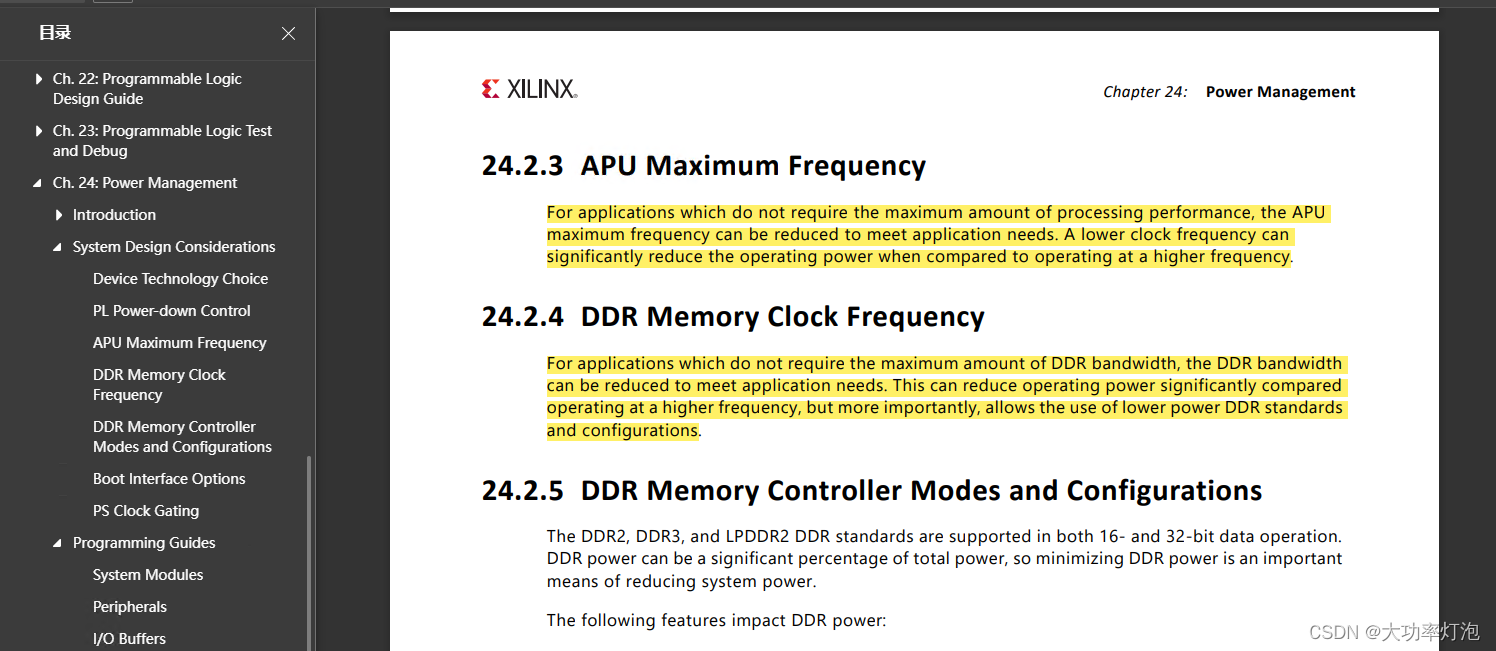

我们继续回到ug585,看看25.clock章节提到的24.power management,读上读下,没有太多具体操作,只是隐约告诉我们,可以进行一些操作(包括sleep mode,单CPU模式,PL关断等)来降低功耗,比较重要的两段话如下:

这告诉我们,在一些不需要极限性能的场合,可以降低APU、DDR频率来满足功耗需求。

降频操作实录

・・・・上文,ug585的clock告诉我们了时钟关系,dc/ac开关特性高速了极限性能,power management 传达我们可以进行降频操作。但是面对下面的众多时钟具体怎么降一无所知,降了会有什么问题,也一无所知,所以我在这儿记录一下相关过程。

1. 时钟参数介绍

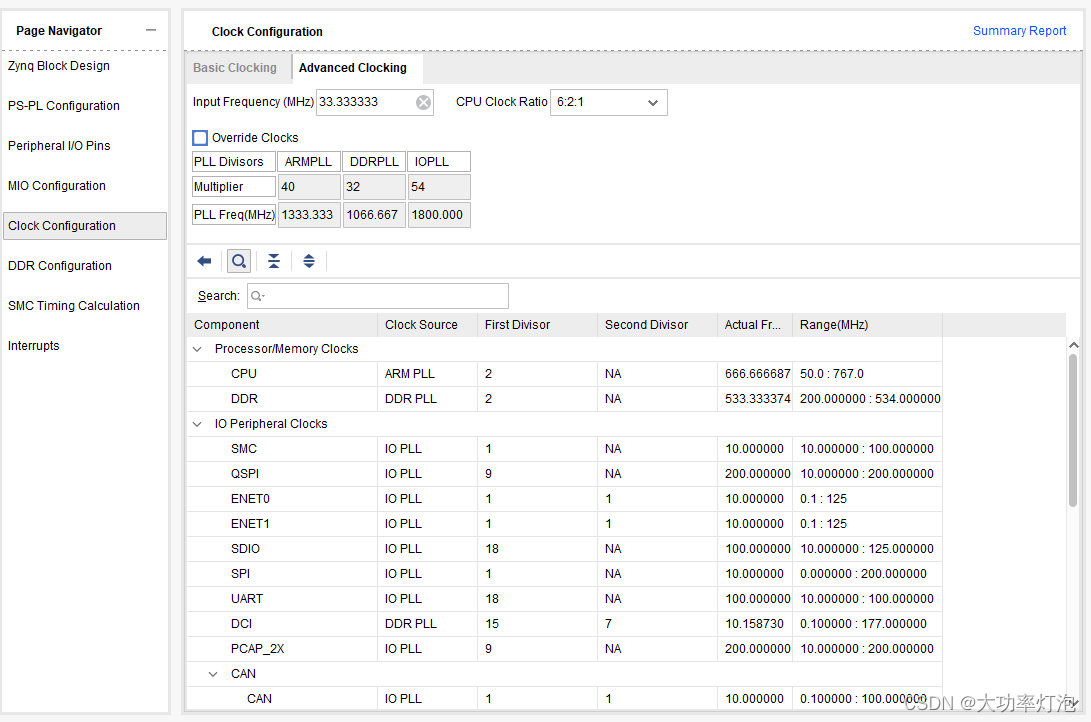

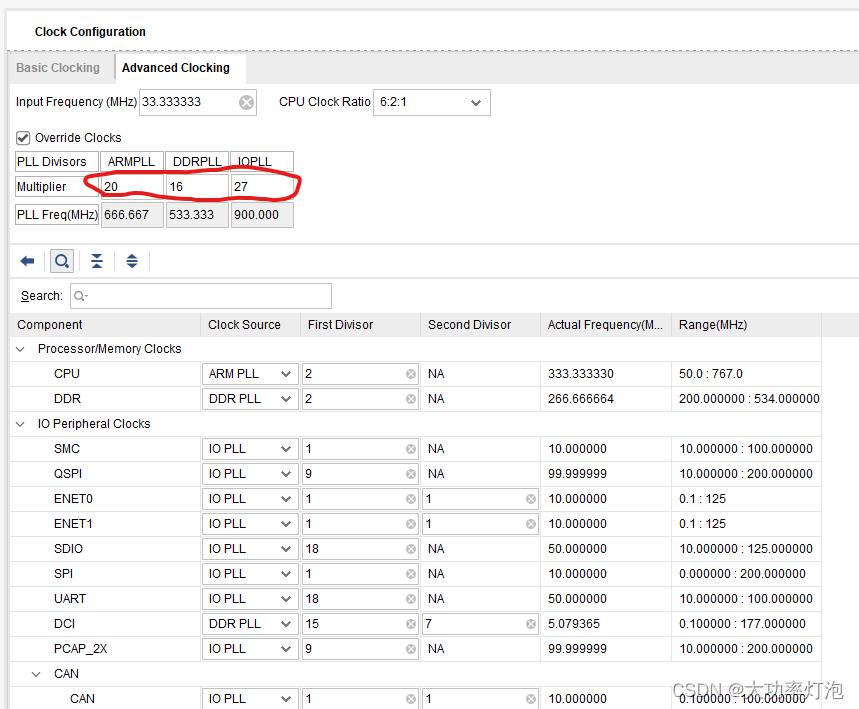

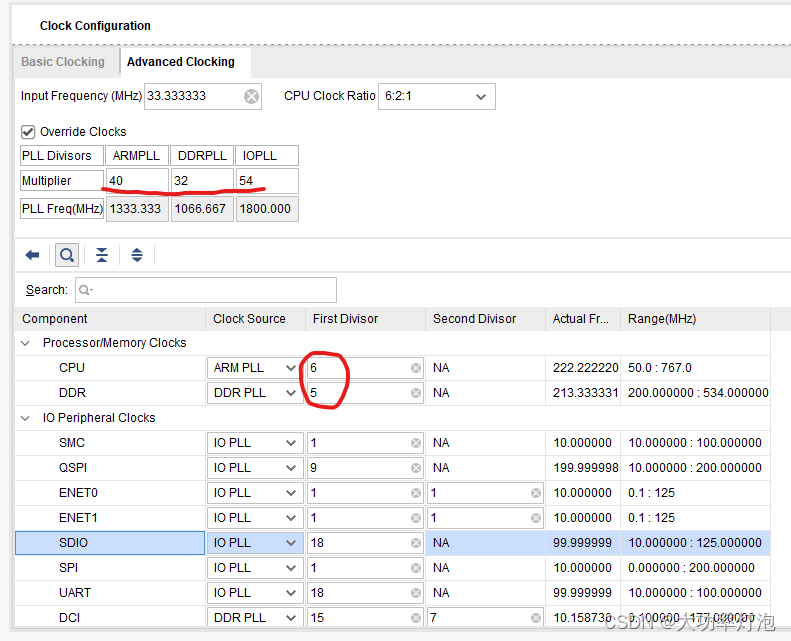

首先进入上述zynq核的advanced clocking配置界面,我们先认识一下这些参数,

Input Frequency: 输入频率,即PS部分的板载晶振频率,这里不能乱改,要根据实际晶振频率来。

CPU Clock Ratio: CPU时钟比例,有两个选项6:2:1和4:2:1, 参看ug585这是6:2:2:1,和4:2:2:1的简写,大概意思就是CPU频率和次级外设(总线等)以及外设(timer等)比例为6:2:2:1/ 4:2:2:1。ug585的原语是,一个系统性能的瓶颈可能并不总是在于APU部分,很可能在外设上,4:2:1下各级频率相比6:2:1更集中,也即CPU频率一定时(CPU_6x4x),4:2:1的cpu_1x比6:2:1的cpu_1x更高。

override clocks: 勾选了就允许自行配置,取消勾选恢复默认,这里我们勾选。

PLL Divisors :这一栏是3个时钟源的倍频因子,即33.33333M*40 = 1333.3333M

下面component栏即我们实际要操作的各项具体参数

第一列为类型没什么好说的,

第二列为clock source,一共有4个出现的源:ARM_PLL、DDR_PLL、IO PLL、External、 CPU 1X。前3个即手册上的3类clock源,External即外部源,CPU 1X为ARM_PLL的1/6或者1/4(取决于上面的CPU Clock Ratio),这一列我们也不动。

第三列First Divisor,分频因子,这一列是我们操作的重点。

第四列即第二分频因子,少部分应用到,此处不动。

后两列显示实际频率和频率范围的。

2. 小试牛刀-------砍一半频率

懒得一个一个调,直接倍频因子集体砍半试试行不行。

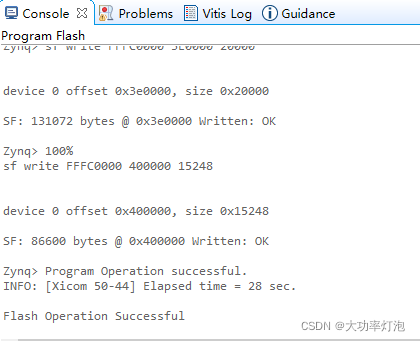

导出hardware在vitis试试:

正常下载运行,flash固化成功,PL逻辑正常,即完成了只使用PL时的基本要求。

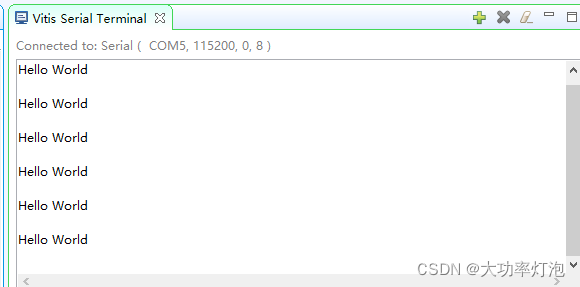

再加个hello world串口试试:

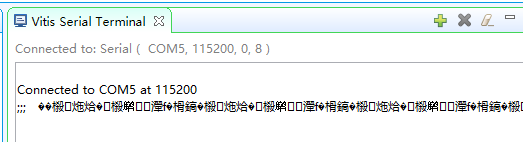

原设置115200下,接收乱码。

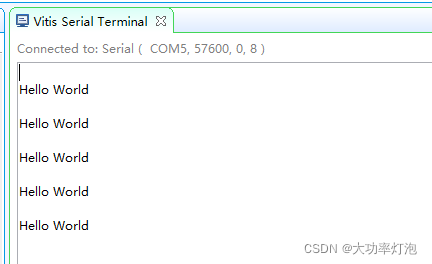

波特率换成一半57600串口接收正常。

原来115200的串口速率变到57600才能匹配,应该是IO速率砍一半导致的。

当然最重要的温度,手摸感觉应该是没有那么烫了,20℃环境连续运行1小时,DDR手感微热,zynq散热盖手感比DDR略热,估摸着40摄氏度左右,但相比于600Mhz下烫手好了很多。

3.实际调节参数

・・・・@ 1. 我的常识是CPU频率要略高于ddr频率,然后一般远高于其他外设频率.

・・・・@ 2.上面串口波特率被砍半,可能其他外设也有这个问题,鉴于外设比较少,且一般外设频率都较低,故默认不降。

・・・・@ 3.倍频因子不是越小越好,需要和分频因子配合出一套频率允许最低值,DDR最低允许200M,CPU应略高于200M。

如下,注意标红部分数值,其他均默认。

实际修改后,CPU频率222.222Mhz,ddr 213.333Mhz, 外设频率默认没变(qspi挺高的200M)。

结果,串口115200恢复正常:

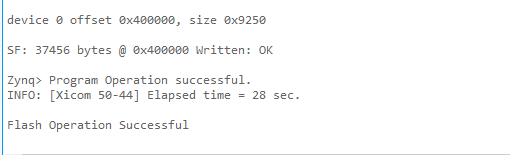

固化到qspi-flash试试,功能正常:

上电一小时试试,

差不多也是温热

其他情况就不试了。