ЮФеТФПТМ

4.ДІРэЦїЬхЯЕМмЙЙ|

жИСюМЏ"Y86-64"

4.1ГЬађдБПЩМћЕФзДЬЌ

RF:ГЬађМФДцЦї

CC:ЬѕМўТы

Start:ГЬађзДЬЌ(ГЬађЕФжДаазДЬЌ)

PC:ГЬађМЦЪ§Цї

DMEM:ФкДц

15Иі64ЮЛФкДцЕФГЬађМФДцЦї

Y86-64 ЯрБШx86,ЪЁТдСЫ%r16

ЬиБ№ЕФ:%rsp:еЛжИеы

movq:rrmovqЁЂirmovqЁЂrmmovqКЭ mrmovq

movqЧАСНИізжФИБэЪОСЫдДКЭФПЕФИёЪН

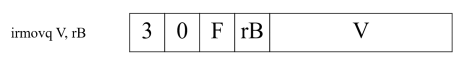

irmovq

дДВйзїЪ§ЪЧСЂМДЪ§(Immediate)

ФПЕФВйзїЪ§ЪЧМФДцЦї(register)

rrmovq

дДВйзїЪ§ЪЧМФДцЦї(register)

ФПЕФВйзїЪ§ЪЧМФДцЦї(register)

rmmovq

дДВйзїЪ§ЪЧМФДцЦї(register)

ФПЕФВйзїЪ§ЪЧФкДц(memory)

mrmovq

дДВйзїЪ§ЪЧФкДц(memory)

ФПЕФВйзїЪ§ЪЧМФДцЦї(register)

ЖдЩЯУцЪ§ОнДЋЫЭжИСюНјааБрТы

ЩЯЭМжаУПЬѕжИСюЕквЛИізжНк(8bit)(ЧАСНЮЛ)БэУїжИСюЕФРраЭ,етИізжНкЗжЮЊСНВПЗж,УПВПЗжеМ(4bit),ИпЫФЮЛ(4bit)БэЪОжИСюДњТы,ЕЭЫФЮЛ(4bit)БэЪОжИСюЙІФм

ЯТУцЮЊСЫЗНБуИјМФДцЦїНјааБрКХ

МФДцЦїБрКХ(0-14)

0 %rax

1 %rcx

2 %rdx

3 %rbx

4 %rsp

5 %rbp

6 %rsi

7 %rdi

8 %r8

9 %r9

A %r10

B %r11

C %r12

D %r13

E %r14

F ЮхМФДцЦї

irmovq,ИУжИСюЕФжИСюДњТыЮЊ3,жИСюЙІФмЮЊ0

гЩгкдДВйзїЪ§ЪЧСЂМДЪ§,вђДЫгУ0xFНјааЬюГф

4.1.1 ЫФЬѕећЪ§Вйзї

ЖдгкећЪ§ЕФВйзї,ЮвУЧЖЈвхСЫЫФЬѕећЪ§ВйзїжИСю,КЭx86-64ВЛЭЌ,ЮвУЧЖЈвхЕФжИСюжЛдЪаэЖдМФДцЦїжаЕФЪ§ОнНјааВйзї

вдЩЯЫФЬѕжИСюЪєгкЭЌвЛРраЭ,жИСюДњТыЪЧвЛбљЕФ,ВЛЭЌЕФЪЧжИСюЕФЙІФм

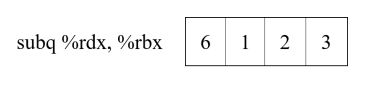

Opq rA,rB 6|fn|rA|rB

addq 6|0

subq 6|1

andq 6|2

xorq 6|3

вдЩЯЫФЬѕжИСюЪєгкЭЌвЛРраЭ,вђДЫжИСюДњТыЪЧвЛбљЕФ,ВЛЭЌЕФЪЧжИСюЕФЙІФм

4.1.2 ЦпЬѕЬјзЊжИСю

ЖдгкЬјзЊ,ЮвУЧЖЈвхСЫ7ЬѕЬјзЊжИСю,ЫќУЧЕФЬјзЊЬѕМўКЭx86-64жаЕФЬјзЊжИСюЯрЭЌ,ЖМЪЧИљОнЬѕМўТыЕФФГжжзщКЯРДХаЖЯЪЧЗёНјааЬјзЊ

jxx Dest

jmp 7|0

jle 7|1

jl 7|2

je 7|3

jne 7|4

jge 7|5

jg 7|6

JMP Label 1 жБНгЬјзЊ

JMP *Operand 1 МфНгЬјзЊ

JE Label JZ ZF ЯрЕШ

JNE Label JNZ ~ZF ВЛЯрЕШ

JS Label SF ИКЪ§

JNS Label ~SF ЗЧИКЪ§

JG JNL Дѓгк(гаЗћКХ>)

JGE JNLE ДѓгкЕШгк(гаЗћКХ)

JL JNG аЁгк(гаЗћКХ)

JLE JNGE аЁгкЕШгк(гаЗћКХ)

JA JNB Дѓгк(ЮоЗћКХ)

JAE JNBE ДѓгкЕШгк(ЮоЗћКХ)

JB JNA аЁгк(ЮоЗћКХ)

JBE JNAE аЁгкЕШгк(ЮоЗћКХ)

4.1.3 СљЬѕЪ§ОнДЋЫЭжИСю

rrcomvqгаЯрЭЌЕФжИСюИёЪН,жЛгаЬѕМўТыТњзуЬѕМўЪБВХЛсИќаТФПЕФМФДцЦїЕФжЕ

comve S,R ЯрЕШ

cmovne S,R ВЛЯрЕШ/ЗЧСу

cmovs S,R ИКЪ§

cmovns S,R ЗЧИКЪ§

cmovg S,R Дѓгк(гаЗћКХ)

cmovge S,R ДѓгкЕШгк(гаЗћКХ)

cmovl S,R аЁгк(гаЗћКХ)

cmovle S,R аЁгкЕШгк(гаЗћКХ)

cmova S,R Дѓгк(ЮоЗћКХ)

cmovae S,R ДѓгкЕШгк(ЮоЗћКХ)

cmovb S,R аЁгк(ЮоЗћКХ)

cmovbe S,R аЁгкЕШгк(ЮоЗћКХ)

cmovxx rA,rB

rrmovq 2|0

comvle 2|1

comvl 2|2

cmove 2|3

cmovne 2|4

cmovge 2|5

cmovg 2|6

ЯЕЭГВйзїжИСю

halt 0 0

nop 1 0

call Dest 8 0 Dest

ret 9 0

pushq rA A 0 rA F

popq rA B 0 rA F

жИСюБрТы

дкЩЯУцЕФВйзїжИСюжа

- haltжИСюЭЃжЙжИСюЕФжДаа,жДааИУжИСюЛсЕМжТДІРэЦїЭЃжЙ,ВЂНЋзДЬЌТыЩшжУЮЊHLT

- nop жИСюБэЪОвЛИіПеВйзї

- call КЭretжИСюЗжБ№ЪЕЯжКЏЪ§ЕФЕїгУКЭЗЕЛи

- push КЭpop жИСюЗжБ№ЪЕЯжШыеЛКЭГіеЛЕФВйзї

жИСюБрТы

rmmovq %rsp,0x123456789abcd(%rdx)

rmmovq

дДВйзїЪ§ЪЧМФДцЦї(register)

ФПЕФВйзїЪ§ЪЧФкДц(memory)

ИљОнЧАУцrmmovqжИСюЕФБрТыЖЈвх,ИУжИСюЖўНјжЦБэЪОЕквЛИізжНкЮЊ0x40;

жИСюВйзїЪ§ВПЗжЕФМФДцЦї%rspЖдгІЕФМФДцЦїБрКХЮЊ0x4,ЛљжЗМФДцЦїrdxЖдгІЕФБрКХЮЊ0x2

ИУжИСюЖўНјжЦБэЪОжаЕФЕкЖўИізжНкЮЊ0x42

жИСюБрТыжаЦЋвЦСПеМ8ИізжНк,вђДЫЮвУЧашвЊдкИУЦЋвЦСПЧАУцВЙ0РДДеЦы8ИізжНкЁЃ

гжгЩгкЮвУЧВЩгУаЁЖЫЗЈДцДЂ,вђДЫЮвУЧЛЙвЊЖдЦЋвЦСПНјаазжНкЗДађВйзїЁЃзюжеЮвУЧЕУЕНИУжИСюЕФЖўНјжЦБэЪОШчЯТ

40 42 cd ab 89 67 45 23 01 00

Y86-64ЕФзДЬЌТы

| жЕ | Ућзж | КЌвх |

|---|---|---|

| 1 | AOK | е§ГЃВйзї |

| 2 | HLT | гіЕНhaltжИСю |

| 3 | ADR | гіЕНЗЧЗЈЕижЗ |

| 4 | INS | гіЕНЗЧЗЈжИСю |

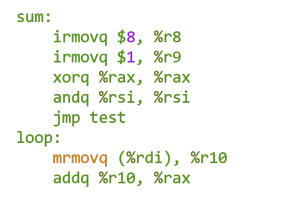

Y86-64жаcгябдЕФЛуБрЗвы

long sum(long *start,long count){

long sum=0;

while(count){

sum+=*start;

start ++;

count --;

}

return sum;

}

gcc -Og -S sum.c

ЕУЕН

cгябдДњТыЕФзїгУЪЧМЦЫувЛИіЪ§зщЕФдЊЫижЎКЭЁЃЦфжажИеыstartжИЯђЪ§зщЕФЦ№ЪМЮЛжУ,countгУгкБэЪОЪ§зщЕФГЄЖШ

ПЩвдПДЕН,Г§СЫЪ§ОнДЋЫЭжИСюжЎЭт,Y86-64жИСюгыx86-64ЕФжИСюЯрВюВЛДѓ

ПДПДЩЯУцЕФЛуБрДњТыЪЧШчКЮЗвыГЩЖўНјжЦжИСюЕФ

НзЖЮЕФИХФю

ДІРэЦїдкжДааЕЅЬѕжИСюЕФЪБКђ,ЭљЭљвВАќКЌзХКмЖрВйзї

Й§ГЬзщжЏГЩЯТУц6ИіНзЖЮ

- ШЁжЗ

ДІРэЦїжДааЕФЫљгажИСюЖМашвЊШЁжЗ

дкY86-64жИСюЯЕЭГжа,жИСюЕФГЄЖШВЛЪЧЙЬЖЈЕФ,вђДЫШЁжЗНзЖЮашвЊИљОнжИСюДњТыХаЖЯжИСюЪЧЗёКЌгаМФДцЦїжИЪОЗћЁЂЪЧЗёКЌгаГЃЪ§РДМЦЫуЕБЧАЕФжИСюГЄЖШ

- выТы

дквыТыНзЖЮжа,ДІРэЦїДгМФДцЦїЮФМўжаЖСШЁЪ§Он,МФДцЦїЮФМўгаСНИіЖЫПк,ПЩвджЇГжЭЌЪБНјааСНИіЖСВйзї

- жДаа

жИСюБЛе§ЪНжДааЕФНзЖЮ,дкИУНзЖЮжа,ЫуЪѕТпМЕЅдЊ(ALU)жївЊжДааШ§РрВйзї,жДааЫуЪѕТпМЕЅдЊ,МЦЫуФкДцв§гУЕФгааЇЕижЗ,еыЖдpushКЭpopжИСюЕФдЫЫу

- ЗУДц

ЖдФкДцНјааЖСаДВйзїЕФНзЖЮ

- аДЛи

НЋжДааНсЙћаДЛиЕНМФДцЦїЮФМўжа

- ИќаТ

НЋPCИќаТЮЊЯТвЛЬѕжИСюЕФЕижЗ

subqжИСюЕФИїИіНзЖЮ

ПДПДЩЯУцетЬѕsubqжИСюИїНзЖЮАќКЌЕФФкШн

ШчЩЯЭМЫљЪО

- ШЁжЗНзЖЮ,ИљОнжИСюДњТыРДМЦЫужИСюГЄЖШЁЃ

- выТыНзЖЮ,ИљОнМФДцЦїжИЪОЗћРДЖСШЁМФДцЦїЕФжЕЁЃ

- жДааНзЖЮ,ALU ИљОнвыТыНзЖЮЖСШЁЕНЕФВйзїЪ§вдМАжИСюРДжДааОпЬхЕФдЫЫу,ВЂЩшжУЬѕМўТыМФДцЦїЁЃ

- ЗУДцНзЖЮ,гЩгкМѕЗЈжИСюВЛашвЊЖСаДФкДц,вђДЫИУНзЖЮЮоВйзїЁЃ

- аДЛиНзЖЮ,НЋ ALU ЕФдЫЫуНсЙћаДЛиМФДцЦїЁЃ

- ИќаТНзЖЮ,ИќаТГЬађМЦЪ§ЦїЁЃ

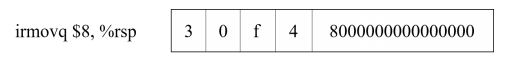

imovqжИСюЕФИїИіНзЖЮ

imovqжИСюЕФИїИіНзЖЮ

irmovq $8,%rsp

ШчЧАЭМЫљЪО

- ШЁжЗНзЖЮ,ИУжИСюМШКЌгаМФДцЦїжИЪОЗћзжНк,вВКЌгаГЃЪ§зжЖЮЁЃ

- выТыНзЖЮ,ИУжИСюВЛашвЊДгМФДцЦїжаЖСШЁЪ§Он,выТыНзЖЮЮоВйзїЁЃ(дДЪЧСЂМДЪ§$8)

- жДааНзЖЮ,ЫфШЛИУжИСюНіНіДЋЫЭЪ§Он,ПДЫЦВЛашвЊ ALU,ЕЋгЩгк ALU ЕФЪфГіЖЫгыМФДцЦїЕФаДШыЖЫЯрСЌ,Ъ§ОнЕФДЋЫЭЛЙЪЧашвЊОЙ§ ALU,вђДЫИУжИСюНЋСЂМДЪ§Мг 0.

- ЗУДцНзЖЮ,ИУжИСюВЛашвЊЖСаДФкДц,вђДЫИУНзЖЮЮоВйзїЁЃ

- аДЛиНзЖЮ,НЋ ALU ЕФдЫЫуНсЙћаДЛиМФДцЦїЁЃ

- ИќаТНзЖЮ,ИќаТГЬађМЦЪ§ЦїЁЃ

rrmovqжИСюЕФИїИіНзЖЮ

ШчЧАЭМЫљЪО

- ШЁжЗНзЖЮ,ИУжИСюМШКЌгаМФДцЦїжИЪОЗћзжНк,вВКЌгаГЃЪ§зжЖЮЁЃ

- выТыНзЖЮ,ДгМФДцЦїжаЖСШЁЪ§ОнЁЃ

- жДааНзЖЮ,ALU ИљОнЦЋвЦСПКЭЛљжЗМФДцЦїРДМЦЫуЗУДцЕижЗЁЃ

- ЗУДцНзЖЮ,НЋМФДцЦї rsp ЕФЪ§жЕаДШыФкДцжаЁЃ

- аДЛиНзЖЮ,гЩгкФкДцЕижЗгЩжДааНзЖЮЕУГіВЂаДШыМФДцЦї,вђДЫаДЛиНзЖЮВЛашвЊНјааВйзїЁЃ

- ИќаТНзЖЮ,ИќаТГЬађМЦЪ§ЦїЁЃ

pushqжИСюЕФИїИіНзЖЮ

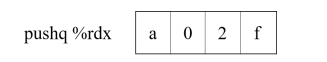

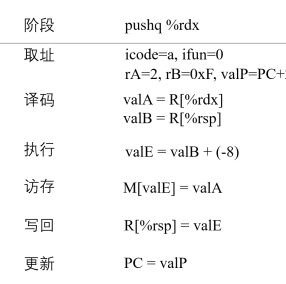

pushq %rdx | a| 0 |2| f|

ЩЯУцетЬѕpushqжИСюИїНзЖЮЕФФкШнШчЯТ

-

ШЁжЗНзЖЮ,ИУжИСюКЌгаМФДцЦїжИЪОЗћ,ВЛКЌГЃЪ§,вђДЫжИСюГЄЖШЮЊ2зжНкЁЃ

-

выТыНзЖЮ,гЩгк pushq жИСювЊНЋМФДцЦї rdx ЕФжЕБЃДцЕНеЛЩЯ,вђДЫИУжИСюВЛНіашвЊЖСШЁМФДцЦї rdx ЕФжЕ,ЛЙашвЊЖСШЁМФДцЦї rsp ЕФжЕЁЃ

-

жДааНзЖЮ,ALU МЦЫуФкДцЕижЗЁЃ

-

ЗУДцНзЖЮ,НЋМФДцЦї rdx ЕФжЕаДЕНеЛЩЯЁЃ

-

аДЛиНзЖЮ,гЩгкМФДцЦї rsp жИЯђЕФФкДцЕижЗЗЂЩњСЫБфЛЏ,вђДЫИќаТМФДцЦїrspЕФжЕЁЃ

-

ИќаТНзЖЮ,ИќаТГЬађМЦЪ§ЦїЁЃ

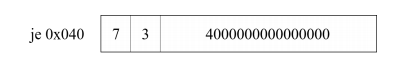

jeжИСюЕФИїИіНзЖЮ

ЩЯЭМНзЖЮФкШнШчЯТ

- ШЁжЗНзЖЮ,ИУжИСюКЌгаГЃЪ§зжЖЮ,ВЛКЌМФДцЦїжИЪОЗћзжНк,вђДЫжИСюГЄЖШЮЊ 9зжНкЁЃ

- выТыНзЖЮ,ВЛашвЊЖСШЁМФДцЦї,ЮоВйзїЁЃ

CondЕФв§Шы

- жДааНзЖЮ,БъКХЮЊCond ЕФгВМўЕЅдЊИљОнЬѕМўТыКЭжИСюЙІФмРДХаЖЯЪЧЗёжДааЬјзЊ,ИУФЃПщВњЩњвЛИіаХКХCnd,ШєCnd=1,дђжДааЬјзЊ;Cnd = 0 дђВЛжДааЬјзЊЁЃ

- ЗУДцНзЖЮ,ЮоВйзїЁЃ

- аДЛиНзЖЮ,ЮоВйзїЁЃ

- ИќаТНзЖЮ,Шє Cnd = 1,НЋ PC ЕФжЕЩшЮЊ0x040;Шє Cnd = 0,дђНЋ PC ЕФжЕЩшЮЊЕБЧАжЕМг 9ЁЃ

4.ДІРэЦїЬхЯЕМмЙЙ||

ШЁЕижЗЕФгВМўЩшМЦ

-

дкШЁжЗНзЖЮжа,ШЁжЗВйзївЛГЬађМЦЪ§ЦїPCЕФжЕзїЮЊЦ№ЪМЕижЗ

-

гЩгкY86-64жИСюМЏжазюГЄЕФжИСюеМ10зжНк,ШЁжЗВйзїУПДЮДгжИСюФкДцЖСШЁ10ИізжНк

-

10зжНкЗжЮЊСНВПЗж

- ЕквЛВПЗжеМ1зжНк

- ЕкЖўВПЗжеМ9зжНк

- Р§ШчБрТыЮЊ 30 |f8 08 00 00 00 00 00 00 00 ЕФжИСю,НЋБЛЗжЮЊ30КЭf008----

SplitгВМўЕЅдЊДІРэЕквЛВПЗж(1Byte)

SplitЕФгВМўЕЅдЊДІРэЕквЛВПЗж,ЫќНЋетИізжНкЗжГЩСНВПЗж,УПВПЗжеМ4ИіБШЬиЮЛ,ЪЙетИізжНкЗжЮЊСНИізжЖЮ,ЗжБ№ЮЊжИСюДњТыКЭжИСюЙІФмЁЃгУicodeКЭifun БэЪО

ИљОнicodeПЩвдШЗЖЈЕБЧАжИСюЕФзДЬЌаХЯЂ,Р§ШчжИСюЕФКЯЗЈад,ШчЙћicodeдк0x0ЕН0xBжЎМф,ФЧУДЫќОЭЪЧвЛЬѕКЯЗЈжИСю,ДЫЭтЭЈЙ§icodeПЩвдХаЖЯЕБЧАжИСюЪЧЗёАќКЌМФДцЦїжИЪОЗћзжНкКЭГЃЪ§зжНк

ЭЈЙ§ЧАУцЫЕЙ§ЕФХаЖЯНсЙћОЭПЩвдМЦЫуГіЕБЧАжИСюЕФГЄЖШ,Р§ШчвЛИіжИСюМШКЌМФДцЦїжИЪОЗћзжНк,гжКЌГЃЪ§зжНк,ФЧЫќЕФГЄЖШОЭЪЧ10зжНк,ШчЙћМШВЛКЌМФДцЦїжИЪОЗћзжНк,гжВЛКЌГЃЪ§зжНк,ЫќЕФГЄЖШОЭЪЧ1зжНк

ПЩвдЭЈЙ§PCжЕМгЩЯЕБЧАЕФжИСюГЄЖШРДМЦЫуФкДцжаЯТвЛЬѕжИСюЕФЕижЗ,гУгкКѓајЕФИќаТНзЖЮ

AlignгВМўЕЅдЊДІРэЕкЖўВПЗж

AlignРДВњЩњМФДцЦїзжЖЮКЭГЃЪ§зжЖЮ,ИУгВМўЕЅдЊЭЈЙ§аХКХneed_regidsРДХаЖЯИУжИСюЪЧЗёАќКЌМФДцЦїжИЪОЗћзжНк

- Шєneed_regids =1,ЫЕУїИУжИСюАќКЌМФДцЦїжИЪОЗћзжНк,ФЧУДЕквЛИізжНкНЋБЛЗжГЩСНИіВПЗж,УПИіВПЗжеМ4Иіbit,ШЛКѓЗжБ№зАШыМФДцЦїжИЪОЗћrAКЭrBжаЁЃ

- Шєneed_regids=0,ЫЕУїИУжИСюВЛАќКЌМФДцЦїжИЪОЗћзжНк,ДЫЪБrA,rBетСНИізжЖЮЩшжУЮЊ0xF

ДЫЭт,ШєИУжИСюКЌгаГЃЪ§,AlignЕЅдЊЛЙНЋВњЩњГЃЪ§зжЖЮ valC

ЕБneed_regids=1ЪБ,valCБЛЩшЮЊжИСюЕФЕк2~9зжНк

ЕБneed_regids=0ЪБ,valCБЛЩшЮЊжИСюЕФ1~8зжНк

выТыНзЖЮЕФгВМўЩшМЦ

-

выТыНзЖЮЕФВйзїЪЧДгМФДцЦїЮФМўжаЖСШЁЪ§Он,дкY86-64ДІРэЦїжаМФДцЦїЮФМўгаСНИіЖСЖЫПк,ЫќжЇГжЭЌЪБНјааСНИіЖСВйзї

СНИіЖСЖЫПкЕФЕижЗЪфШыЮЊ

srcA,srcB

ДгМФДцЦїЮФМўЖСШЁЕФЪ§жЕЭЈЙ§valAКЭvalBЪфГі -

ЖСЖЫПкЕФsrcAКЭsrcBгУгкВњЩњМФДцЦїЕФID

еташвЊМФДцЦїжИЪОЗћrAвдМАrB -

гЩгкФГаЉжИСюР§ШчpushжИСю,ИУжИСюЕФМФДцЦїжИЪОЗћжЛКЌгаФПЕФМФДцЦїЕФID,ЕЋжДаабЙеЛВйзїЕФЪБКђ,ЛЙашвЊЛёЕУеЛЖЅжИеы rspЕФжЕ,вђДЫsrcAКЭsrcBВЛНіашвЊДЋШыrAКЭrB,ЛЙашвЊжИСюДњТы icode

жДааНзЖЮЕФгВМўЩшМЦ

жДааНзЖЮЕФКЫаФВПМўALUИљОнжИСюЙІФм ifunРДХаЖЯЖдЪфШыЕФВйзїЪ§НјааКЮжждЫЫуЁЃУПДЮдЫааЕФЪБКђ,ALUЖМЛсВњЩњШ§ИігыЬѕМўТыЯрЙиЕФаХКХ,Су,ЗћКХ,вчГі

ЮвУЧжЛЯЃЭћALUдкжДааЫуЪѕТпМжИСюЪБВХЩшжУЬѕМўТыЁЃЖјМЦЫуФкДцв§гУЕижЗвдМАеЛВйзїЕФЪБКђВЛвЊЩшжУЬѕМўТыЁЃвђДЫЮвУЧЪЙгУSet_CCаХКХИљОнжИСюДњТыicodeРДПижЦЪЧЗёашвЊЩшжУЬѕМўТы

ДЫЭт,ЮвУЧЪЙгУУћЮЊCondЕФгВМўЕЅдЊРДПижЦЬјзЊВйзїЁЃCondЛсИљОнжИСюЙІФмКЭЬѕМўТыМФДцЦїРДВњЩњCndаХКХ

ЖдгкЬјзЊжИСю,ШчЙћCnd=1 ЬјзЊ

Cnd=0ВЛЬјзЊ

ЗУЮЪНзЖЮЕФгВМўЩшМЦ

ЫФИіПижЦПщ

- ЖСПижЦПщ

гУгкНјааЖСВйзї - аДПижЦПщ

гУгкНјаааДВйзї - ФкДцЕижЗПижЦПщ

гУгкВњЩњФкДцЕижЗ - Ъ§ОнЪфШыПижЦПщ

гУгкЪфШыЪ§Он

ЗУДцНзЖЮЕФзюКѓЛЙНЋИљОнicodeХаЖЯГіжИСюЕФгааЇадвдМАФкДцзДПіВњЩњinstr_valid КЭimem_error аХКХРДМЦЫузДЬЌТы

аДЛиНзЖЮЕФгВМўЩшМЦ

ЪзЯШЮЊМФДцЦїЮФМўЬэМгMКЭE,етСНИіаДЖЫПк,ЖдгІЕФЕижЗЪфШыЮЊdstEКЭdstM,ашвЊзЂвтЕФЪЧ,ЕБжДааЬѕМўДЋЫЭжИСю cmovЪБ,аДШыВйзїЛЙвЊИљОнжДааНзЖЮМЦЫуГіЕФcndаХКХ,ЕБЬѕМўВЛТњзуЪБКђ,вдФПЕФМФДцЦїЩшжУЮЊ0xFРДНћжЙаДШыМФДцЦїЮФМў

ИќаТНзЖЮЕФгВМўЩшМЦ

ИќаТНзЖЮPCЕФжЕгавдЯТШ§жжЧщПі

- call PC=callжИСюЕФГЃЪ§зжЖЮ

- ret PC=retдкЗУДцНзЖЮДгФкДцжаЖСШЁЕФЗЕЛиЕижЗ

- jxx

ТњзуЬјзЊЬѕМўcnd=1,аТЕФPCЕФжЕЕШгкЬјзЊжИСюЕФГЃЪ§зжЖЮ

ВЛТњзуЬјзЊЬѕМў,cnd=0,аТЕФPCжЕЕШгкЕБЧАPCжЕМгЩЯЕБЧАжИСюГЄЖШ - Ъ§ОнЪфШыПижЦПщ,гУгкЪфШыЪ§Он