ЮФеТФПТМ

вЛЁЂAMBAзмЯпИХЪі

ДІРэЦїКЭЦфЫћЕФmaster/slaveЩшБИЖМЪЧПЩвдЬцЛЛЕФ

AHB(Advanced High-performance Bus)ИпМЖИпадФмзмЯпЁЃ

APB(Advanced Peripheral Bus)ИпМЖЭтЮЇзмЯп

ИїздЕФЬиЕу:

- AHBжївЊЪЧеыЖдИпаЇТЪЁЂИпЦЕПэМАПьЫйЯЕЭГФЃПщЫљЩшМЦЕФзмЯп,ЫќПЩвдСЌНгШчЮЂДІРэЦїЁЂаОЦЌЩЯЛђаОЦЌЭтЕФФкДцФЃПщКЭDMAЕШИпаЇТЪФЃПщЁЃ

- APBжївЊгУдкЕЭЫйЧвЕЭЙІТЪЕФЭтЮЇ,ПЩеыЖдЭтЮЇЩшБИзїЙІТЪЯћКФМАИДдгНгПкЕФзюМбЛЏЁЃAPBдкAHBКЭЕЭДјПэЕФЭтЮЇЩшБИжЎМфЬсЙЉСЫЭЈаХЕФЧХСК,ЫљвдAPBЪЧAHBЕФЖўМЖЭиеЙзмЯпЁЃ

ЖўЁЂ AHBавщ

2.1 AHBзщГЩ

Master:ФмЙЛЗЂЦ№ЖСаДВйзї,ЬсЙЉЕижЗКЭПижЦаХКХ,ЭЌвЛЪБМфжЛга1ИіMasterЛсБЛМЄЛю(ЖРеМад)ЁЃ(CPUЁЂDMAЁЂDSPЁЂLCDCЁ)

Slave:дкИјЖЈЕФЕижЗЗЖЮЇФкЖдЖСаДВйзїзїЯьгІ,ЭЈЙ§ЕижЗгГЩфРДбЁдёЪЙгУФФИіДгЩшБИ,ВЂЖдMasterЗЕЛиГЩЙІЁЂЪЇАмЛђепЕШД§зДЬЌЁЃ

Arbiter:ИКд№БЃжЄзмЯпЩЯвЛДЮжЛга1ИіMasterдкЙЄзїЁЃжйВУавщЪЧЙцЖЈЕФ,ЕЋЪЧжйВУЫуЗЈПЩвдИљОнгІгУОіЖЈЁЃ

Decoder:ИКд№ЖдЕижЗНјааНтТы,ВЂЬсЙЉЦЌбЁаХКХЕНИїSlaveЁЃУПИіAHBЖМашвЊ1ИіжйВУЦїКЭ1ИіжабыНтТыЦїЁЃ

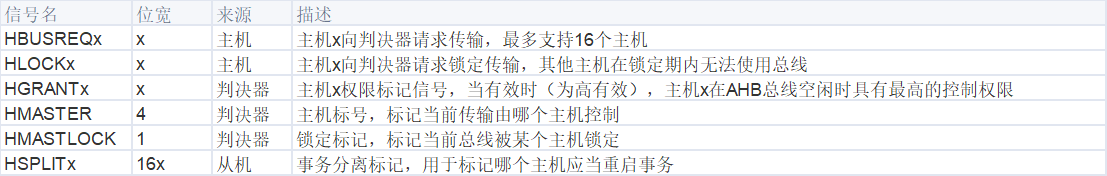

- ИпЫйзмЯп,ИпадФм

- 2МЖСїЫЎЯпВйзїСїЫЎЯп

- ПЩжЇГжЖрИізмЯпmasterЩшБИ(зюЖр16Иі)

- жЇГжburstДЋЪф,ЧАКѓашвЊгадМЪј

- змЯпДјПэ:8ЁЂ16ЁЂ32ЁЂ64ЁЂ128bits

- ЩЯЩ§биДЅЗЂВйзї,ЕчШнГфЕчБШНЯПь,ЕЋЪЧЗХЕчБШНЯТ§

- ЖдгквЛИіаТЩшМЦНЈвщЪЙгУAHB

2.2 AHBЛљБОаХКХ

2.3 AHBДЋЪф

AHBДЋЪфЗжЮЊвдЯТМИИіВПЗж:

- жїЛњЛёШЁзмЯпЪЙгУШЈ:жїЛњЯђХаОіЦїЗЂЫЭзмЯпЧыЧѓаХКХ,ХаОіЦїЗЂЫЭгІД№КѓжїЛњПЩвдПЊЪМДЋЪф

- Ъ§ОнДЋЪф:жїЛњЯђДгЛњДЋЪфЪ§Он,ЗжЮЊвдЯТСНИіВПЗж:

- ЗЂЫЭЕижЗКЭПижЦаХКХ:АќРЈЕижЗ,ЮЛПэ,ЭЛЗЂРраЭ(діСПЭЛЗЂКЭЛиОэЭЛЗЂ)ЕШПижЦаХКХ,НівЛИіЪБжгжмЦк

- Ъ§ОнДЋЪф:НјааЪ§ОнНЛЛЛ,вЛИіЛђЖрИіЪБжгжмЦк,жївЊгЩHREADYаХКХОіЖЈМИИіcycle

- СїЫЎЯпДЋЫЭ:ЯШЪЧЕижЗжмЦк,ШЛКѓЪЧЪ§ОнжмЦк

- ДгЛњгІД№:ДгЛњЭЈЙ§HRESPКЭHREADYБъМЧЭъГЩзДЬЌ,ЖдгкHRESP,гавдЯТзДЬЌ:

- OKAY:БъМЧДЋЪфЭъГЩ,ЕБHRESPЮЊИУзДЬЌЧвHREADYРИпЪБ,ДЋЪфЭъГЩ

- ERROR:БъМЧДЋЪфГіДэ

- RETRYКЭSPLIT:БъМЧДЋЪфЮДЭъГЩ,жїЩшБИШдашвЊеМгУзмЯп

ЙигкЭЛЗЂДЋЪф,РэТлЩЯНјааЭЛЗЂДЋЪфЕФжїЩшБИгІЕБвЛжБеМОнзмЯп,ЕЋЪЧЮЊСЫЫѕЖЬЕШД§ЪБМф,AHBдЪаэДђЖЯЭЛЗЂДЋЪф,ВЂдквЛЖЮЪБМфКѓжиЦєИУЭЛЗЂДЋЪф

2.3.1 AHBвЛДЮЮоашЕШД§зДЬЌЕФМђЕЅДЋЪф

ЮоЕШД§ДЋЪфЯТ,вЛИіДЋЪфгыШ§ИіЪБжгбигаЙи:

- ЕквЛИіЪБжгби:ЕквЛИіЪБжгбиКѓ,жїЛњНЋЕижЗаХЯЂКЭПижЦаХЯЂЗЂЫЭЕНзмЯпЩЯ

- ЕкЖўИіЪБжгби:ЕкЖўИіЪБжгбиЩЯ,ДгЛњВЩбљжїЛњЕФЕижЗаХЯЂКЭПижЦаХЯЂЁЃЕкЖўИіЪБжгбиКѓ,ДгЛњНЋЯьгІаХКХКЭЪ§ОнЗЂЫЭЕНзмЯпЩЯ

- ЕкШ§ИіЪБжгби:жїЛњВЩбљДгЛњЯьгІаХКХКЭЪ§Он,ДЋЪфЭъГЩ

ШчЙћHREADYЮДНгЪеЕНЪ§ОнФЧУДОЭашвЊПДЯТвЛИіВПЗж

2.3.2 AHBашвЊСНИіЕШД§жмЦкЕФМђЕЅДЋЪф

гаЕШД§ДЋЪфЯТ,Ъ§ОнДЋЪфНзЖЮПЩвдРЉеЙ,МДдкHREADYРИпжЎЧА,Ъ§ОнДЋЪфНзЖЮВЛНсЪјЁЃвЊЧѓаДЪ§ОндкHREADYРИпЧАБЃГжЮШЖЈ,жїЛњдкHREADYРИпКѓВЩбљЖСЪ§ОнЁЃетРяВЛФмЕШД§ГЌЙ§16ИіcycleЁЃ

2.3.3 AHBашвЊСНИіЕШД§жмЦкЕФМђЕЅДЋЪф

AHBзмЯпжЇГжСїЫЎЯпДЋЪф,МДНЋДЋЪфЗжЮЊЕижЗ-Ъ§ОнСНИіВПЗжСїЫЎНјаа,БОДЮДЋЪфЕФЕижЗБиШЛдкЩЯвЛДЮЕижЗжЎКѓ,БОДЮДЋЪфЕФЪ§ОнБиЖЈНєИњдкБОДЮДЋЪфЕижЗжЎКѓЁЃвђДЫ,ЕБЩЯвЛДЮЕФЪ§ОнДЋЪфзшШћЕМжТДЋЪфжмЦкдіМгЪБ,ЯТвЛДЋЪфЕФЕижЗжмЦквВЛсЯргІЕФБфГЄ:

- AКЭConctrol(A)ЮЊЕквЛДЮДЋЪфЕФЕижЗКЭПижЦаХКХ

- WDATA(A)КЭRDATA(A)ЪЧЕквЛДЮДЋЪфЕФЪ§Он,ИУДЋЪфЮЊЕЅЪБжгМДЮозшШћЕФДЋЪф,ЭЌЪБЗЂЫЭЕФЛЙгаЯТвЛДЮДЋЪфЕФЕижЗКЭПижЦаХКХ:A2КЭC2

- ЕкЖўДЮДЋЪфЮЊЖржмЦкДЋЪф,вђДЫWDATA(B)КЭRDATA(B)еМОнЖрИіЪБжгжмЦк,ЖдгІЕФ,ЭЌЪБЗЂЫЭЕФЕкШ§ДЮДЋЪфЕижЗКЭПижЦаХA3КЭC3вВБЛбгГйЯрЭЌЕФЪБжгжмЦкЪ§

- WDATA?КЭRDATA?ЪЧЕквЛДЮДЋЪфЕФЪ§Он

2.3.4 Burst transfer

гаСНжжburst transfer

- діСПburst:ДЋЪфЙ§ГЬжаДЋЪфЕижЗЕндіЁЃЯТвЛДЮДЋЪфЕФЕижЗЪЧЩЯвЛДЮЕижЗМгЩЯвЛИідіСП

- ЛиЛЗburst:тЇЗЂЕФЕижЗЗЖЮЇБЛЯожЦдквЛИіЙЬЖЈЗЖЮЇжЎФк,ДЋЪфЕижЗЕнді,ШєЪЧГЌГідђЛиЕНЕижЗЗЖЮЇЕФПЊЪМЕФЕижЗЁЃР§ШчДг0x34НјаадіСПЮЊ4,ЗЖЮЇЮЊ16ЕФЛиЛЗburst,ЕижЗЫГађЮЊ0x34ЁЂ0x38ЁЂ0x3c,0x30

2.14 Dummy Master/Default Master

Dummy Master,

- ЕБЫљгаЕФmaster SPLITЪБgranted,ЖМВЛеМгУЪБ

- жЛдкIDLE cylesжаВњЩњ

- ЕБЫјЖЈmasterЕУЕНSPLIT response Ъкгш

- зїЮЊЕижЗ/ПижЦЕФвЛВПЗжЪЕЯжЖрТЗИДгУЦї

Default Master,CPU

- ЕБжїЛњВЛашвЊзмЯпЪБЪкгш

- ЭЈГЃжїЛњзюПЩФмашвЊзмЯп

- дкУЛгаЧыЧѓзмЯпЪБВњЩњПеЯажмЦк

- БмУтзюаЁСНИіЪБжгжмЦк

2.5 ДЋЪфРраЭ

ДЋЪфРраЭЪЙгУЖЫПкHTRANSБъМЧ,гавдЯТШЁжЕ:

- IDLE(00):БъжОжїЛњеМгаAHBзмЯп,ЕЋЪЧУЛгаЪ§ОнДЋЪфЗЂЩњЁЃДгЛњашвЊЪЙгУOKAYзДЬЌЛигІИУРраЭ

- BUSY(01):БъжОжїЛњеМгаAHBзмЯпВЂдкНјаатЇЗЂДЋЪф,ЕЋЯТвЛИіДЋЪфВЛФмСЂПЬЗЂЩњЁЃДгЛњашвЊЪЙгУOKAYзДЬЌЛигІ

- NONSEQ(10):БъжОжїЛњЕБЧАЗЂЫЭЕФЕижЗКЭПижЦаХКХгыЩЯвЛДЮДЋЪфЮоЙи(ЕЅДЮДЋЪфОЭЪЧИУзДЬЌ)

- SEQ(11):БъМЧжїЛњДІгктЇЗЂДЋЪфЕФжаМфВПЗж,МДЕБЧАЗЂЫЭЕФЕижЗКЭПижЦаХКХгыЩЯвЛДЮЕижЗКЭПижЦаХКХгаЙи

- ЕквЛДЮДЋЪф,ПЊЦєвЛДЮburstДЋЪф,вђДЫИУЕижЗгыЩЯвЛДЮДЋЪфЮоЙи,ЪЙгУРраЭNONSEQ

- ЕкЖўДЮДЋЪф,ЮоЗЈСЂПЬНјааДЋЪф,вђДЫЪЙгУBUSYБъМЧбгГйвЛИіжмЦк,бгГйКѓПЩвдНјааДЋЪф,ЧвДІгкburstДЋЪфжа,вђДЫЕижЗгыЩЯвЛДЮЕижЗгаЙи,ЪЙгУSEQБъМЧ

- жЎКѓОљЮЊburstДЋЪф,ОљЪЙгУSEQРраЭ

2.6 ПижЦаХКХ

- HWRITE

- ИпЕчЦН:аД

- ЕЭЕчЦН:ЖС

- HSIZE[2:0]

- HPROTЬсЙЉЖдДЋЪфавщЕФЖюЭтЫЕУї,ШчЯТЫљЪО:

- HPROT[3]:0-Cacheable;1-Not cacheable

- HPROT[2]:0-Bufferable;1-Not bufferable

- HPROT[1]:0-Privileged access;1-User access

- HPROT[0]:0-Opcode fetch;1-Data access

Ш§ЁЂ APBавщ

- ЕЭЫйзмЯп,ЕЭЙІКФ

- НгПкМђЕЅ

- дкbridgeжаЫјДцЕижЗаХКХКЭПижЦаХКХ

- ЪЪКЯЖржжЩшБИ

- AHB2APB BridgeПЩвдЫјДцЫљгаЕФЕижЗЁЂЪ§ОнКЭПижЦаХКХ

- НјааЖўМЖвыТыРДВњЩњAPBДгЩшБИбЁдёаХКХ

- APBзмЯпЩЯЕФЫљгаЦфЫћФЃПщЖМЪЧAPBДгЩшБИ,жЛгаslaveУЛгаmasterЁЃ

3.1 APBаХКХСаБэ

| УћГЦ | УшЪі |

|---|---|

| PCLK | PCLKЕФЩЯЩ§бигУзїAPBДЋЪфЕФЪБЛљ |

| PRESETn | APBзмЯпИДЮЛаХКХЮЊЕЭгааЇЧвЭЈГЃНЋИУаХКХжБНгСЌНгЕНЯЕЭГзмЯпИДЮЛаХКХ |

| PADDR[31:0] | APBЕижЗзмЯп,ПЩИпДя32ЮЛПэЖШВЂгЩЭтЩшзмЯпЧХНгЕЅдЊЧ§ЖЏ |

| PSELx | РДздЖўМЖвыТыЦїЕФаХКХ,ДгЭтЩшзмЯпЧХНгЕЅдЊФкЕНУПИіЭтЩшзмЯпДгЛњxЁЃИУаХКХБэЪОДгЛњЩшБИБЛбЁжаВЂЧввЊЧѓНјаавЛДЮЪ§ОнДЋЪфЁЃУПИізмЯпДгЛњЖМгавЛИіPSELxаХКХ |

| PENABLE | етИібЁЭЈаХКХгУРДИјЭтЩшзмЯпЩЯЕФЫљгаЗУЮЪЬсЙЉЪБМфЁЃЪЙФмаХКХгУРДБэЪОвЛДЮAPBДЋЪфЕФЕкЖўИіжмЦкЁЃPENABLEЕФЩЯЩ§биГіЯждкAPBДЋЪфЕФжаМф |

| PWRITE | ИУаХКХЮЊИпБэЪОвЛДЮAPBаДЗУЮЪЖјЮЊЕЭБэЪОвЛДЮЖСЗУЮЪ |

| PRDATA | ЖСЪ§ОнзмЯпгЩБЛбЁжаЕФДгЛњдкЖСжмЦк(PWRITEЕЭ)ЦкМфЧ§ЖЏ,ЖСЪ§ОнзмЯпПЩДяЕН32ЮЛПэЖШ |

| PWDATA | аДЪ§ОнзмЯпгЩБЛбЁжаЕФДгЛњдкЖСжмЦк(PWRITEИп)ЦкМфЧ§ЖЏ,аДЪ§ОнзмЯпПЩДяЕН32ЮЛПэЖШ |

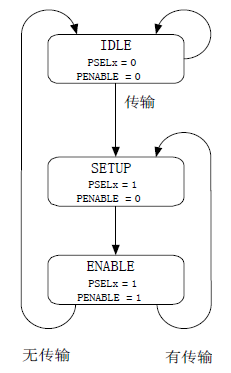

3.2 APBзДЬЌзЊвЦ

- IDLE:ЭтЩшзмЯпЕФФЌШЯзДЬЌЁЃ

- SETUP:ЕБгаДЋЪфвЊЧѓЪБзмЯпзЊвЦЕНSETUP зДЬЌ,етЪБЖдгІЕФбЁдёаХКХ,PSELxБЛЖЯбдЁЃзмЯпНідк SETUP зДЬЌБЃГжвЛИіЪБжгжмЦкВЂНЋзмЪЧдкЯТвЛИіЪБжгЕФЩЯЩ§бивЦЖЏЕН ENABLE зДЬЌЁЃ

- ENABLE ЪЙФмаХКХPENABLE дкENABLE зДЬЌжаБЛЖЯбдЁЃЕижЗЁЂаДКЭбЁдёаХКХЖМдкДг SETUP ЕНENABLE зДЬЌЕФзЊБфЙ§ГЬжаБЃГжЮШЖЈЁЃ

ENABLEзДЬЌвВНіГжајвЛИіжмЦкВЂЧвдкетИізДЬЌжЎКѓШчЙћУЛгаНјвЛВНЕФДЋЪфвЊЧѓзмЯпНЋЗЕЛи IDLE зДЬЌЁЃСэЭт,ШчЙћНєИњзХСэвЛИіДЋЪфФЧУДзмЯпвЦЖЏЕН SETUP зДЬЌЁЃЕижЗЁЂаДКЭбЁдёаХКХдкДгENABLE ЕНSETUP зДЬЌЕФзЊБфЦкМфгааЁЬјБфвВЪЧПЩвдНгЪмЕФЁЃ

3.3 APBаДДЋЪф

аДДЋЪфПЊЪМгкЕижЗЁЂаДЪ§ОнЁЂаДаХКХКЭбЁдёаХКХдкЪБжгЩЯЩ§бижЎКѓЕФШЋВПИФБфЁЃ

ДЋЪфЕФЕквЛИіЪБжгБЛГЦзїSETUP жмЦкЁЃдкЯТвЛИіЪБжгБпбиЪЙФмаХКХPENABLE ЩњаЇ,етБэЪОEANBLE жмЦке§дкНјааЁЃЕижЗЁЂЪ§ОнКЭПижЦаХКХШЋЖМдкећИіENABLE жмЦкБЃГжгааЇЁЃДЋЪфдкетИіжмЦкНсЪјЪБЭъГЩЁЃЪЙФмаХКХ PENABLE,НЋдкДЋЪфНсЪјЪБЪЇаЇЁЃбЁдёаХКХвВНЋБфГЩЕЭЕчЦН,Г§ЗЧЕБЧАДЋЪфжЎКѓНєИњзХСэвЛИіЕНИУЭтЩшЕФДЋЪфЁЃЮЊСЫНЕЕЭЙІТЪЯћКФЕижЗаХКХКЭаДаХКХНЋдкДЋЪфжЎКѓВЛдйИФБф,жБЕНЯТвЛИіДЋЪфЗЂЩњЮЊжЙЁЃавщНівЊЧѓдкЪЙФмаХКХЩЯгавЛИіЙцдђЕФзЊБф(ЬјБф)ЁЃдкБГППБГДЋЪфЧщПіЯТбЁдёКЭаДаХКХПЩФмгааЁЬјБфЁЃ

3.3 APBЖСДЋЪф

ЕижЗЁЂаДЁЂбЁдёКЭбЁЭЈаХКХЕФЪБађЖМКЭаДДЋЪфвЛбљЁЃдкЖСДЋЪфЕФЧщПіЯТ,ДгЛњБиаыдкEANBLE жмЦкЬсЙЉЪ§ОнЁЃЪ§ОндкENABLE жмЦкФЉЮВЕФЪБжгЩЯЩ§биБЛВЩбљЁЃ

3.4 APB bridge