控制信号发生器

1.功能

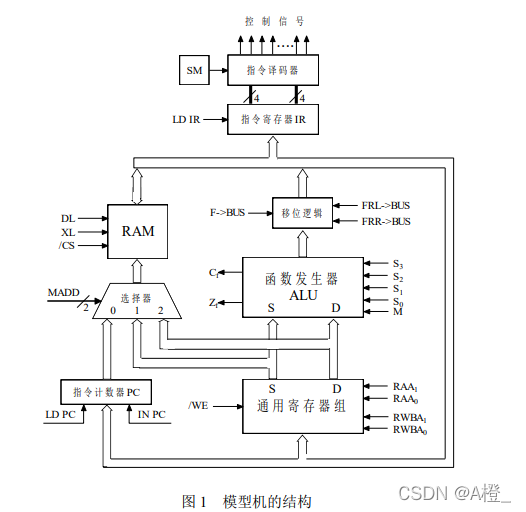

????????控制信号发生器的功能为根据特定的指令,发出对应的控制信号,使各组件配合完成指令的执行。

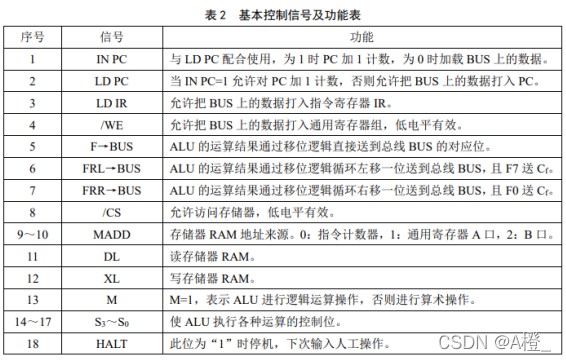

2.控制信号

????????控制信号如下表:

????????

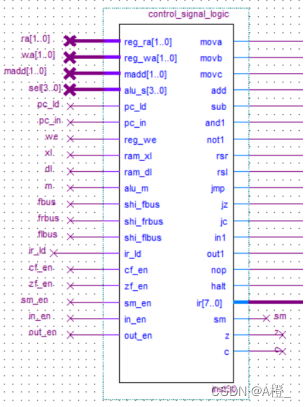

3.端口设计

????????共20个输入端口,除16个指令信号外,还有z,c两个状态信号(通过状态寄存器传入),ir为指令编码(这里仍然需要指令编码是因为ALU的sel控制信号是指令编码前4位),sm信号的作用是控制指令执行的时间。

??????? 共19个输出端口,18个控制信号如上表,多出的一个sm_en信号是执行HALT指令所需要的。sm控制指令执行的周期,sm=1时执行指令,sm=0时读取指令,当sm_en=1时,sm在0和1之间翻转,重复读取指令执行指令的过程。HALT指令执行后,不再执行之后的指令,因此需要使sm_en=0,让sm不再翻转,保持为1,即一直执行HALT指令。

4.各指令与对应的控制信号情况

??????? 只需要关注控制信号在哪些指令有效即可,无效不需要关注,使用always语句赋值,考虑信号为1的情况。

??????? 寄存器组共有三个寄存器,分别为A,B,C。

MOVA

??????? MOVA指令的功能为将源寄存器的数据移送至目的寄存器,关注通用寄存器组,ALU和移位逻辑构成的通路。

??????? 通用寄存器组:需要写入数据,we=0(低电平有效)

??????? ALU:不需要运算,m,cf_en,zf_en都无效为0

??????? 移位逻辑:不需要移位,flbus,frbus无效为0,数据直接通过,fbus=1

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:不需要读写,DL,XL都无效为0

??????? 指令计数器无操作,选择器值不影响指令执行

MOVB

??????? MOVB指令的功能为将源寄存器的数据移送至RAM,数据在RAM中的地址为寄存器C中的数据。

??????? 通用寄存器组:不需要写入数据,we无效为1(低电平有效)

??????? ALU:不需要运算,m,cf_en,zf_en都无效为0

??????? 移位逻辑:不需要移位,flbus,frbus无效为0,数据直接通过,fbus=1

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:需要写,DL无效为0,XL=1

??????? 指令计数器无操作

??????? 选择器要接收寄存器C的数据作为一个存储器地址,从总线上取得的寄存器数据要存放在这个地址,因此MADD=10,接收D口传输的数据

MOVC

??????? MOVC指令的功能为将RAM的数据移送至目的寄存器,数据在RAM中的地址为寄存器C中的数据。

??????? 通用寄存器组:需要写入数据,we=0(低电平有效)

??????? ALU:不需要运算,m,cf_en,zf_en都无效为0

??????? 移位逻辑:不需要移位,也不需要且不能有数据通过(总线上只能有RAM传输的数据,不能冲突),flbus,frbus,fbus无效为0

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:需要读,XL无效为0,DL=1

??????? 指令计数器无操作

??????? 选择器要接收寄存器C的数据作为一个存储器地址,要读出RAM这个地址的数据传给寄存器,因此MADD=01,接收S口传输的数据

ADD

????????通用寄存器组:需要写入数据,we=0(低电平有效)

??????? ALU:运算,m=1,cf_en=1,zf_en=1

??????? 移位逻辑:不需要移位,flbus,frbus,无效为0,fbus=1

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:不需要读写,XL,DL无效为0

??????? 指令计数器无操作,选择器值不影响指令执行

SUB

????????通用寄存器组:需要写入数据,we=0(低电平有效)

??????? ALU:运算,m=1,cf_en=1,zf_en=1

??????? 移位逻辑:不需要移位,flbus,frbus,无效为0,fbus=1

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:不需要读写,XL,DL无效为0

??????? 指令计数器无操作,选择器值不影响指令执行

AND

????????通用寄存器组:需要写入数据,we=0(低电平有效)

??????? ALU:运算,m=1,cf_en无效为0,zf_en无效为0

??????? 移位逻辑:不需要移位,flbus,frbus,无效为0,fbus=1

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:不需要读写,XL,DL无效为0

??????? 指令计数器无操作,选择器值不影响指令执行

NOT

????????通用寄存器组:需要写入数据,we=0(低电平有效)

??????? ALU:运算,m=1,cf_en无效为0,zf_en无效为0

??????? 移位逻辑:不需要移位,flbus,frbus,无效为0,fbus=1

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:不需要读写,XL,DL无效为0

??????? 指令计数器无操作,选择器值不影响指令执行

RSR

????????通用寄存器组:需要写入数据,we=0(低电平有效)

??????? ALU:运算,m=1,cf_en=1,zf_en无效为0

??????? 移位逻辑:需要移位,frbus=1,fbus,flbus无效为0

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:不需要读写,XL,DL无效为0

??????? 指令计数器无操作,选择器值不影响指令执行

RSL

????????通用寄存器组:需要写入数据,we=0(低电平有效)

??????? ALU:运算,m=1,cf_en=1,zf_en无效为0

??????? 移位逻辑:需要移位,flbus=1,fbus,frbus无效为0

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:不需要读写,XL,DL无效为0

??????? 指令计数器无操作,选择器值不影响指令执行

JMP

????????通用寄存器组:不需要写入数据,we=1(低电平有效)

??????? ALU:不运算,m,cf_en,zf_en无效为0

??????? 移位逻辑:不需要移位,flbus,fbus,frbus无效为0

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:需要读,XL无效为0,DL=1

??????? 指令计数器:读取总线上的指令地址,pc_ld=1,pc_in无效为0

??????? 选择器选择PC的数据:MADD=00

JZ/JC(Z=1/C=1时如下执行,否则不执行)

????????通用寄存器组:不需要写入数据,we=1(低电平有效)

??????? ALU:不运算,m,cf_en,zf_en无效为0

??????? 移位逻辑:不需要移位,flbus,fbus,frbus无效为0

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:需要读,XL无效为0,DL=1

??????? 指令计数器:读取总线上的指令地址,pc_ld=1,pc_in无效为0

??????? 选择器选择PC的数据:MADD=00

IN

????????通用寄存器组:需要写入数据,we=0(低电平有效)

??????? ALU:不运算,m,cf_en,zf_en无效为0

??????? 移位逻辑:不需要移位,flbus,fbus,frbus无效为0

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:不需要读写,XL,DL无效为0

??????? 指令计数器无操作,选择器值不影响指令执行

??????? in_en=1

OUT

????????通用寄存器组:不需要写入数据,we=1(低电平有效)

??????? ALU:不运算,m,cf_en,zf_en无效为0

??????? 移位逻辑:不需要移位,flbus,frbus无效为0,fbus=1

??????? 指令寄存器:不需要读指令,ir_ld无效为0

??????? RAM:不需要读写,XL,DL无效为0

??????? 指令计数器无操作,选择器值不影响指令执行

??????? out_en=1

NOP:暂停指令执行,无控制信号

HALT:停止sm翻转,sm_en=0

读取指令:sm=0时读取指令,pc_in=1,ir_ld=1

5.过程赋值代码

??????? 整理每个控制信号有效的指令,进行赋值

...

always@(mova,movb,movc,add,sub,and1,not1,rsr,rsl,jmp,jz,z,jc,c,in1,out1,nop,halt,sm,ir)

begin

sm_en<=!halt;

//ALU

alu_m<=add||sub||and1||not1||rsr||rsl||out1;

cf_en<=add||sub||rsr||rsl;

zf_en<=add||sub;

alu_s[3:0]<=ir[7:4];

//移位逻辑

shi_fbus<=mova||movb||add||sub||and1||not1||out1;

shi_frbus<=rsr;

shi_flbus<=rsl;

//RAM

ram_dl<=movc||jmp||(jz&&z)||(jc&&c)||!sm;

ram_xl<=movb;

//指令寄存器

ir_ld<=!sm;

//寄存器组

reg_we<=!(mova||movc||add||sub||and1||not1||rsl||rsr||in1)||!sm;

reg_wa<=ir[3:2];

reg_ra[1:0]<=ir[1:0];

//计数器PC

pc_ld<=jmp||(jz&&z)||(jc&&c);

pc_in<=(jz&&!z)||(jc&&!c)||!sm;

//选择器MADD

if(movb&&sm) madd<=2'b10;

else if(movc&&sm) madd<=2'b01;

else if(!sm) madd<=2'b00;

else madd<=2'b00;

//输入输出设备

in_en<=in1;

out_en<=out1;

end

...