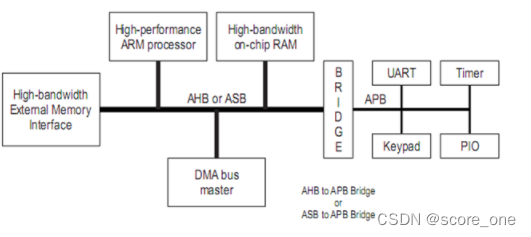

����AMBA����ϵͳ:(��Ҫ��AHB��APB)

�����Ҫ���IJ���:master,slaver,arbiter,decoder

master��BUS���ز���,����CPU

slaver��BUS��������,����ROM

arbiter��BUS�ٲ���,�����ж϶�����ص����ȼ�

decoder�ǵ�ַ������,�����жϿ����ĸ�����

AHB�������ڸ�����,��ʱ�ӹ���Ƶ��ģ�顣AHB��AMBA�ܹ���Ϊϵͳ�ĸ������������˻�ʯ���á�AHBΪ�����ܴ�����,Ƭ���ڴ�,Ƭ���ڴ��ṩ�ӿ�,ͬʱ�Ž��������衣������,���ݴ���,��������������,ͻ����������,�ֲ����䡣AHB����Э����AMBA����һ������Э��,֧�ֶ��ָ�������������������

AHB_lite�Ǽ��AHB,ֻ֧��һ������,���Բ���Ҫarbiter

����APBֻ��slaver

Bridge����AHB��APB��ת��

ʵ����:(��Դ��CPU�������š�)

���岿��:

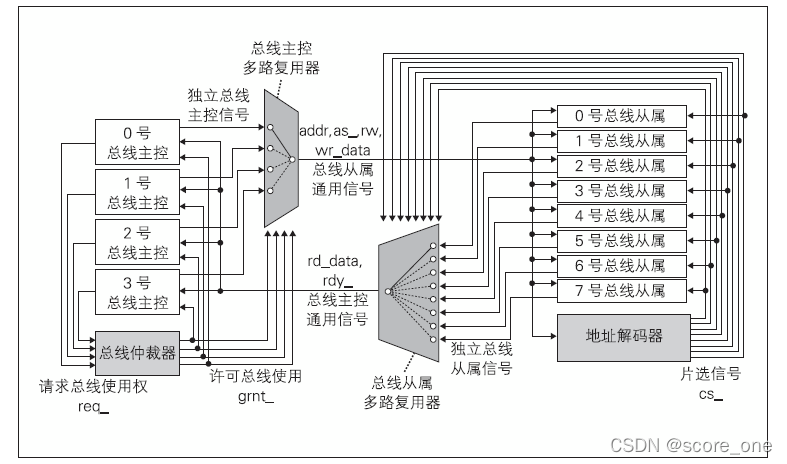

4������,1���ٲ���,1����ַ������,8������

**

�˿ڶ���:

**

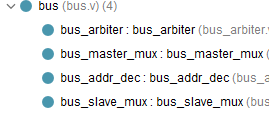

Part1. BUS����

1.bus_arbiter --��ѯ����,��������˳��

input wire clk,

input wire reset,

input wire m0_req_,

input wire m1_req_,

input wire m2_req_,

input wire m3_req_,

output reg m0_grnt_,

output reg m1_grnt_,

output reg m2_grnt_,

output reg m3_grnt_

2.bus_master_mux --�������ض�·������

input wire [`WordAddrBus] m0_addr, // Address--30

input wire m0_as_, // Address strobe

input wire m0_rw, // Read/Write

input wire [`WordDataBus] m0_wr_data, // Write data--32

input wire m0_grnt_, // Bus grant

// Bus master 1

input wire [`WordAddrBus] m1_addr, // Address

input wire m1_as_, // Address strobe

input wire m1_rw, // Read/Write

input wire [`WordDataBus] m1_wr_data, // Write data

input wire m1_grnt_, // Bus grant

// Bus master 2

input wire [`WordAddrBus] m2_addr, // Address

input wire m2_as_, // Address strobe

input wire m2_rw, // Read/Write

input wire [`WordDataBus] m2_wr_data, // Write data

input wire m2_grnt_, // Bus grant

// Bus master 3

input wire [`WordAddrBus] m3_addr, // Address

input wire m3_as_, // Address strobe

input wire m3_rw, // Read/Write

input wire [`WordDataBus] m3_wr_data, // Write data

input wire m3_grnt_, // Bus grant

/********** Bus slave common signal **********/

output reg [`WordAddrBus] s_addr, // Address --30

output reg s_as_, // Address strobe

output reg s_rw, // Read/Write

output reg [`WordDataBus] s_wr_data // Write data --32

3.bus_addr_dec ---��ַ������

input wire [`WordAddrBus] s_addr, // Address

/********** Chip select **********/

output reg s0_cs_, // Bus slave 0

output reg s1_cs_, // Bus slave 1

output reg s2_cs_, // Bus slave 2

output reg s3_cs_, // Bus slave 3

output reg s4_cs_, // Bus slave 4

output reg s5_cs_, // Bus slave 5

output reg s6_cs_, // Bus slave 6

output reg s7_cs_ // Bus slave 7

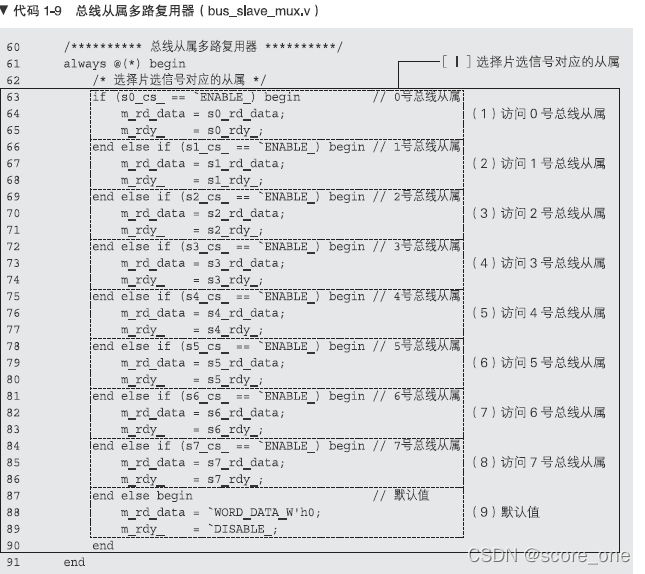

4.bus_slave_mux ---���ߴ�����·������

/********** Multiplexer **********/

input wire s0_cs_, // Bus slave 0

input wire s1_cs_, // Bus slave 1

input wire s2_cs_, // Bus slave 2

input wire s3_cs_, // Bus slave 3

input wire s4_cs_, // Bus slave 4

input wire s5_cs_, // Bus slave 5

input wire s6_cs_, // Bus slave 6

input wire s7_cs_, // Bus slave 7

/********** Bus slave signals **********/

// Bus slave 0

input wire [`WordDataBus] s0_rd_data, // Read data

input wire s0_rdy_, // Ready

// Bus slave 1

input wire [`WordDataBus] s1_rd_data, // Read data

input wire s1_rdy_, // Ready

// Bus slave 2

input wire [`WordDataBus] s2_rd_data, // Read data

input wire s2_rdy_, // Ready

// Bus slave 3

input wire [`WordDataBus] s3_rd_data, // Read data

input wire s3_rdy_, // Ready

// Bus slave 4

input wire [`WordDataBus] s4_rd_data, // Read data

input wire s4_rdy_, // Ready

// Bus slave 5

input wire [`WordDataBus] s5_rd_data, // Read data

input wire s5_rdy_, // Ready

// Bus slave 6

input wire [`WordDataBus] s6_rd_data, // Read data

input wire s6_rdy_, // Ready

// Bus slave 7

input wire [`WordDataBus] s7_rd_data, // Read data

input wire s7_rdy_, // Ready

/********** Bus master common signals **********/

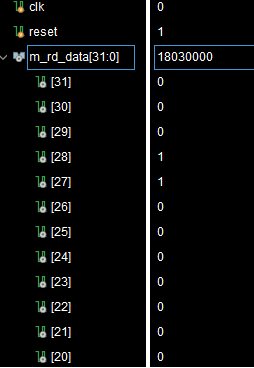

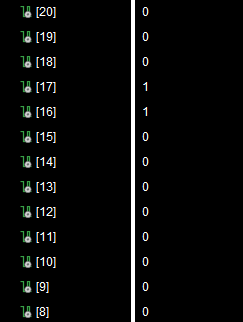

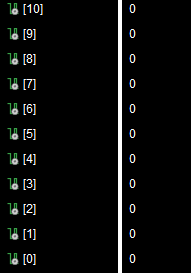

output reg [`WordDataBus] m_rd_data, // Read data

output reg m_rdy_

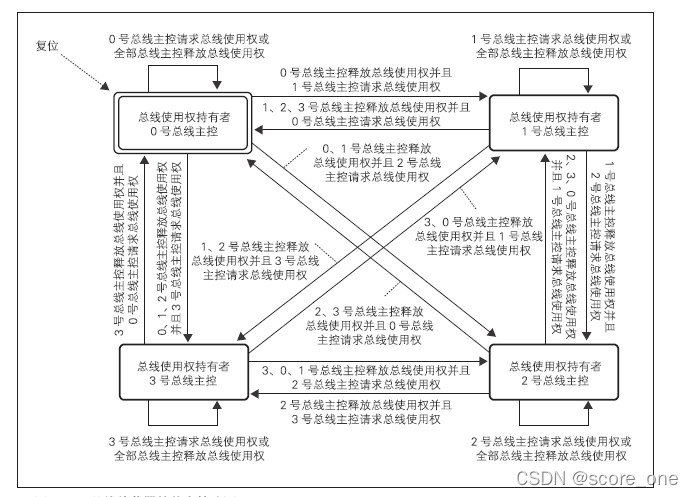

1.�����ٲ�����ʵ��

������ѯ����,ʵ�����ȼ�����

��������req����,���grnt,�������߿���Ȩ

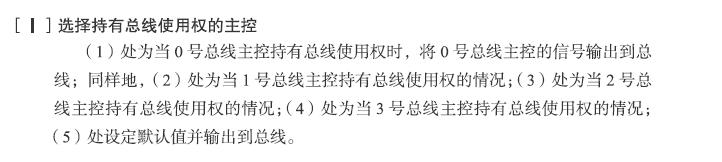

2.�������ض�·������

�������ź������BUS����

���ٲ�����˭grnt�ź�,�ĸ����ؾͿ����źŸ�BUS

����,Ĭ�������,0�����ص�addr��ַ,as_��ַ��־λ,rw��д�ź�,wr_dataд�����ݡ�ȫ����ֵ��output s�Ķ�Ӧ�š�

3.��ַ������

ʵ�ֵ�ַӳ��,����addr�����������ĸ�����,�����Ӧ��cs_�ź�

4.���ߴ�����·������

����cs_�ź�,����Ӧ��slaver��rd_data��rdy_�ź����

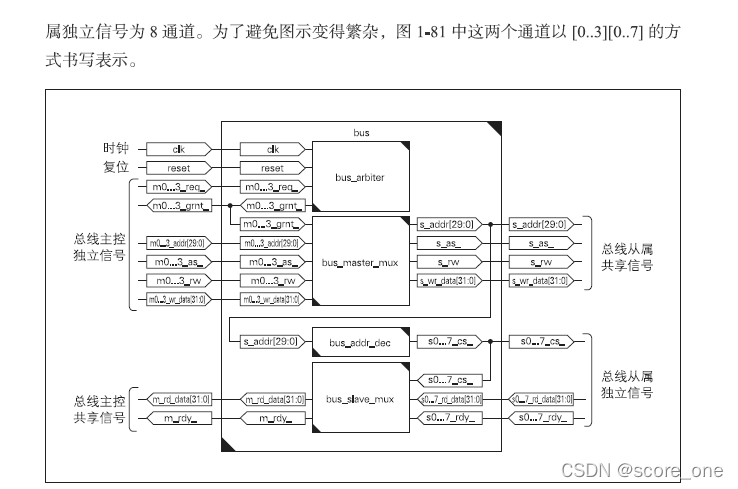

5.TOPģ������

�ع����ĵĶ˿ڶ���,���ǿ��Եõ�����ģ�������ϵ

1.arbiterģ��,��������clk,reset,

��m0-m4��req�źŸ�����ѯ���������Ӧ��grnt�ź�,ֻ�еõ�grnt�źŲſ��Եõ�BUS�Ŀ���Ȩ��

2.master_muxģ��,����arbiter������grnt�ź�,���õ�����Ȩ����������ź����,��s_addr,,s_as_,,s_rw,,s_wr_data ��

3.addr_decģ��,����master_mux�����s_addr,����ַǰ��λȡ��,�ж��ĸ�slaver������,�����Ƶ�slaver�õ�cs_��־λ

4.slave_muxģ��,���ݵ�ַ��������cs_��־λ,����Ӧ��slaver���ź�,��rd_data,rdy_,�����output��m_rd_data, m_rdy_

6.����ROM,��Ϊslaver0

����֤ģ����,���ǽ�������0�ſ��ƴ���0��,��ȡ����0������,���ǽ���ֻ���洢��ROM����0�����ߴ�����

rom�Ķ˿�:

part2.single port Read Only Memory

1.rom

input wire clk, // Clock

input wire reset, // Asynchronous reset

/********** Bus interface **********/

input wire cs_, // Chip select

input wire as_, // Address strobe

input wire [`RomAddrBus] addr, // Address

output wire [`WordDataBus] rd_data, // Read data

output reg rdy_ // Ready

��addr��ַ����,�õ���Ӧ��ַ�����������

ʵ�����CXilinx FPGA Block RAM : Single port ROM

x_s3e_sprom x_s3e_sprom (

.clka (clk), // Clock

.addra (addr), // Address

.douta (rd_data) // Read data

);

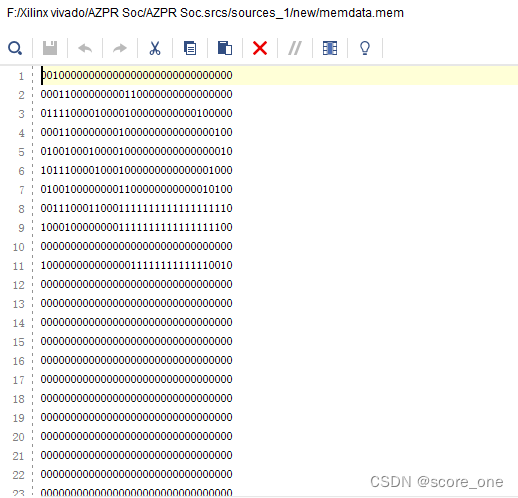

����ROM

module x_s3e_sprom (

input wire clka, // Clock

input wire [`RomAddrBus] addra, // Address

output reg [`WordDataBus] douta // Read data

);

/*

`define ROM_SIZE 8192 // ROM's size

`define ROM_DEPTH 2048 // ROM's depth

`define ROM_ADDR_W 11 // Address width

`define RomAddrBus 10:0 // Address bus

`define RomAddrLoc 10:0 // Address location

`define WordDataBus 31:0 // Data bus

*/

/********** Memory **********/

reg [`WordDataBus] mem [0:`ROM_DEPTH-1];

initial begin

$readmemb("memdata.mem", mem, 0, 99);

end

/********** Read access **********/

always @(posedge clka) begin

douta <= #1 mem[addra];

end

endmodule

Ҫע�⽨��memdata.mem�ļ�,�����2���ƴ���

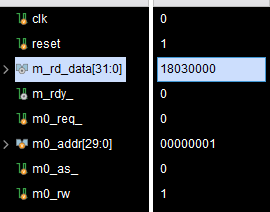

7.����ģ��

ע��s_addr��λ��Ϊ30,ROM��Ҫ��addrλ��Ϊ11λ,����ѡȡ��{{11��b00000_000001}}�ŵ�ROM�ڴ��ַ��ȡ�������ݡ�m0_rw<=`READ;��д�ź�����Ϊ��ȡ

//����ʱ�Ӽ���

initial begin

#10 begin

clk<=1;

reset<=`RESET_ENABLE;

end

#(STEP*3/4)

#STEP begin

reset<=`RESET_DISABLE;

//���������ٲ�������ѯ

#STEP

m0_req_<=`DISABLE_;

m2_req_<=`DISABLE_;

m3_req_<=`DISABLE_;

m1_req_<=`ENABLE_;

#STEP

m0_req_<=`DISABLE_;

m1_req_<=`DISABLE_;

m3_req_<=`DISABLE_;

m2_req_<=`ENABLE_;

#STEP

m0_req_<=`DISABLE_;

m1_req_<=`DISABLE_;

m2_req_<=`DISABLE_;

m3_req_<=`ENABLE_;

#STEP

m3_req_<=`DISABLE_;

m1_req_<=`DISABLE_;

m2_req_<=`DISABLE_;

m0_req_<=`ENABLE_;

#STEP

m0_addr<={{{3'b000}},{16'b0},{{11'b00000_000001}}};

m0_as_ <=`ENABLE_;

m0_rw<=`READ;

end

#STEP

$finish;

end

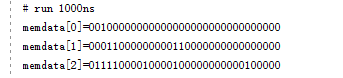

���Խ��:

����ʾROM��0-2�ŵ�ַ������,����testbench��߿��Ƶ���memdata[1]���

����m0_addrѡȡ��Ϊ1�ŵ�ַ,m_rd_dataΪ�������

�����Ӧ��Ϊmemdata[1],��֤�ɹ�.