1.监沿器

监沿器用来鉴定上升沿或下降沿

具体实现:前一刻时钟与现时刻时钟比较

信号经打一拍处理后存为前一刻信号,即比原信号慢了一个时钟的信号,因此可以根据两者的比较检测出上升沿或者下降沿。当现时刻为1,前时刻为0时,说明从上个时钟的0,变为这个时钟的1,判断出上升沿,同理可以判断出下降沿。具体代码如下:

module identify_tool

(

input clk,

input rst_n,

input signal,

output wire pose,

output wire nege

);

//内部信号

reg signal_before;

//前一刻信号值寄存

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)begin

signal_before <= 0;

end

else begin

signal_before <= signal ;

end

end

//上升下降判断

assign nege = signal==0 && signal_before==1;

assign pose = signal==1 && signal_before==0;

endmodule

测试代码:

`timescale 1 ns/1 ns

module tb_identify_tool();

reg clk;

reg rst_n;

reg signal;

wire pose;

wire nege;

parameter CYCLE = 20;

initial begin

clk = 0;

forever

#(CYCLE/2)

clk = ~clk;

end

initial begin

rst_n = 1;

#2;

rst_n = 0;

#2;

rst_n = 1;

end

identify_tool u1

(

.clk (clk),

.rst_n (rst_n),

.signal (signal),

.pose (pose),

.nege (nege)

);

initial begin

signal = 0;

end

always@(posedge clk)begin

signal = {$random}%2;

end

endmodule

仿真结果:

2.PWM输出

PWM输出主要有两个参数:

第一,波的周期:一个完整波形的时间

第二,波的占空比:一个周期中高电平所占百分比

举个例子:一个周期是10ms,占空比是50%的PWM波,波形如下:

下面是参数化的代码,下例中输出的PWM波的周期是1us(一个时钟周期为20ns),占空比是20%

module pwm

(

input clk,

input rst_n,

output reg pwm

);

//参数 周期以及占空比

parameter CYCLE = 50; //1000ns = 1us

parameter PERCENT = 20; //20%

reg [7:0] cnt_T; //随计数最大值改动,这里最大计数到49,因此需要8位

//功能块

always@(posedge clk or negedge rst_n)begin

if (!rst_n)

cnt_T <= 0;

else if(cnt_T == CYCLE-1)

cnt_T <= 0;

else

cnt_T <= cnt_T +1;

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

pwm <= 0;

else if (cnt_T <= CYCLE * PERCENT /100 -1 )

pwm <= 1;

else

pwm <= 0;

end

endmodule

测试代码:

`timescale 1 ns/1 ns

module tb_pwm();

reg clk;

reg rst_n;

wire pwm;

parameter CYCLE = 20;

initial begin

clk = 0;

forever

#(CYCLE/2)

clk = ~clk;

end

initial begin

rst_n = 1;

#2

rst_n = 0;

#2

rst_n = 1;

end

pwm u1

(

.clk (clk),

.rst_n (rst_n),

.pwm (pwm)

);

endmodule

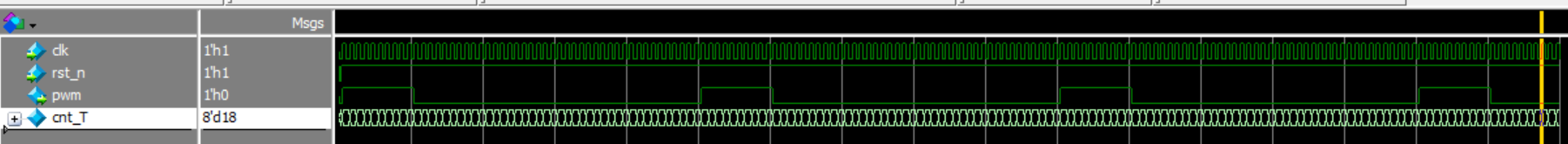

仿真结果: