从零开始学stm32(一)

arm的发展史

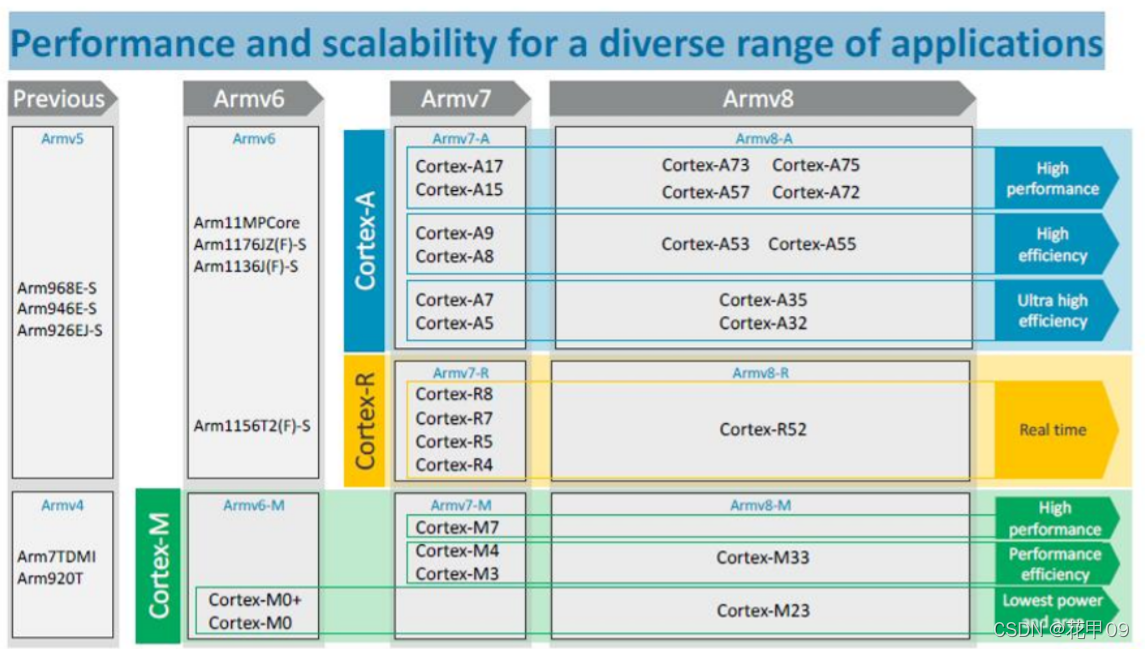

arm架构是一个32位精简指令集(RISC)处理器架构,其广泛底使用在许多嵌入式系统设计中。

体系结构

冯诺依曼体系结构

- 程序(指令)和数据存放在存储器的不同地址,存储单元线性排列,且其位数固定

- 缺点:顺序执行, 程序/数据 ―》内存―》取指令执行指令

- 优点:最大限度的利用资源

- 代表:intel X86

哈佛体系结构

- 程序(指令)与数据存储在不同存储器中

- 优点:并行工作相对独立

- 代表:arm

指令集

arm使用的是精简指令集(RISC)

RISC结构优先选取使用频率较高的简单指令,避免复杂指令;

它将指令的长度固定,指令格式和寻址方式种类减少;

以控制逻辑为止,不用或少用微码控制。

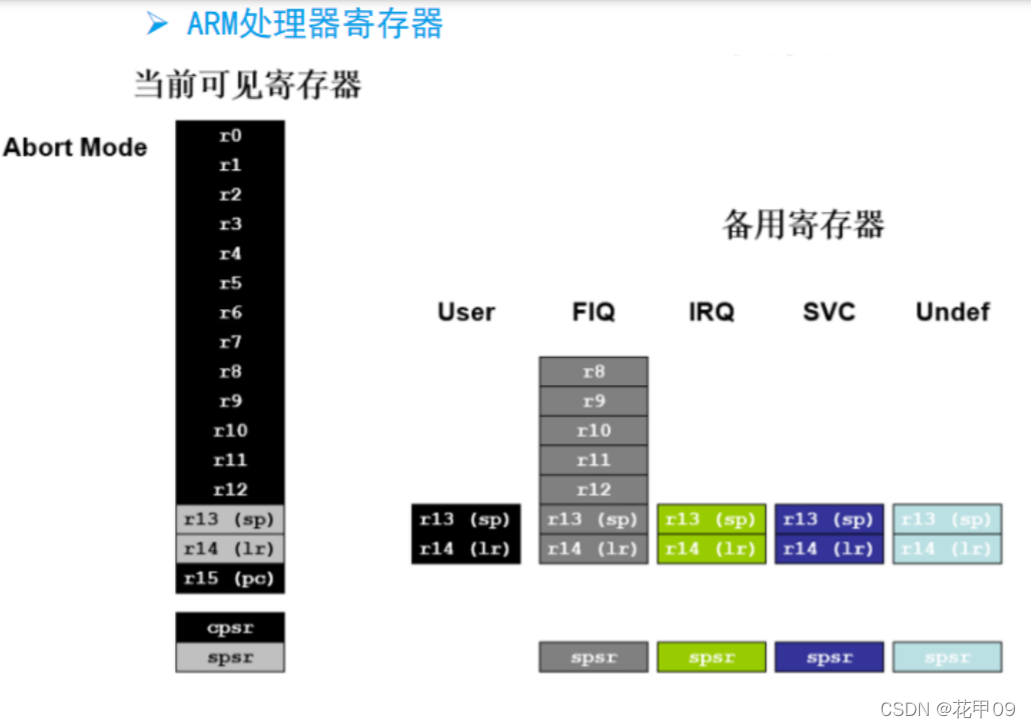

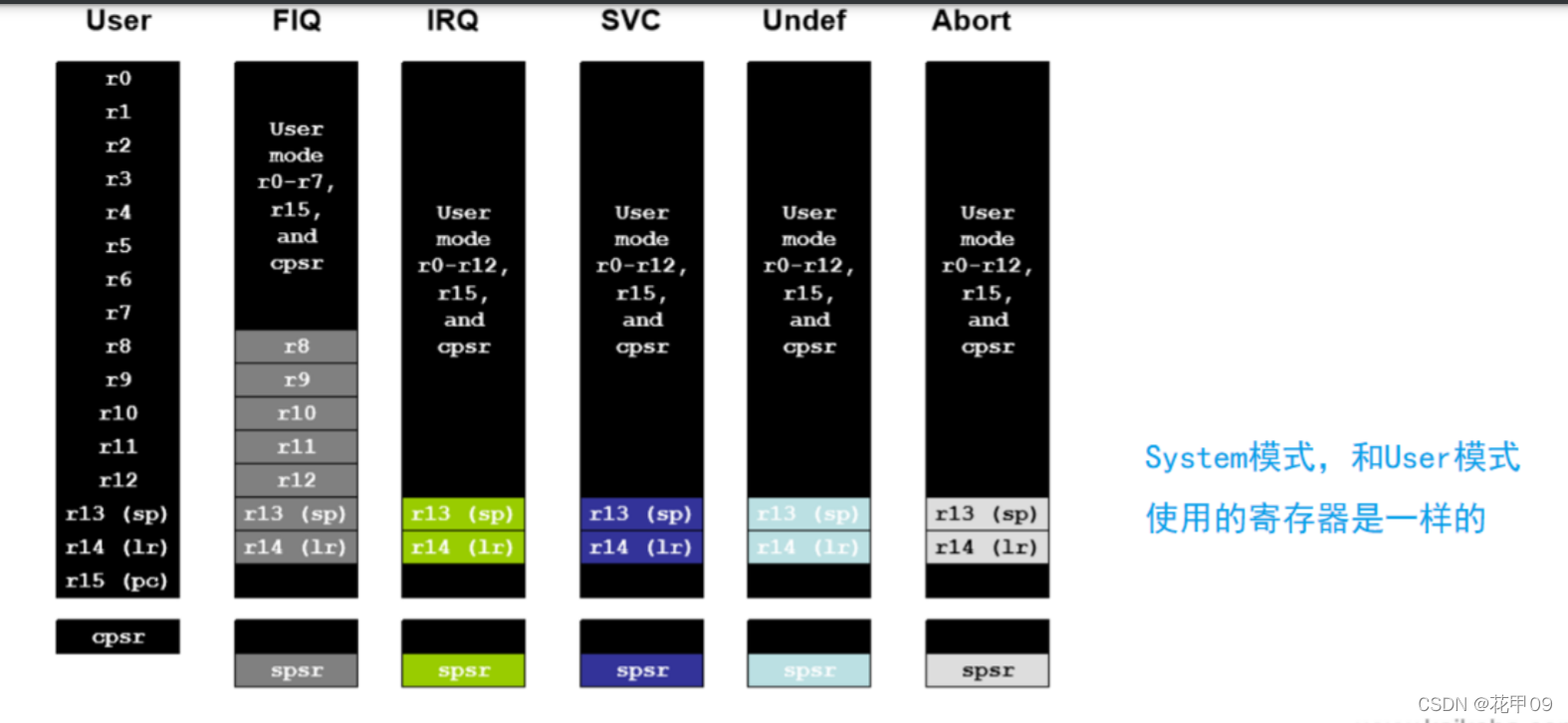

处理器工作模式与寄存器

| 处理器 | 描述 |

|---|---|

| 用户模式(user, usr) | 正常的程序执行模式 |

| 快速中断模式(FIQ, fiq) | 用于高速数据传输和通道处理 |

| 外部中断模式(IRQ,irq) | 用于通常的中断处理 |

| 特权模式(supervisor,sve) | 供操作系统使用的一种保护模式 |

| 数据访问中止模式(abort,abt) | 用于虚拟存储及存储保护 |

| 未定义指令中止模式(undefined,und) | 用于支持通过软件仿真硬件的协处理器 |

| 系统模式(system,sys) | 用于运行特权级的操作系统任务 |

R13(堆栈指针,SP)

R14(连接寄存器,LR)

R15(程序计数器,PC)

cpsr与spsr: 程序状态寄存器,spsr是cpsr的影子寄存器

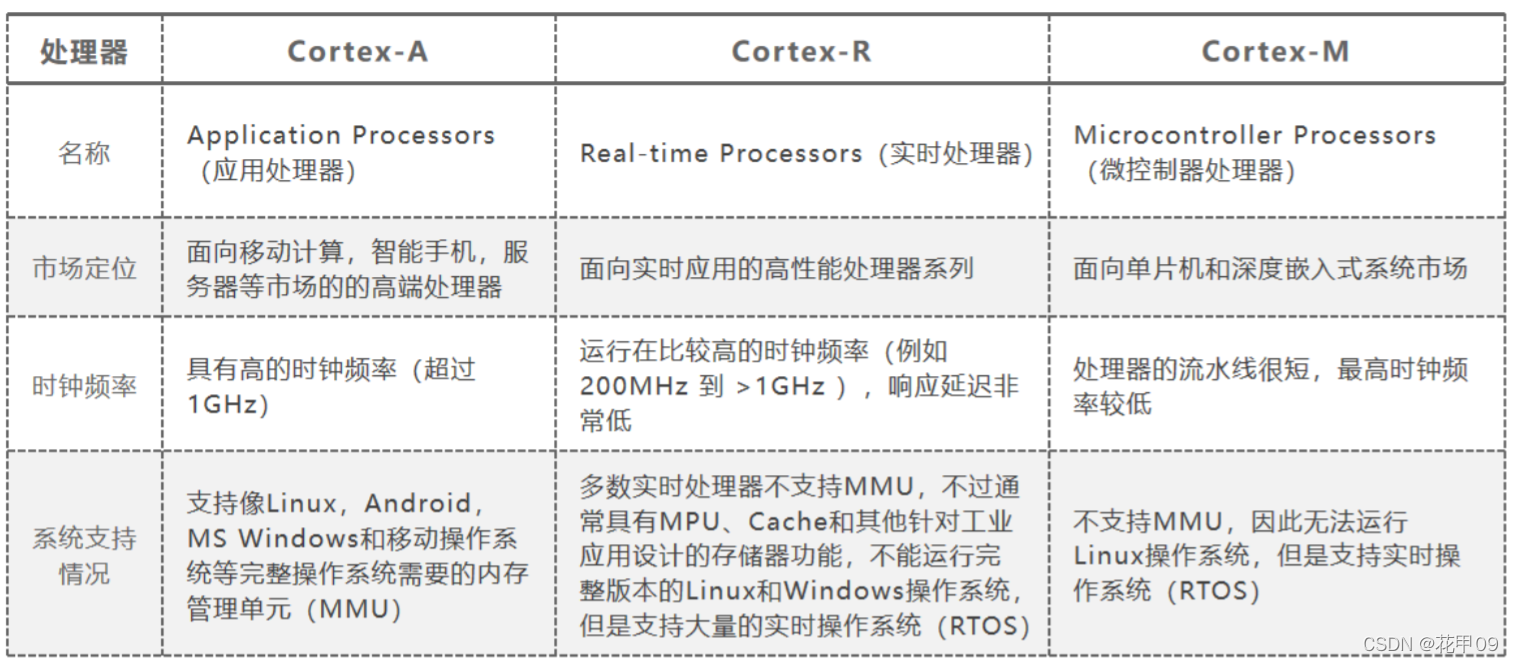

cortex-M3与stm32概述

cortex-M3 是一个32位处理器内核,属于armv7架构,哈佛体系结构,其内部数据存取路径、寄存器、存储器接口均是32位。

stm32f103xx的特点:

- 内核:arm cortex-m3 32位的RISC内核

- 工作频率:72MHz

- stm32f103xx系列成员之间完全是脚对脚兼容,软件和功能上也兼容

- 内置高速存储器,具有丰富的增强I/O端口,和连接到两条APB总线的外设,所有型号的器件都包含2个12位的ADC,7个定时器,还包含标准的通信接口

stm32时钟系统RCC

时钟系统的意义:命脉 驱动源

- 电源开关(有助于达到低功耗)

- 调节速度(stm32系统内核,各种总线和外设所需的工作频率)

寄存器

- RCC_CR时钟控制寄存器

- RCC_CFGR时钟配置寄存器