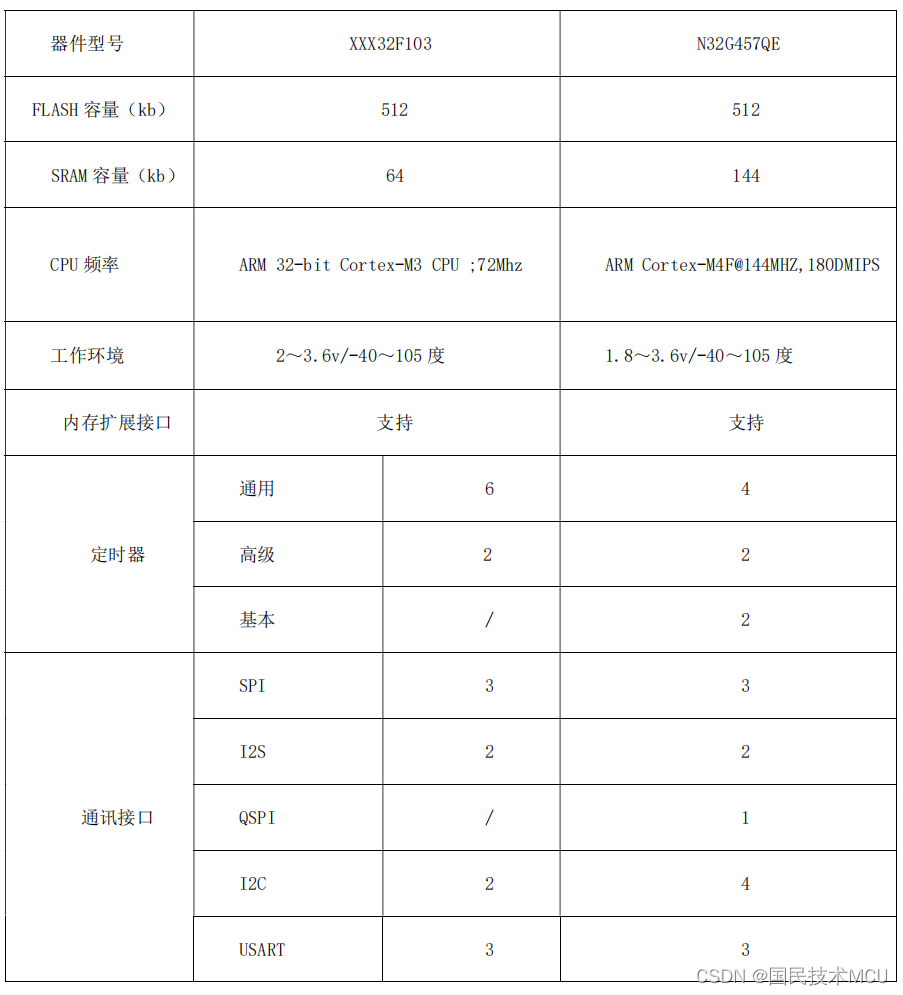

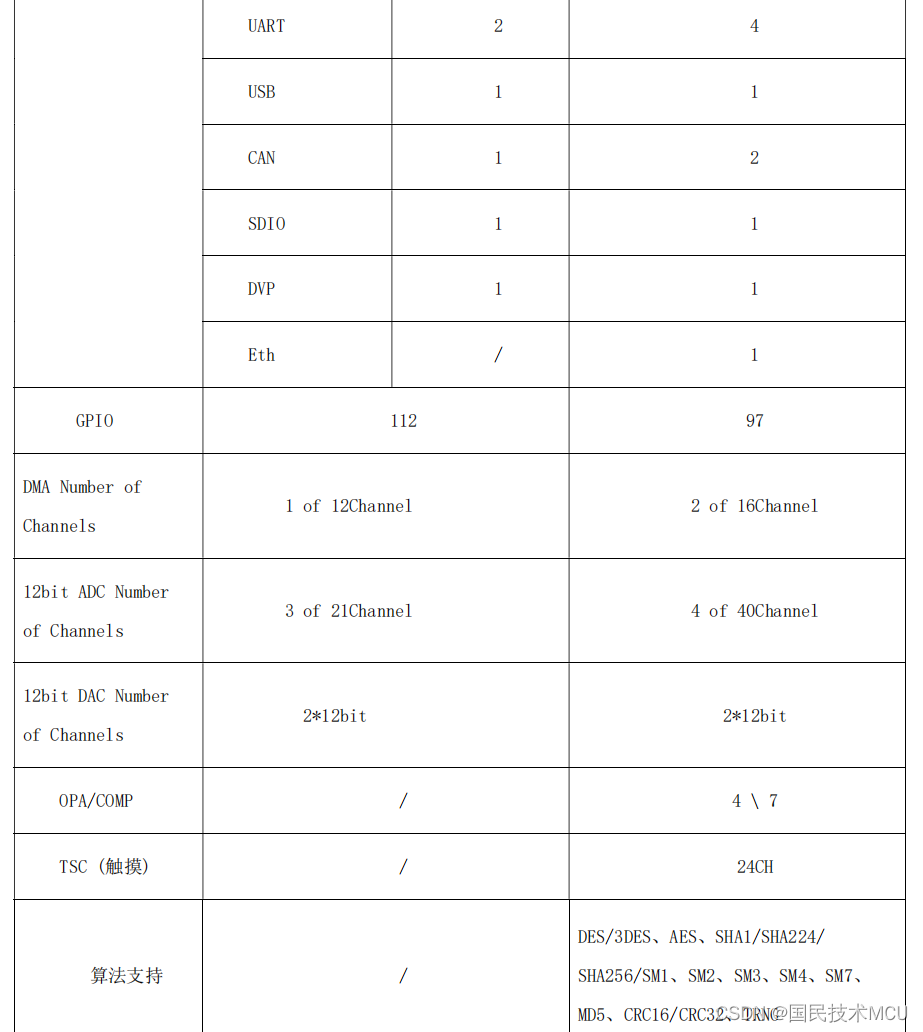

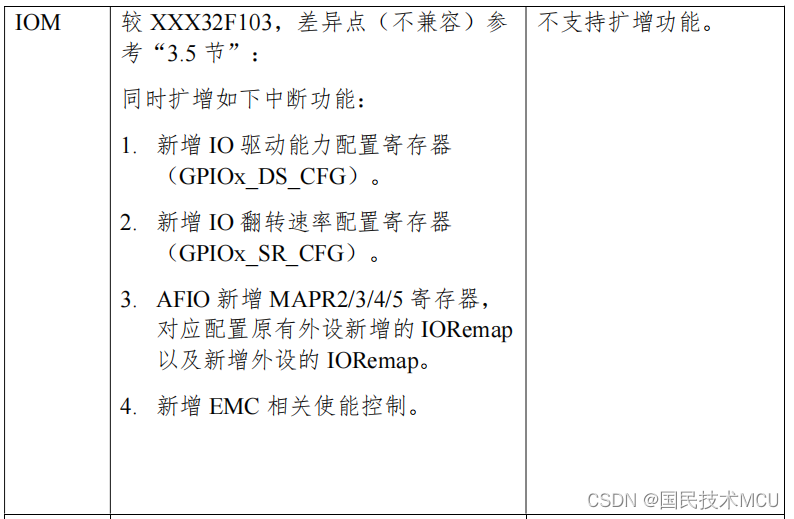

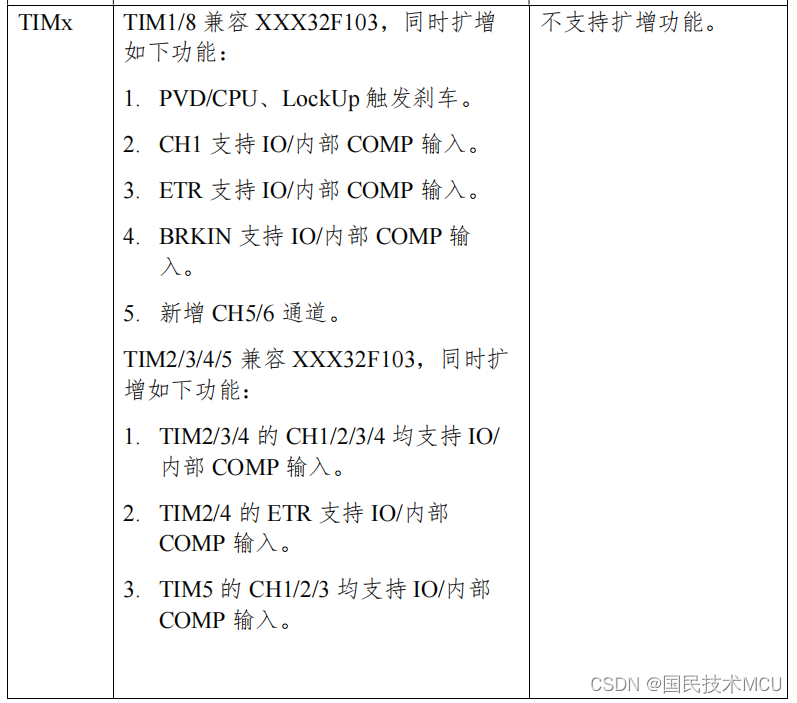

芯片资源整体对比

器件型号 STM32F103 & N32G457QE

1 N32G45X 系列与 STM32F103 系列异同

N32G45X 系列微控制器基本兼容 STM32F103 系列,同时强化和扩展了一些功

能模块,有些地方与 STM32F103 不同,可参见本文档下述章节描述。

1.1 相同点概述

? 管脚定义:相同封装管脚定义基本实现 PIN-TO-PIN 兼容。扩增的外设作

管脚复用定义延伸。

? 寻址空间:内存与模块寄存器逻辑地址相同。扩展外设或扩展功能占用

XXX32F103 保留地址空间。

? 库函数文件:大部分模块驱动库兼容,仅部分不兼容模块可参考“第 2

章”进行驱动库调整。

? 编译工具: KEIL5。

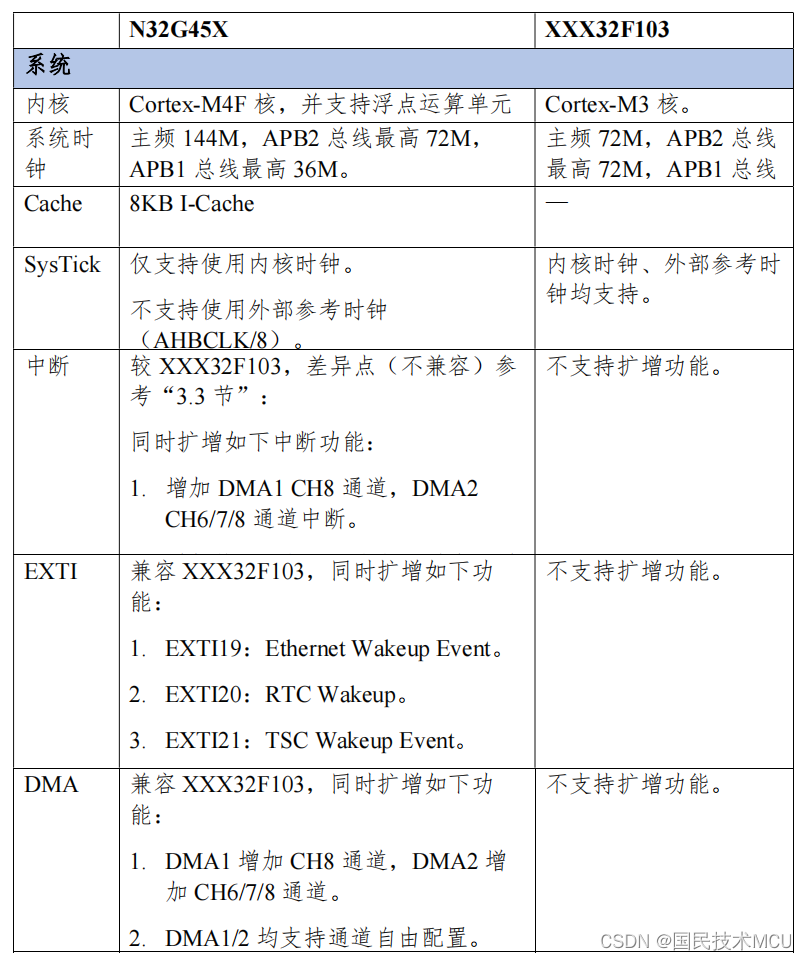

1.2 差异点概述

2 快速替换 XXX32F103

? 导入 N32G45X PACK 包

导入 N32G45X 对应规格芯片的 PACK 包。

? 工程配置

请参考“3.1 节”。

? 驱动代码

- xxx32f10x.h 文件:替换。

- 启动文件 startup_xxx32f10x_hd.s:替换。

- xxx32f10x_flash.c/.h 文件:替换。

- xxx32f10x_rcc.h/.c 文件:替换。

- xxx32f10x_gpio.h/.c 文件:替换。

- xxx32f10x_exti.h/.c 文件:替换。

- xxx32f10x_adc.h/.c 文件:替换。

- xxx32f10x_rtc.h/.c 文件:替换。

对原工程中的以上文件进行替换。

? 应用代码 - 在 main 中添加如下配置代码,此段代码在使用 ADC 和 SDIO 时必须

添加,否则会影响模块的使用。如下图:

Int main()

{

RCC_APB1PeriphClockCmd(RCC_APB1Periph_PWR,ENABLE);

PWR->CR3 |= 0x00000001;

RCC_APB1PeriphClockCmd(RCC_APB1Periph_PWR,DISABLE);

} - 应用代码中如果使用的模块具有不兼容点,则需要参考“1.2 节”和

“第 3 章”的内容进行更改;如果使用模块均兼容,则无需更改。

3 N32G45X 模块不兼容点解析

功能点不兼容,将会影响底层驱动或应用代码的设计;为快速将原有的

XXX32F103 工程运行在 N32G45X 平台上,下文记录 N32G45X 与 XXX32F103 不

兼容的功能点,可供移植参考。

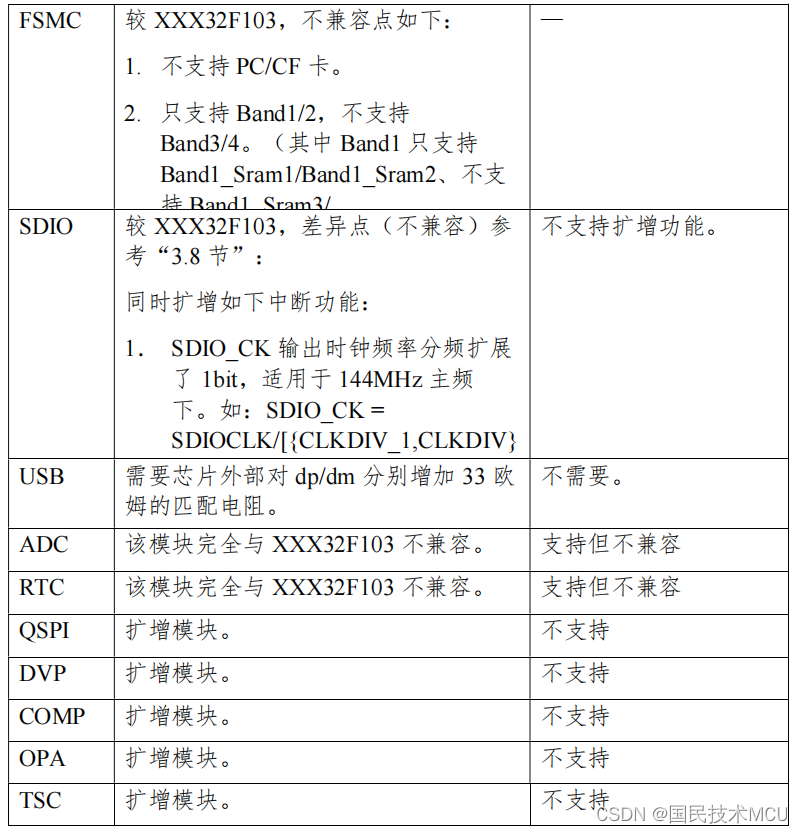

3.1 内核

? 描述

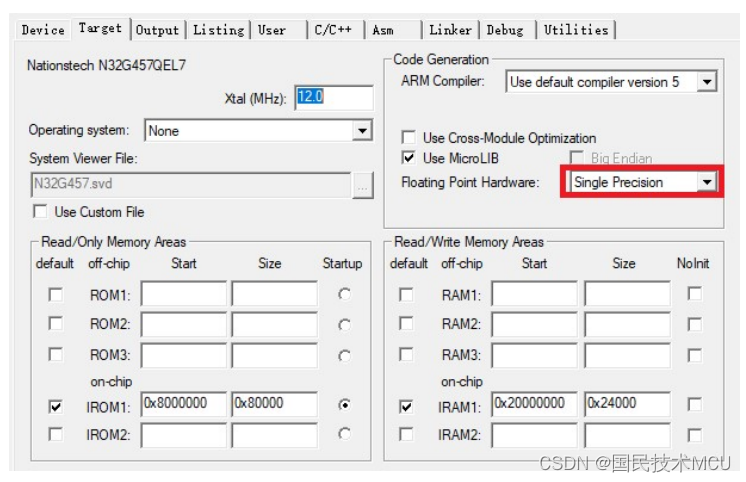

N32G45X 使用 Cortex-M4F 核,如果原代码中有涉及浮点类型的定义或运

算,直接运行在 N32G45X 会进 HardFualt。

? 方案

方案 1:仅对原代码工程配置进行如下修改

方案 2:修改工程配置+代码中添加对浮点运算的支持

然后在进入 main 之前启动 FPU 功能,需要对 xxx32f10x.h 和

system_xxx32f10x.c 文件进行微小修改:

1、打开 xxx32f10x.h 文件,将 #include“core_cm3.h” 改为#include

“core_cm4.h”;

2、打开 system_xxx32f10x.c 文件,在 SystemInit 函数中添加下面一条语

句:SCB->CPACR |= ((3UL << 10 * 2) | (3UL << 11 * 2));

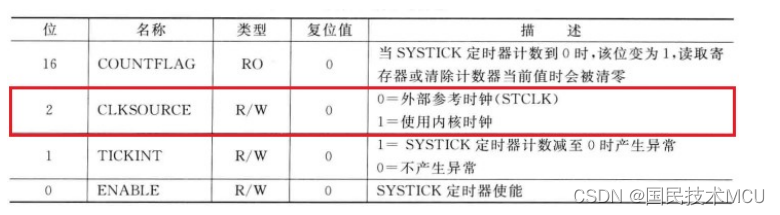

3.2 SYSTICK

? 描述

N32G45X 仅支持 SysTick 使用内部核时钟,不支持使用外部参考时钟

AHBCLK/8。

? 方案

如果原代码中 SysTick 配置使用外部参考时钟,则需要配置为内核时钟,

即配置如下寄存器的 CLKSOURCE 位=1。

具体代码如下:

SysTick_CLKSourceConfig(SysTick_CLKSource_HCLK ); //选择内部时钟

3.3 中断

? 描述

N32G45X 与 XXX32F103 中断不兼容点如下:

- RTC 全局中断改为 RTC_WAKEUP_EXTI20 中断。

- DMA2 的 CH4/5 由共用一个中断号改为分别使用两个中断号。

原应用代码中使用到以上中断时,需要进行调整。

? 方案 - 使用 RTC 全局中断(RTC_IRQn)时,不仅需要配置 RTC,还需要配

置 EXTI20(如下图),同时结合“3.4 节、3.7 节”。

void EXTI20_RTCWKUP_Configuration(FunctionalState NewState)

{

EXTI_InitTypeDef EXTI_InitStructure;

NVIC_InitTypeDef NVIC_InitStructure;

EXTI_ClearITPendingBit(EXTI_Line20);

EXTI_InitStructure.EXTI_Line = EXTI Line20;

EXTI_InitStructure.EXTI_Mode = EXTI_Mode_Interrupt;

EXTI_InitStructure.EXTI_Trigger = EXTI_Trigger_Rising;

EXTI_InitStructure.EXTI_LineCmd = ENABLE;

EXTI_Init(&EXTI_InitStructure);

/Enable the RTC WakeUp Interrupt/

NVIC_InitStructure.NVIC_IRQChannel = RTC_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelCmd = NewState;

NVIC_Init(&NVIC_InitStructure);

} - 当原代码中使用到 DMA2_CH4/5 时,需要分别定义 CH4/5 的中断号

和中断服务函数,涉及改动的文件包括 xxx32f10x.h、启动文件。

原配置:

DMA2_Channel4_5_IRQn = 59,

EXPORT DMA2_Channel4_5_IRQHandler[WEAK]

修改如下:

DMA2_Channel4_IRQn = 59, /DMA2 Channel 4 global Interrupt/

DMA2_Channel5_IRQn = 60, /DMA2 Channel 5 global Interrupt/

EXPORT DMA2_Channel4_IRQHandler [WEAK]

EXPORT DMA2_Channel5_IRQHandler [WEAK]

3.4 EXTI

? 描述

使用 RTC wakeup 功能时,需要使用新增 EXTI20。

? 方案

参考“3.7 节”

3.5 IOM

? 描述

N32G45X 与 XXX32F103 IOM 不兼容点如下:

- PA8 在上电启动时进行芯片模式判断,会被自动设置为下拉输入,结

束后为高阻态。 - 除以下引脚外,其他 IO 上电默认为高阻态(XXX32F103 为输入浮空

态):

PB4/NJTRST:输入上拉;

PB3/TDO:输入无上下拉;

PA15/TDI:输入上拉;

PA14/JTCK-SWCLK:输入上拉;

PA13/JTMS-SWDIO:输入上拉;

PB2/BOOT1:输入下拉;

BOOT0:输入下拉;

NRST:输入输出上拉; - NRST 引脚无法输出内部各复位源引起的系统复位信号,除非板上的

NRST 引脚接的是 1nF 以内电容负载以及 10K 以内的上拉电阻。 - SPI1/2/3 做主机时,NSS 可选 Idle 时输出 1(接单从机)还是高阻

(接多从机) - 对端口配置低/高寄存器(GPIOx_CRL/CRH)进行修改:

? 方案 - 上述 1/2/3 点可能影响硬件电路设计,可供参考。

- 上述第 5 点,需要修改 xxx32f10x_gpio.h 文件中相关代码如下:

原结构体:

typedef enum

{

GPIO_Speed_10MHz = 1,

GPIO_Speed_2Mhz,

GPIO_Speed_50MHz

}GPIOSpeed_TypeDef;

修改为:

typedef enum

{

GPIO_Speed_2MHz = 1,

GPIO_Speed_10Mhz,

GPIO_Speed_50MHz

}GPIOSpeed_TypeDef;

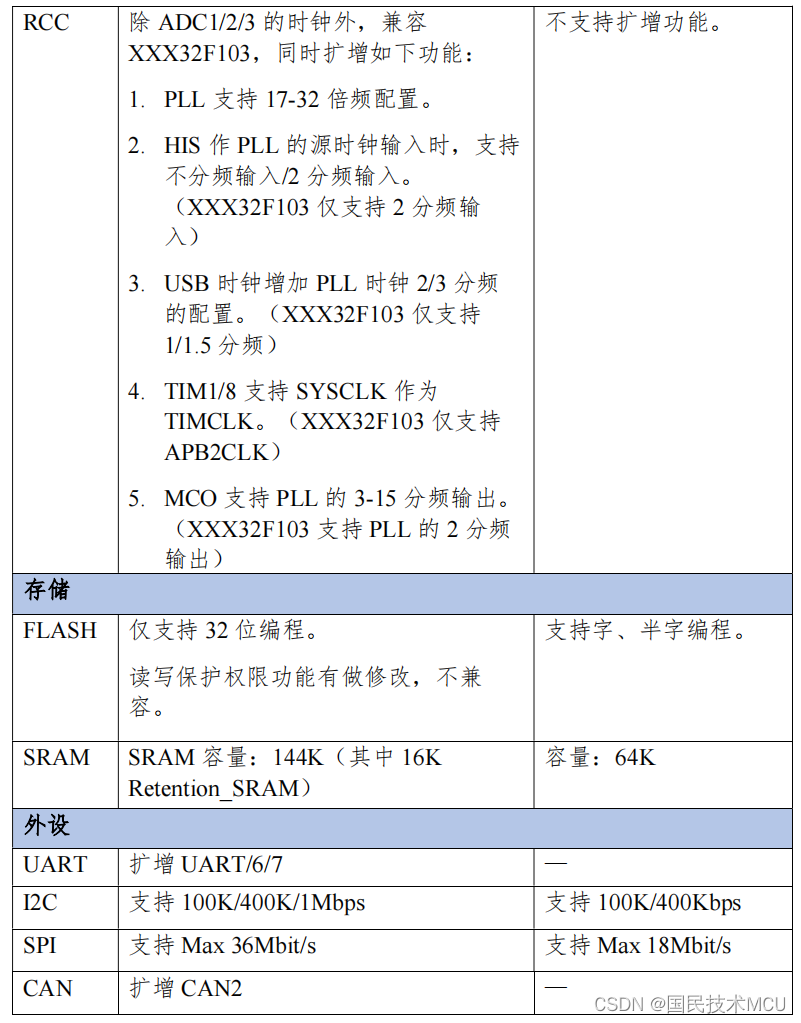

3.6 FLASH

? 描述

N32G45X 仅支持 32 位(字)编程,不支持半字编程。

? 方案

由于本模块涉及差异点较大,需要使用 N32G45X 的库替换 XXX32F103

的库。(模块库接口基本保持一致)

3.7 RTC

? 描述

RTC 模块与 XXX32F103 的 RTC 完全不一样,具体功能可参考 N32G45X

参考手册。

? 方案

- RTC 应用代码移植:首先需要根据“第 2 章”替换相关文件,应用代

码需要查看参考手册。 - 注意点 1:RTC 预分频寄存器的 Prediv_A 和 Prediv_S 不能设置为 0。

- 注意点 2:RTC Alarm_AB 和 Auto_WakeUp 均可唤醒 Stop2,

Alarm_AB 可喊醒 Standby,但是前提不能使用 HSE/128 作为 RTC 时

钟输入;因为 Stop2 和 Standby 模式下 HSE 时钟 停止工作。

3.8 SDIO

? 描述

N32G45X 与 XXX32F103 SDIO 不兼容点如下:

SDIO 配置为 DMA 发送时,如果主频为 72M 或以上,当分频系数

CLKDIV 为 9-153 中任意一个值时,会导致 SDIO 无法完成数据发送。

? 方案

在原有代码的基础上,SDIO_Write 时需将 SDIO_DCTRL 寄存器的 BIT12

写 1;SDIO_Read 时需将 BIT12 写 0。

3.9 ADC

? 描述

ADC 模块与 XXX32F103 的 ADC 完全不一样,具体功能可参考

N32G45X 参考手册

? 方案

本模块的主要区别在于模块时钟的配置 XXX32F103 的 ADC1/2/3 仅用到

APB2CLK,N32G45X 的 ADC1/2/3 使用 HCLK/PLLCLK/ADC1MCLK

(其中 HCLK/PLLCLK 是二选一,ADC1MCLK 必须配置)

- 驱动:参考“第 2 章”替换相关文件。

- 应用:需查看“参考手册”。

3.10 XFMC

? 描述

- 不支持 PC/CF 卡扩展。

- 只支持 Band1/2,不支持 Band3/4。(其中 Band1 只支持

Band1_Sram1/Band1_Sram2、不支持 Band1_Sram3/Band1_Sram4)

? 方案

根据以上区别进行具体使用。例如:如果原代码中使用 sram3,则需要改

为使用 sram1/sram2。

原配置:

//使用 NOR/SRAM 的 Bank1.sector3,地址位 HADDR[27,26]=10

#define Bank1_SRAM3_ADDR ((uint32_t)(0x68000000))

修改为:

//使用 NOR/SRAM 的 Bank1.sector1,地址位 HADDR[27,26]=10

#define Bank1_SRAM1_ADDR ((uint32_t)(0x60000000))

控制信号线端口配置:

/NE1,对应的基地址 0x60000000/

#define FSMC_CS_GPIO_PORT GPIOD

#define FSMC_CS_GPIO_CLK RCC_APB2Periph_GPIOD

#define FSMC_CS_GPIO_PIN GPIO_Pin_7

3.11 RCC

? 描述

RCC 模块中 ADC1/2/3 的时钟与 XXX32F103 不兼容,XXX32F103 的

ADC1/2/3 使能时钟挂载在 APB2 上,而 N32G45X 挂载在 AHB 上;具体

差异可查看“参考手册”RCC 与 ADC 章节。

? 方案

修改原代码中 ADCx 模块时钟配置的相关接口。如下:

原调用函数:

void RCC_ADCCLKConfig(uint32_t RCC_PCLK2);

修改为以下函数:

void RCC_ADC1MLKConfig(uint32_t RCC_ADC1MCLKSource,uint32_t MPrescaler);

void RCC_ADCPLLCLKCmd(uint32_t RCC_ADCPLLCLKPrescaler,FunctionalState NewState);

void RCC_ADCHCLKConfig(uint32_t RCC_ADCHCLKPrescaler);

国民代理