GT Transceiver的配置-RXOUTCLK的来源及生成

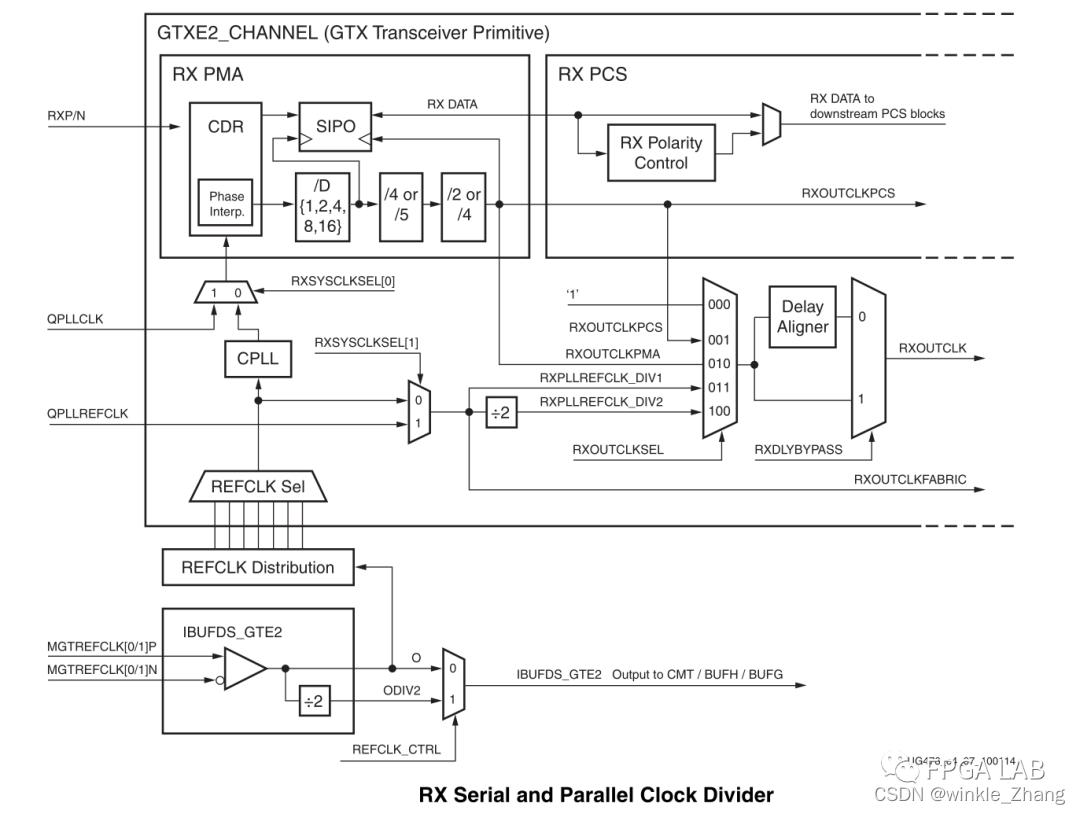

RX时钟分频控制块有两个主要部分:串行时钟分频器控制和并行时钟分频器和选择器控制。时钟分频器和选择器的细节见图。

前面的文章中,已经介绍了TXOUTCLK的来源及其生成。这篇文章可以算是其姊妹篇,介绍RXOUTCLK的来源。

为何要追溯其来源,这是因为我们上篇介绍USRCLK的文章中提到RXUSRCLK是由RXOUTCLK驱动的,其中一段话是这样的:

(1)如果通道被配置成由同一个振荡器驱动发射器和接收器的参考时钟,TXOUTCLK可以用来驱动RXUSRCLK和RXUSRCLK2,其方式与驱动TXUSRCLK和TXUSRCLK2相同。

(2)如果单独的振荡器驱动通道上发射器和接收器的参考时钟,并且不使用时钟校正,RXUSRCLK和RXUSRCLK2必须由RXOUTCLK驱动(RXOUTCLKSEL = 3’b010用于RXOUTCLKPMA),并且必须使用相位校正电路。

如下图为RX时钟分频器的架构框图:

RX串并行时钟分频器架构

来自RX时钟分频器控制块的并行时钟输出可以用作结构逻辑时钟,这取决于线路速率和协议要求。

FPGA逻辑的推荐时钟是来自GTX/GTH收发器之一的RXOUTCLK。

也可以把MGTREFCLK直接接到FPGA逻辑结构上,作为结构时钟使用。

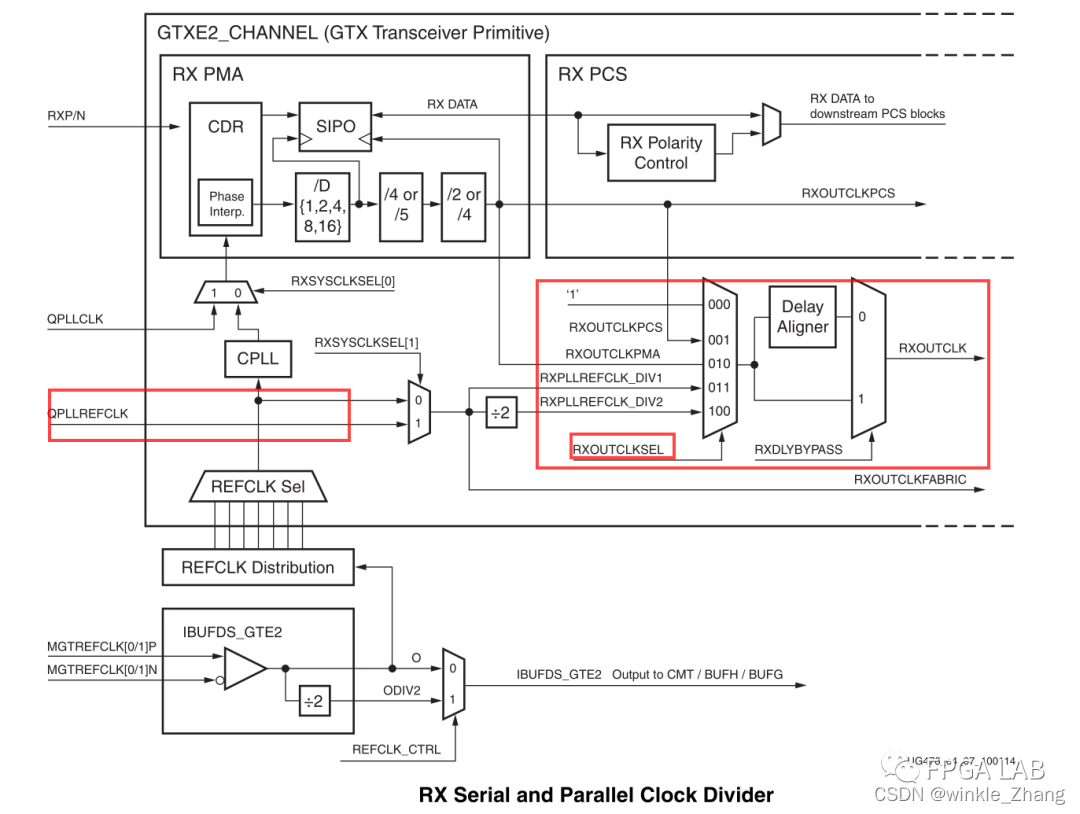

同TXOUTCLK介绍一致,RXOUTCLK的时钟来源如下图标记:

RXOUTCLK的时钟来源

由RXOUTCLKSEL来选择来源:

(1)RXOUTCLKSEL = 3’b001:不建议使用RXOUTCLKPCS路径,因为它产生了来自PCS块的额外延迟。

(2)RXOUTCLKSEL = 3’b010。RXOUTCLKPMA是可以引出FPGA逻辑的恢复时钟。恢复的时钟被那些没有时钟补偿机制的协议使用,需要使用与数据同步的时钟(恢复的时钟),为下游结构逻辑提供时钟。它也被RX PCS块使用。当PLL或CDR被一个相关的复位信号复位时,这个时钟会被中断。

(3)RXOUTCLKSEL = 3’b011或3’b100。RXPLLREFCLK_DIV1或RXPLLREFCLK_DIV2是CPLL或QPLL的输入参考时钟,取决于RXSYSCLKSEL[1]的设置。对于不需要向结构输出恢复时钟的使用,RXPLLREFCLK_DIV1或RXPLLREFCLK_DIV2可以作为系统时钟使用。然而,TXOUTCLK通常被用作系统时钟。