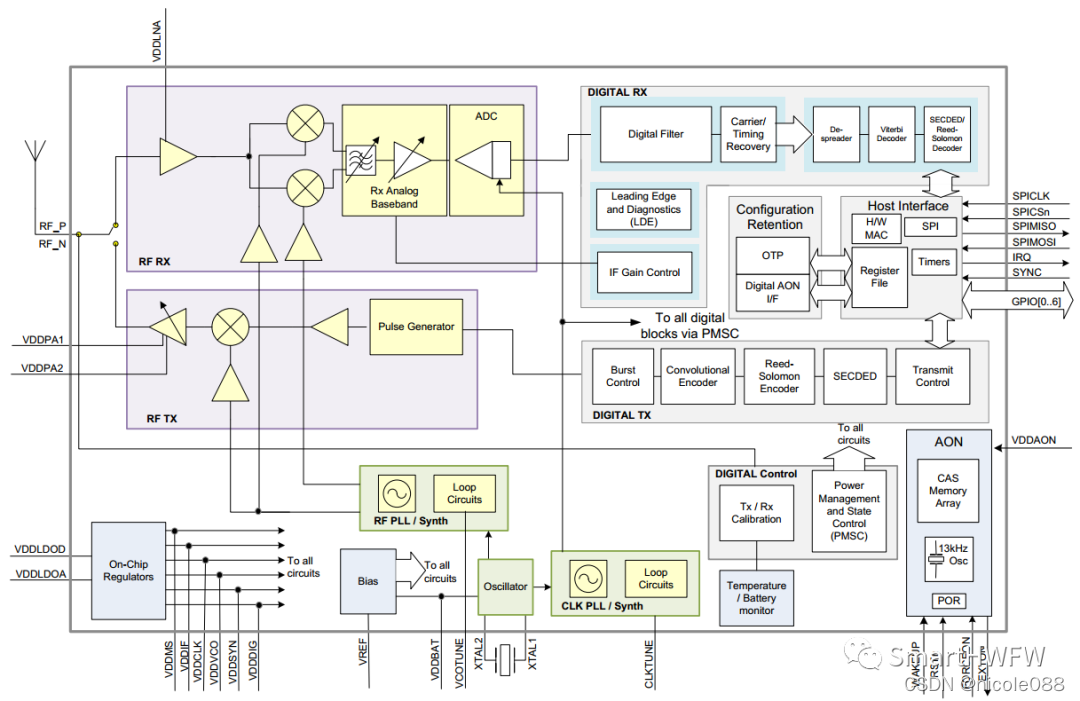

1. ���ܿ��

2. ����&�ӿ�

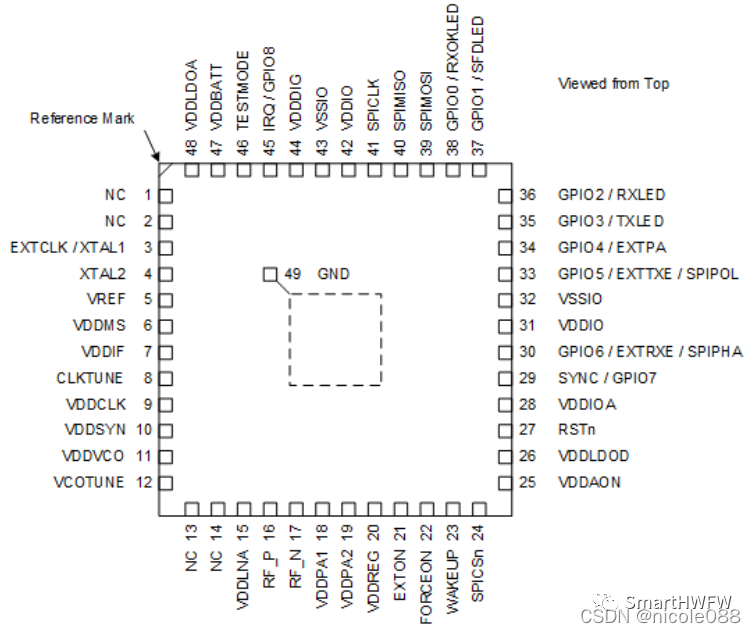

DW1000оƬʹ��QFN-48��װ,����ͼ����:

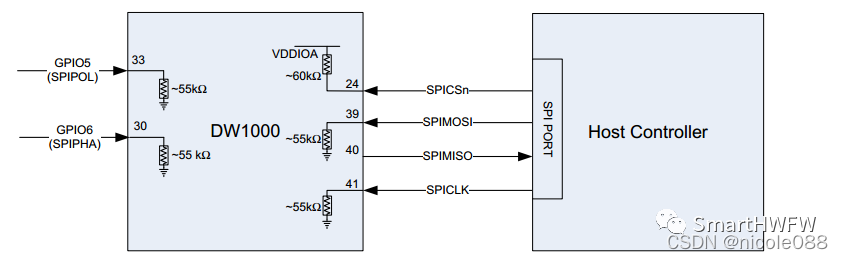

3. �������ӽӿ�

3.1 DW1000����ΪSPI�ӻ�

֧��ʱ�Ӽ��� (SPIPOL=0/1) ����λ (SPIPHA=0/1)��֧�ֵ��ֽںͶ��ֽڶ�/д���ʡ������ֽڶ��ȴ���MSB,�����LSB�� ͨ����SPICSn ��Ϊ�͵�ƽ����������,����SPICSn��Ϊ�ߵ�ƽʱ��ֹ���䡣

3.2 SPI�ӿ�ʹ�õ�����Ϊ

���� ����

GPIO5 ��������

GPIO6 ��������

SPICLK SPIʱ���ź�

SPI MISO SPI�������

SPI MOSI SPI��������

SPICSn SPIƬѡ�ź�(�͵�ƽ��Ч)

tips: DW1000 �����ڲ�������������·,��ȷ�������ӿ��źŶϿ�ʱ�İ�ȫ������ ��Щ�����ڲ�ʹ��,��Ӧ���ڽ��ⲿ�ź��������͡��ڲ���������ֵ�� 34 k�� - 90 k�� ��Χ��,�ڲ���������ֵ�� 40 k�� - 90 k�� ��Χ�ڡ�

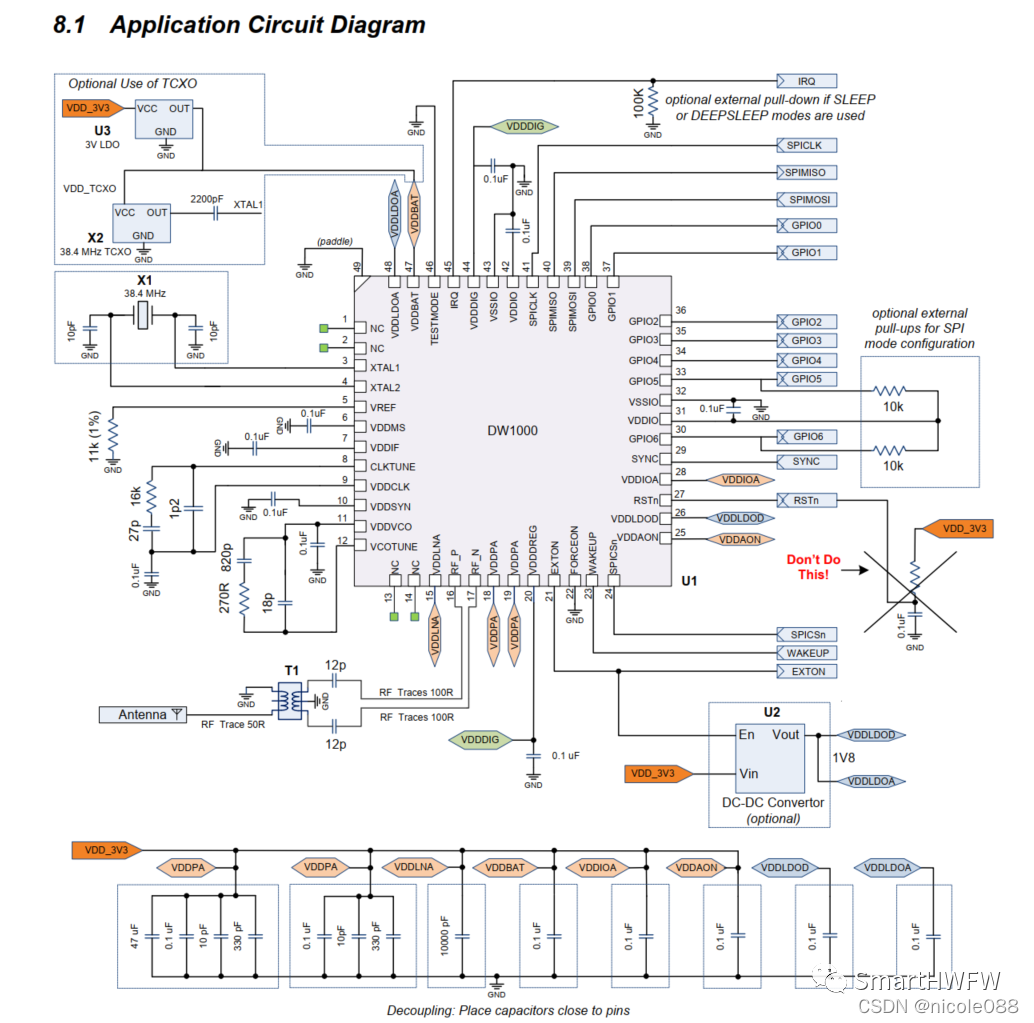

4.��·ͼ

4.1 �����

DW1000����������һ�������¼�����ʱʹ�������ж�����,��֪ͨ�ⲿ�����������������¼���

�ж����ŵļ��Կ���ͨ��ϵͳ���ƼĴ���(Register file: 0x0D �C SystemControl Register)��HIRQ_POLλ�����á��ϵ��Ĭ�ϵļ���Ϊ�ߵ�ƽ,��Ҳ��ȷ��DW1000��˯�ߺ����˯���豸״̬�µ���������е��Ƽ����ԡ���DW1000��˯�������˯�ߵ�ʱ��,�ж����Ŵ��ڸ���״̬,��ʱ�����ⲿ����������,������ܻᴥ����ٵ��жϡ�

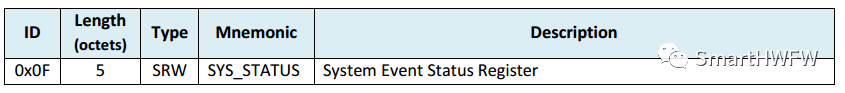

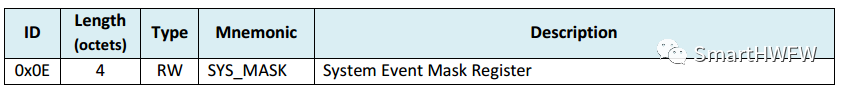

һ����ϵͳ�¼�״̬�Ĵ���( Register file: 0x0F �C System Event Status Register )�е��¼��������Ƿ��ж�,��ȡ������ϵͳ״̬���μĴ���(Register file: 0x0E �C System Event Mask Register)�ж�Ӧλ�����á�

Ĭ�������,���ϵ�����п��Բ����жϵ��¼����ᱻ����,�����ж�Ҳ����ʧ��״̬��

4.2 GPIO

DW1000 �ṩ��8��GPIO���ſ������û����ж��������á��κ�һ��������Ϊ��������ŵĵ�ƽ״̬,�����Ա���ȡ���ϱ�����������ͨ��SPI�ӿ�,������Ϊ���ʱ,��������Ҳ����ͨ��SPI�ӿ��������ƽ��

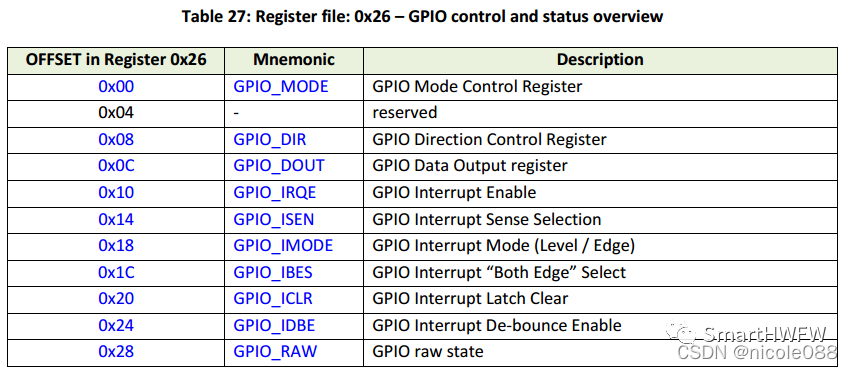

ͨ��GPIO���ƺ�״̬�Ĵ���( Register file: 0x26 �C GPIO control and status)���úͲ���:

Ĭ���ϵ�֮����ЩGPIOȫ��������Ϊ����״̬��

4.3 GPIO���ù��ܱ�:

���� ���ù���˵��

GPIO0/RXOKLED ���յ�����������֡ʱ���ڵ���һ��LED

GPIO1/SFDLED ����������SFDʱ����һ��LED

GPIO2/RXLED �ڽ���ģʽʱ����һ��LED

GPIO3/TXLED �ڷ�������ʱ����һ��LED

GPIO4/EXTPA ����ʹ���ⲿ��Դ���ʷŴ���

GPIO5/EXTTXE/SPIPOL �ϵ�ʱ��������SPI����ģʽ,�ϵ��ָ�ΪĬ��GPIO����

GPIO6/EXTRXE/SPIPHA �ϵ�ʱ��������SPI����ģʽ,�ϵ��ָ�ΪĬ��GPIO����

GPIO8/IRQ ������������

4.4 �����������

���� ���ù���˵��

WAKEUP ��������,���ڴ�DW1000˯��ģʽ�������˯��ģʽ����

EXTON �������,�ⲿ����ʹ������,��DW1000����ʱ���ָߵ�ƽ

SYNC/GPIO7 SYNCͬ������ʱGPIO7,������ű������ⲿʱ��ͬ����������

RSTn ��λ����,�͵�ƽ��Ч