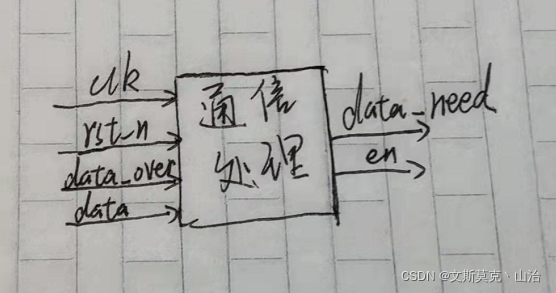

1.通信处理的意义

我们现在已经在06、07两篇文章中完成了单独的发送和接收命令,但是只是传输数据而已,那什么时候传送,什么时候结束这样的问题还没解决;因此这里通过对通信的处理来实现我们想要的自定应串口通信,下面一起来DIY我们自己设计的串口通信

2.实现的功能

①假设我们一次要获得8个数据,数据位宽为8,那么在一堆数据流中怎么才能区别有用无用信号呢?我们可以通过添加起始帧和结束帧;

②当收8’h01时,表示开始传输;

③当接收完8个数据后,传输结束;

④显然,只有命令正确的时候,数据才能有效的输出,这样就多了一层我们可以控制的手段

⑤当我给出一定的数据流时,通过通信处理,可以滤除没用的信号

3.功能实现分析

①:判断是否符合起始帧,从起始帧开始构造传输区域flag

②:数据个数计数,当检测到起始帧开始计数,从计数器为1-7输出数据,到8结束

③:每输出一个数据,给一个使能信号

④:代码

module rs232_diy

(

input clk,

input rst_n,

input data_over,

input [7:0] data,

output wire en,

output wire [7:0] data_need

);

//参数

localparam RX_NUM_END = 9;

//内部信号

reg [3:0] rx_num;

reg flag;

//数据有限传输区域

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)

flag <= 0;

else if(data == 8'h01)

flag <= 1;

else if(rx_num == RX_NUM_END-1)

flag <= 0;

end

//接收数据计数

always @(posedge clk or negedge rst_n)begin

if(rst_n==1'b0)

rx_num <= 0;

else if(data_over && rx_num == RX_NUM_END-1)

rx_num <= 0;

else if(data_over && flag)

rx_num <= rx_num + 1;

end

//使能

assign en = (rx_num >= 'd1)?data_over:0;

//得出有用的数据

assign data_need = (rx_num >= 1 && rx_num <= RX_NUM_END)?data:0;

endmodule

⑤:测试代码

`timescale 1 ns / 1 ns

module tb_rs232_diy();

reg clk;

reg rst_n;

reg data_over;

reg [7:0] data;

wire en;

wire [7:0] data_need;

parameter CYCLE = 20;

initial begin

clk = 0;

forever

#(CYCLE/2)

clk = ~clk;

end

initial begin

rst_n = 1;

#2

rst_n = 0;

#2

rst_n = 1;

end

rs232_diy u1

(

.clk (clk),

.rst_n (rst_n),

.data_over (data_over),

.data (data),

.en (en),

.data_need (data_need)

);

initial begin

data_over = 0;

#14

data = 8'hff;

#16

data_over = 1;

#1

data = 8'h11;

#1

data_over = 0;

#16

data_over = 1;

#2

data = 8'h22;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h01;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h11;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h22;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h33;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h44;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h55;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h66;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h77;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h88;

#2

data_over = 0;

#16

data_over = 1;

#2

data = 8'h99;

#2

data_over = 0;

end

endmodule

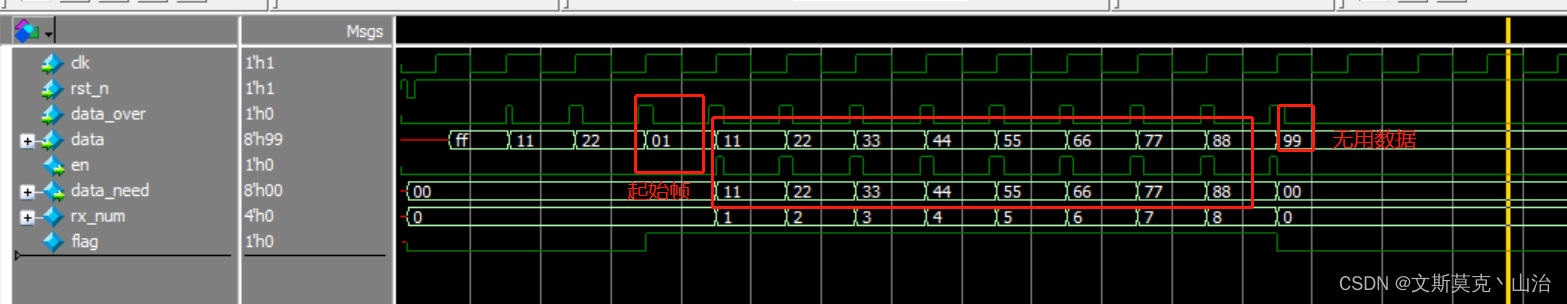

仿真结果: