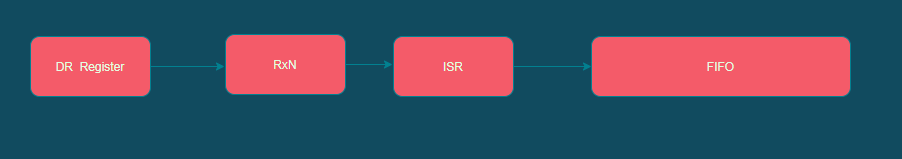

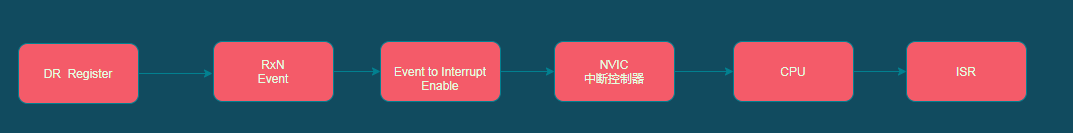

UART 模块接收数据 进入DR接收寄存器,RXN表示接收非空标志位在 中断使能的情况下会调转进入 ISR中断服务函数

到这里这些过程都是由MCU自己完成,其中中断使能有两重含义

1.CPU未屏蔽中断

2.RXN事件的中断使能

中断使能后,如果对应的事件发生那么对应的中断标志位被悬起,CPU会转为处理ISR。

实时系统应该在事先先定义的时间范围内识别和处理离散事件。

如果ISR没有及时的把数据从DR数据寄存器中搬运出去,那么下一个数据到来的时候,DR数据寄存器就会被覆盖。这样上一个DR数据寄存器的数据就会丢失,导致错失信息。这里就产生一个实时要求,产生RXN事件后,需要在下一个数据到来前取出DR寄存器上的数据。

1.尽快的进入到 ISR

2.ISR尽可能快速处理完成,以免下一个RXN事件到来时ISR还未处理完成任务。

第一点:ISR的进入受到中断使能的制约

第二点:ISR尽可能的快速处理完成,这样以免事情积压。或者其他低优先级中断无法得到相应。

这样对整个嵌入式系统的设计提出了要求:

CPU 尽可能快的响应ISR,CPU 禁止中断的时间要极可能短,非必要不要禁用中断。

同时处理ISR的过程中,低优先级的中断是无法运行的。所以ISR函数要尽可能的短。

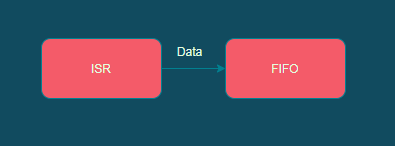

一般来说会把接收到的数据保存到FIFO BUFFER中(可以通过数组实现),这样数据就保存在了缓存数组中,实时性的需求被处理完成。

那么这个时候如何对数据进行处理,先思考一个问题

对数据的处理这件事的实时性,来看几个情景

1.数据代表当前的办公室室内气温

气温是一个变化缓慢的数据,这个数据可能显示屏幕上。路过的人看一下,知道今天的气温。

很显然这个数据的处理并不需要什么实时性。

2.数据代表 电动车当前的转速

很显然如果数据是提供给控制算法的,那么这个数据实时性就要高的多了。

数据有时候不是单个字节,需要组合为一串数据才有意义。

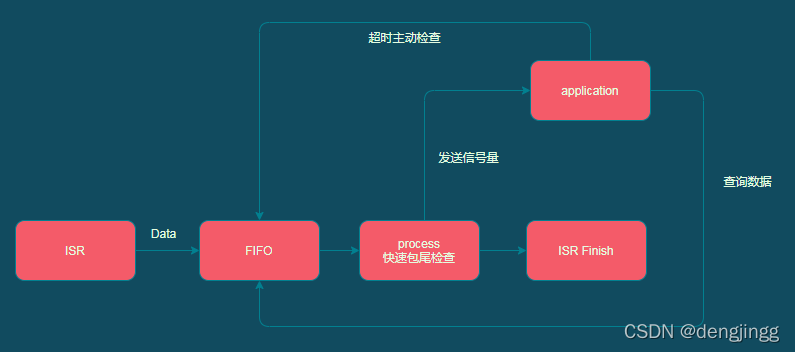

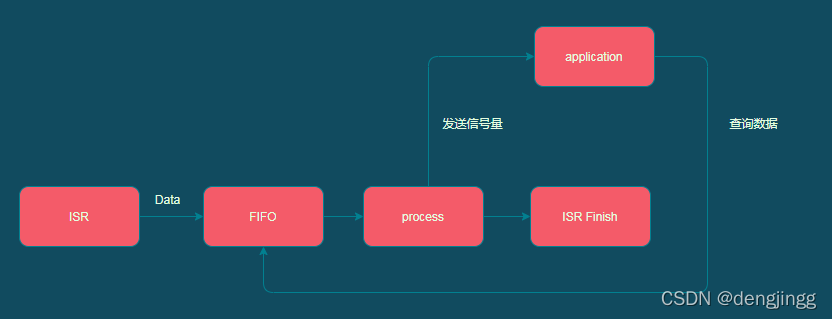

在process过程中去判断数据包是否完成,再去主动唤醒应用层处理数据。

或者process 每次接收到一个数据就去唤醒application,以便application能够最快的相应每个字节的数据。

1.process 本身需要耗费时间,增加ISR的开销

2.发送信号量本身是调用 操作系统,也会有相应的开销,甚至产生关中断的临界区。

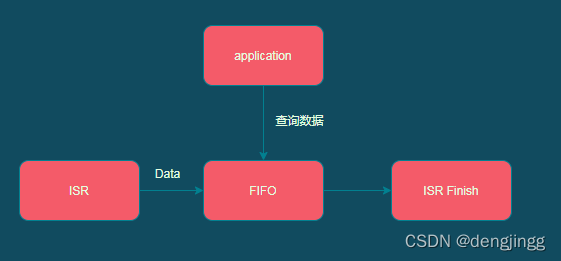

另外一种结构,如下

application task根据其任务的需求周期去读取FIFO的数据。ISR只做数据保存。

结合两者的优点,下图所示