ǰ��

��ʵ���Ǹ���AD/DA��֤ʵ��,��ʹ�ø���DAоƬʵ����ģת��,�������Ҳ�ģ���ѹ�ź�,��ͨ������ADоƬ��ģ���ź�ת���������źš���ʵ���õ���Ӳ���Ǻڽ�AX7020���������������ADDAģ�顪��AN108��

һ��ADDAģ�����

��ʵ����ʹ�õ�ADDAģ���ͺ�ΪAN108,��ģ������ͼ��ʾ��

����,ADC����������Ϊ32MHz,����Ϊ8λ,DAC����������Ϊ125MHz,����ҲΪ8λ��

��ADDAģ�鲻����AD IN�ڻ���DA OUT�ڶ���ͨ��BNC�ӿ���������ӵġ�

AN108��Ӳ���ṹͼ����ͼ��ʾ��

DA��·�ɸ���DAоƬAD9708��7�װ�����˹��ͨ�˲��������ȵ��ڵ�·���ź�����ӿ���ɡ�����DAоƬAD9708��8λ,125MSPS��DAת��оƬ,����1.2V�ο���ѹ,��ֵ��������AD9708оƬ�������Ժ�,Ϊ�˷�ֹ��������,��·�н�����7�װ�����˹��ͨ�˲���,�����Ϊ40MHz�����˲���֮��,������2Ƭ�����ܵ�145MHz�������˷�AD8056,��ʵ�ֲ�ֱ䵥�ˡ����ȵ��ڵȹ���,�Ӷ�ʹ��������·���ܵõ�����ȵ�����,���ȵ���ʹ�õ���5K�ĵ�λ��,������յ������Χ��-5V��5V,��10Vpp��

��Ҫע�����,���ڵ�·���ľ��Ȳ��Ǻܾ�ȷ,���յ������һ�����,�п��ܲ��η��Ȳ��ܴﵽ10Vpp,Ҳ�п��ܳ��ֲ�������������,��Щ�������������

AD��·�ɸ���ADоƬAD9280��˥����·���ź�����ӿ���ɡ�����DAоƬAD9280��8λ,32MSPS��ADת��оƬ�����źŽ���оƬAD9280֮ǰ,ʹ��һƬAD8056оƬ����˥����·,�ӿڵ����뷶Χ��-5V��5V,ͨ��˥����·�Ժ�,���뷶Χ����ADоƬ�����뷶Χ,��0~2V,��Ӧ��ת����ʽ���¡�

�ڽ�7020��������ADDAģ�����������ͼ��ʾ,�����������1��2�ź�39��40�Ŷ��ڿ������ϱ������,ADDAģ���1��2��Ҳ��ADDAģ���ϱ�ע������,����AN108��34��,���������������40��,���Ҫע�ⲻҪ�巴,�Ƚ�ADDAģ���1��2�źͿ������1��2�ſڶ���,�����δ������²��뼴�ɡ�

��������ROM IP��

�ⲿ�ֵ�ϸ�ڿ��Բο�����:ZYNQ֮FPGA Ƭ��ROM��д����ʵ����

���ȴ���һ����Ϊadda_test�Ĺ���,�¹��̻��ܵĽ�������ͼ��ʾ,���Finish������ɴ�����

�ڱ���ʵ����,�����Ҳ��IJ������ݴ洢��ROM��,������Ϊʵ���в�����Ҫд����(�����Ҫ,��Ҫ��RAM),Ȼ��ͨ����ȡROM�е�����,�̶�����DAת��оƬ���ɡ�

���ȴ�������������,ѡ�����ݳ���Ϊ256,����λ��Ϊ8,ѡ�����Ҳ�����,Ȼ�������档

�����ļ���ñ����ڹ���Ŀ¼��,ѡ��ĸ�ʽΪ.coe��

���û�в�������������,�������������

����������ROM IP��,��������Ϊrom_256x8b,����Ŀ����������ͼ��ʾ��

Basic��Ŀ���á�

Port A Options��Ŀ���á�

Other Options��Ŀ��,ѡ����س�ʼ�ļ�,�������汣���.coe�ļ���

��������ILA IP��

ILA�¸���Ŀ����������ͼ��ʾ��

������������̽��,�ֱ��������ad�����ݺ�da�����ݡ�

̽��λ������������ͼ��ʾ��

�ġ���д���Գ���

�½���Ϊadda_test��Verilog�ļ�,���ΰ�����ͼ�б�ע����Ž��м��ɡ�

���½��õ�adda_test.v�ļ���д�����´��롣

//��������������ԭ��

`timescale 1ns / 1ps

module adda_test(

input sys_clk , //ϵͳʱ��

input sys_rst_n , //ϵͳ��λ,�͵�ƽ��Ч

//DAоƬ�ӿ�

output da_clk , //DA(AD9708)����ʱ��,���֧��125Mhzʱ��

output [7:0] da_data , //�����DA������

//ADоƬ�ӿ�

input [7:0] ad_data , //AD��������

//ģ�������ѹ�������̱�־(��������δ�õ�)

//input ad_otr , //0:�����̷�Χ 1:��������

output ad_clk //AD(AD9280)����ʱ��,���֧��32Mhzʱ��

);

//wire define

wire [7:0] rd_addr; //ROM����ַ

wire [7:0] rd_data; //ROM����������

//DA���ݷ���

da_wave_send u_da_wave_send(

.clk (sys_clk),

.rst_n (sys_rst_n),

.rd_data (rd_data),

.rd_addr (rd_addr),

.da_clk (da_clk),

.da_data (da_data)

);

//ROM�洢����

rom_256x8b u_rom_256x8b (

.clka (sys_clk), // input wire clka

.addra (rd_addr), // input wire [7 : 0] addra

.douta (rd_data) // output wire [7 : 0] douta

);

//AD���ݽ���

ad_wave_rec u_ad_wave_rec(

.clk (sys_clk),

.rst_n (sys_rst_n),

.ad_data (ad_data),

// .ad_otr (ad_otr),

.ad_clk (ad_clk)

);

//ILA�ɼ�AD����

ila_0 ila_0 (

.clk (ad_clk ), // input wire clk

.probe0 (da_data), // input wire [7:0] probe0

.probe1 (ad_data) // input wire [7:0] probe0

);

endmodule

ͬ���ķ����½���Ϊda_wave_send.v���ļ���д�����´��롣

//��������������ԭ��

module da_wave_send(

input clk , //ʱ��

input rst_n , //��λ�ź�,�͵�ƽ��Ч

input [7:0] rd_data, //ROM����������

output reg [7:0] rd_addr, //��ROM��ַ

//DAоƬ�ӿ�

output da_clk , //DA(AD9708)����ʱ��,���֧��125Mhzʱ��

output [7:0] da_data //�����DA������

);

//parameter Ƶ�ʵ��ڿ���

parameter FREQ_ADJ = 8'd5; //Ƶ�ʵ���,FREQ_ADJ��ֵԽ��,���������Ƶ��Խ��,��Χ0~255

//reg define

reg [7:0] freq_cnt ; //Ƶ�ʵ��ڼ�����

//����rd_data����clk�������ظ��µ�,����DAоƬ��clk���½��������������ȶ���ʱ��

//��DAʵ������da_clk����������������,����ʱ��ȡ��,����clk���½����൱��da_clk��������

assign da_clk = ~clk;

assign da_data = rd_data; //��������ROM���ݸ�ֵ��DA���ݶ˿�

//Ƶ�ʵ��ڼ�����

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

freq_cnt <= 8'd0;

else if(freq_cnt == FREQ_ADJ)

freq_cnt <= 8'd0;

else

freq_cnt <= freq_cnt + 8'd1;

end

//��ROM��ַ

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

rd_addr <= 8'd0;

else begin

if(freq_cnt == FREQ_ADJ) begin

rd_addr <= rd_addr + 8'd1;

end

end

end

endmodule

���½���Ϊad_wave_rec.v���ļ���д�����´��롣

//��������������ԭ��

module ad_wave_rec(

input clk , //ʱ��

input rst_n , //��λ�ź�,�͵�ƽ��Ч

input [7:0] ad_data , //AD��������

//ģ�������ѹ�������̱�־(��������δ�õ�)

input ad_otr , //0:�����̷�Χ 1:��������

output reg ad_clk //AD(AD9280)����ʱ��,���֧��32Mhzʱ��

);

//ʱ�ӷ�Ƶ(2��Ƶ,ʱ��Ƶ��Ϊ25Mhz),����ADʱ��

always @(posedge clk or negedge rst_n) begin

if(rst_n == 1'b0)

ad_clk <= 1'b0;

else

ad_clk <= ~ad_clk;

end

endmodule

������,��ʵ��IJ��Դ������������ˡ�

�塢�ܽŷ���

ADDAģ�顪��AN108��34���Ų���ԭ��ͼ���¡�

�ڽ����J11��չ��ԭ��ͼ���¡�

����,J11��չ������Ӧ�����ź����±���ʾ��

| J11�ܽ� | �ź����� | ZYNQ������ | ZYNQ���ź� |

|---|---|---|---|

| PIN1 | GND | - | - |

| PIN2 | +5V | - | - |

| PIN3 | EX_IO2_1N | IO_L6N_T0_35 | F17 |

| PIN4 | EX_IO2_1P | IO_L6P_T0_35 | F16 |

| PIN5 | EX_IO2_2N | IO_L15N_T2_35 | F20 |

| PIN6 | EX_IO2_2P | IO_L15P_T2_35 | F19 |

| PIN7 | EX_IO2_3N | IO_L18N_T2_35 | G20 |

| PIN8 | EX_IO2_3P | IO_L18P_T2_35 | G19 |

| PIN9 | EX_IO2_4N | IO_L14N_T2_35 | H18 |

| PIN10 | EX_IO2_4P | IO_L14P_T2_35 | J18 |

| PIN11 | EX_IO2_5N | IO_L9N_T1_35 | L20 |

| PIN12 | EX_IO2_5P | IO_L9P_T1_35 | L19 |

| PIN13 | EX_IO2_6N | IO_L7N_T1_35 | M20 |

| PIN14 | EX_IO2_6P | IO_L7P_T1_35 | M19 |

| PIN15 | EX_IO2_7N | IO_L12N_T1_35 | K18 |

| PIN16 | EX_IO2_7P | IO_L12P_T1_35 | K17 |

| PIN17 | EX_IO2_8N | IO_L10N_T1_35 | J19 |

| PIN18 | EX_IO2_8P | IO_L10P_T1_35 | K19 |

| PIN19 | EX_IO2_9N | IO_L17N_T2_35 | H20 |

| PIN20 | EX_IO2_9P | IO_L17P_T2_35 | J20 |

| PIN21 | EX_IO2_10N | IO_L11N_T1_35 | L17 |

| PIN22 | EX_IO2_10P | IO_L11P_T1_35 | L16 |

| PIN23 | EX_IO2_11N | IO_L8N_T1_35 | M18 |

| PIN24 | EX_IO2_11P | IO_L8P_T1_35 | M17 |

| PIN25 | EX_IO2_12N | IO_L4N_T0_35 | D20 |

| PIN26 | EX_IO2_12P | IO_L4P_T0_35 | D19 |

| PIN27 | EX_IO2_13N | IO_L5N_T0_35 | E19 |

| PIN28 | EX_IO2_13P | IO_L5P_T0_35 | E18 |

| PIN29 | EX_IO2_14N | IO_L16N_T2_35 | G18 |

| PIN30 | EX_IO2_14P | IO_L16P_T2_35 | G17 |

| PIN31 | EX_IO2_15N | IO_L13N_T2_35 | H17 |

| PIN32 | EX_IO2_15P | IO_L13P_T2_35 | H16 |

| PIN33 | EX_IO2_16N | IO_L19N_T3_35 | G15 |

| PIN34 | EX_IO2_16P | IO_L19P_T3_35 | H15 |

| PIN35 | EX_IO2_17N | IO_L20N_T3_35 | J14 |

| PIN36 | EX_IO2_17P | IO_L20P_T3_35 | K14 |

| PIN37 | GND | - | - |

| PIN38 | GND | - | - |

| PIN39 | +3.3V | - | - |

| PIN40 | +3.3V | - | - |

����������еĶ�Ӧ��ϵ,�ܽ�����ҳ���������ü��ɡ�

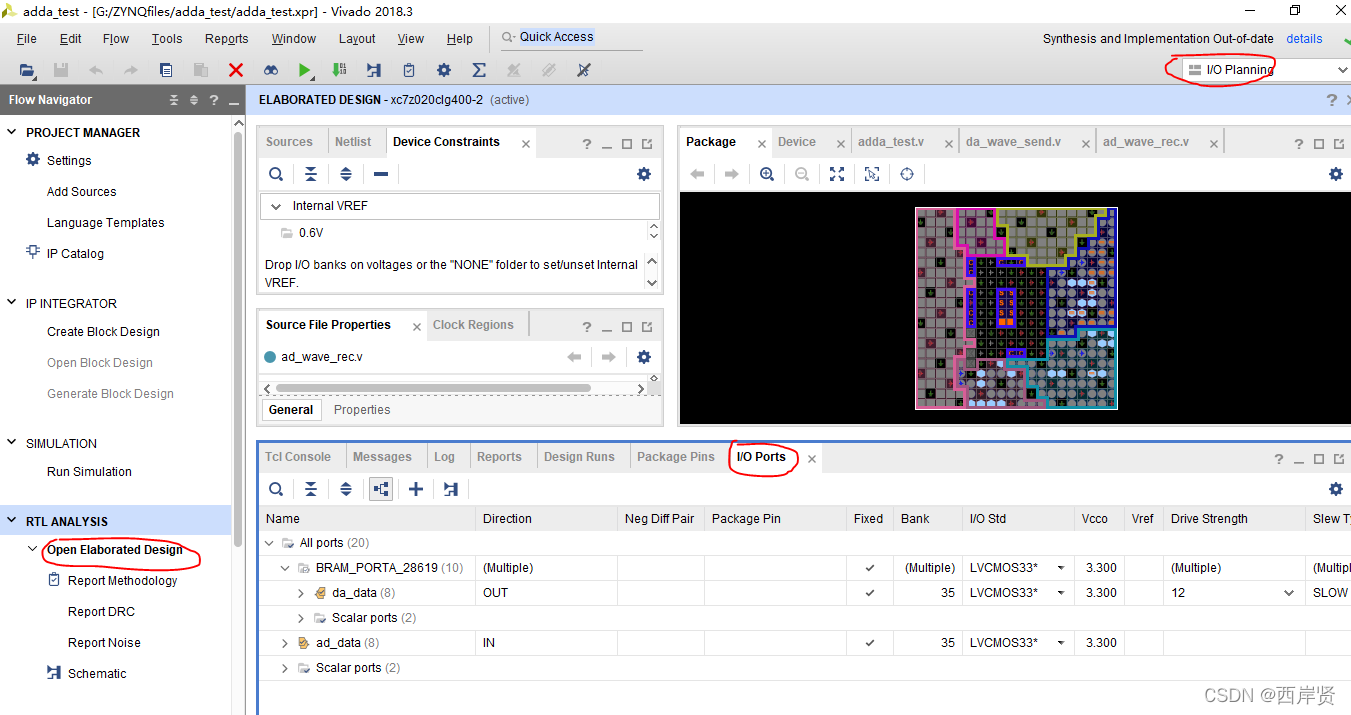

�������ӿ��������

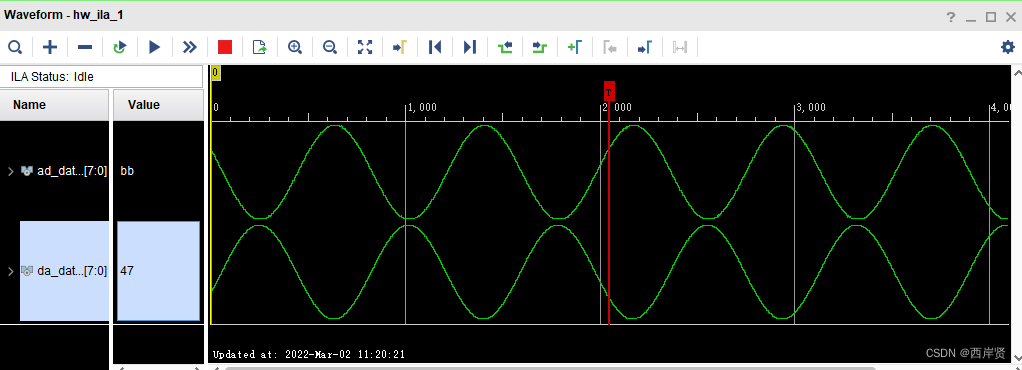

���ӿ�����,���Generate Bitstream���ɱ������ļ�,�������ص���������,��ILA�������к�õ�����ͼ��ʾ�����Ҳ���

����ͼ���Կ���,�����ad_data���������Ҳ��IJ���,˵����ʵ����֤�ɹ��ˡ�

����˵�������ģת��������Ҫ��ʾ��������,����IJ��������ǽ�ʾ���������ӵ�һ�����ӿ������GND��(�������������GND����),Ȼ��ʾ������һ��̽��ӵ�DAͨ����,���������������ƾ�����ILA������ʾ����,�����Ҳ�����Ҳ���

�ܽ�

���Ͼ���ZYNQ֮����AD/DA��֤ʵ�������������,��ʵ����ROM��д����ʵ����һ��������֮��,ͬʱҲ����������Ͻ��и����ӵ�ʵ��,��ʵ����Ҫע�����ADDAģ���ڲ��뿪����ʱ��Ҫ�巴,ͬʱ�ڹܽŷ���ʱҲҪע�ⲻҪ������

���IJ����:

����ԭ�ӨCcourse_s1_ZYNQ��Щ�¶�-FPGAʵ��ƪV1.06.pdf

ALINX�ڽ�AX7020�������û��ֲ�V2.2.pdf

�캽��ZYNQ֮FPGA����ָ��_V2.0 .pdf