�жϺ��쳣

ָ�ڵ�ǰִ�г����ij������һ���¼�,���¼���Ҫ���������д�����ͨ��,��������ᵼ�´ӵ�ǰ���г���ת�Ƶ�����Ϊ�жϴ������쳣�����ij����С�

һ.�쳣������

ϵͳ���

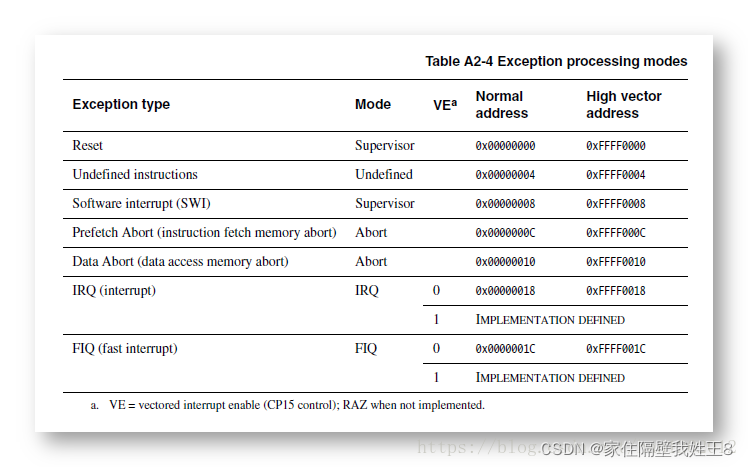

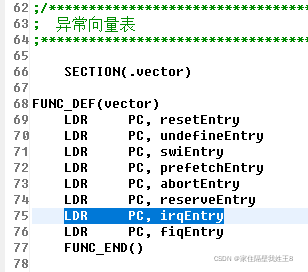

ARM(AArch32)�ܹ��ж�������

1.Reset :

�������ڹ���ʱ, ͻȻ����������, �ͻᴥ�����쳣;

2.Undefined instructions :

������ִ�е�ָ�����й淶��, �������ִ�в�����Ҫ���ָ��, �ͻ���뵽���쳣;

3.Software interrupt :

���ж�, ��������Ҫȥ��ϴ���������, ����ʹ�����ж���ִ��;

4.Prefetch Abort :

ARM ��ִ��ָ��Ĺ�����, Ҫ��ȥԤȡָ����ִ��, ���Ԥȡָ��ʧ��, �ͻ�������쳣;

5.Data :

��ȡ����ʧ��;

6.IRQ:

��ͨ�ж�;

7.FIQ :

�����ж�, �����ж�Ҫ����ͨ�ж���Ӧ�ٶ�Ҫ��һЩ;

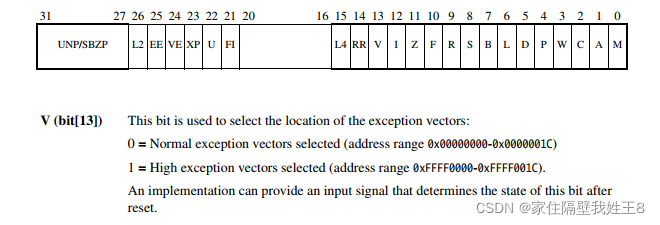

(AArch32)�쳣������ͨ����0x00000000,Ҳ������0xffff0000

���ĸ���ַ��cp15����

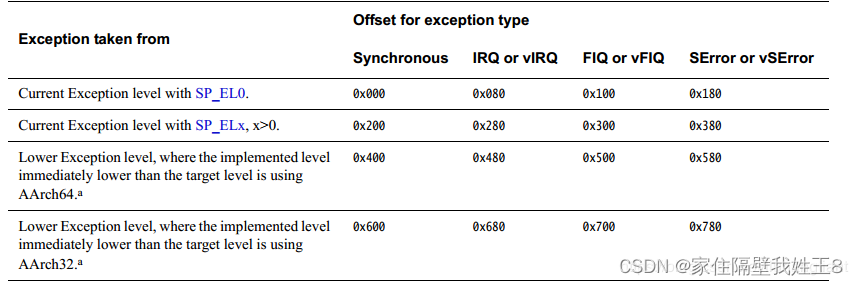

ARM64(AArch64)�ܹ��쳣������

�쳣�������ṹ:

ʵ���������ű�,ÿ�ű����ĸ��쳣���,�ֱ��Ӧͬ���쳣,IRQ,FIQ �� �����쳣��

ÿһ���쳣��ڲ��ٽ���ռ�� 4bytes �Ŀռ�,����ռ�� 0x80 bytes�ռ�,Ҳ����˵,ÿһ���쳣��ڿ��Է��ö���ָ��,����������һ����תָ��

��ARM32��,ÿ����������Ӧ�ĸ��ֽ�,ÿ�ĸ��ֽڶ�Ӧһ��ָ�ARM32��ڶ�Ӧ0,ÿ��ָ���Ӧ�ĸ��ֽ�,�ɼ���ƫ������

��ARM64��,������������ָ����ú��˵�ַ��

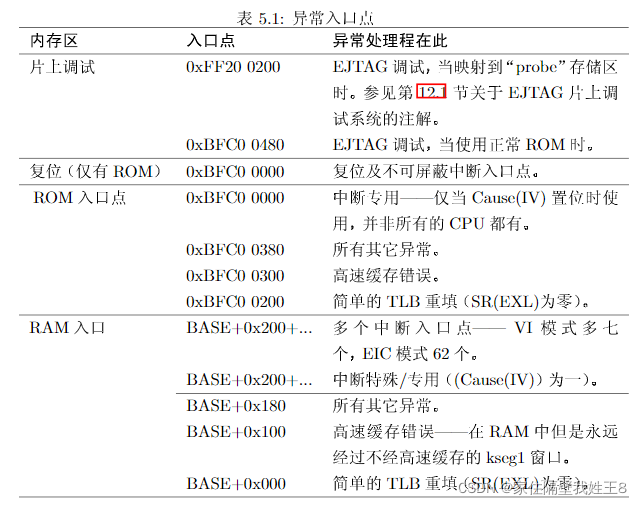

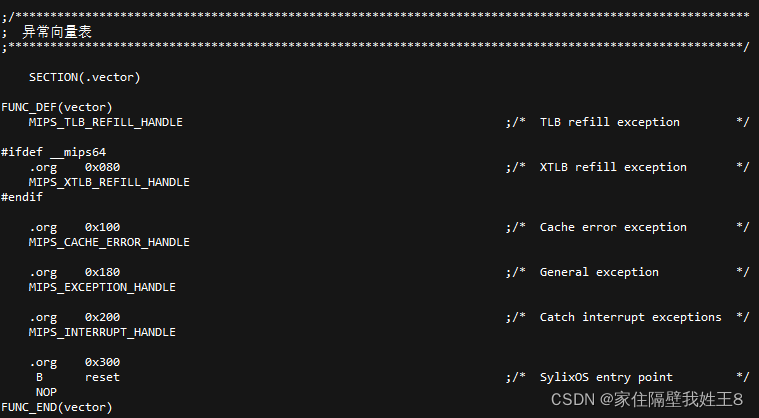

MIPS32�ܹ��쳣������

�쳣���������õ�����ڵ�ַ

�������ṹ,�����֧,�ӵ�����Ϣ,֪����������ڡ�

��.�жϴ�������

�����ж�,��ʱ���ж϶���IRQ�ж�

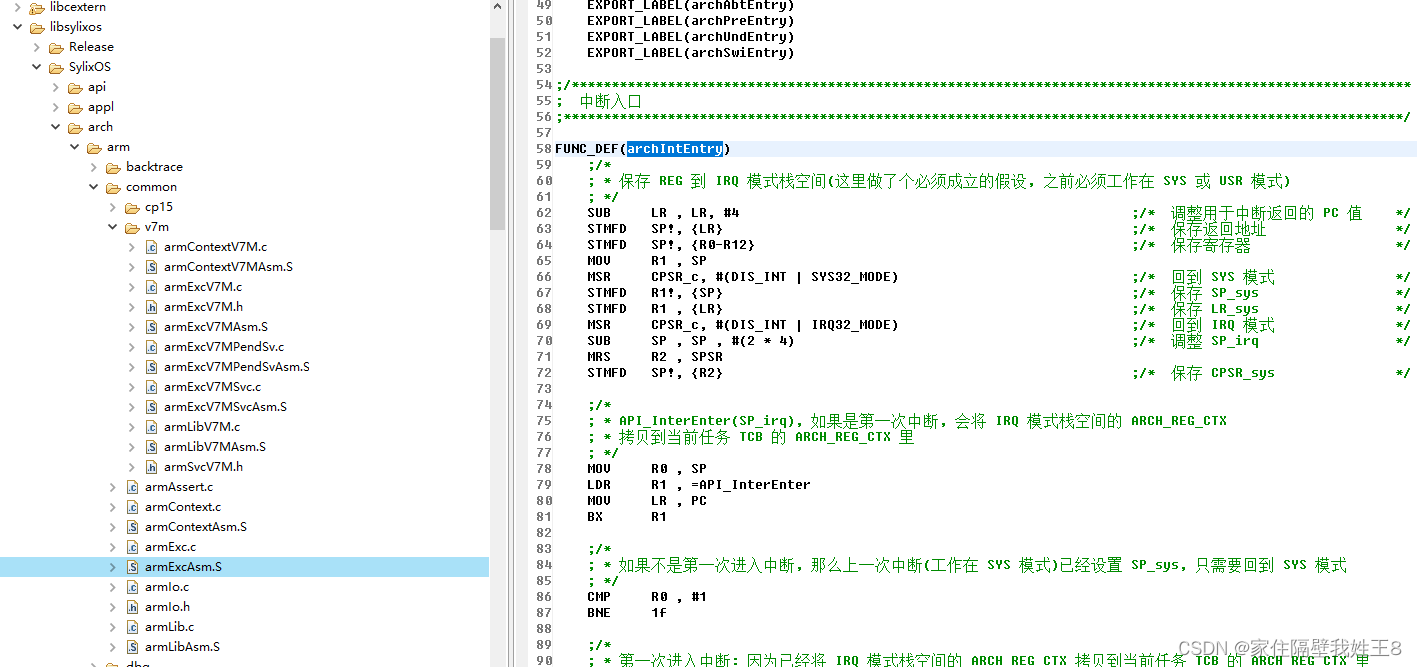

����IRQ�жϺ�,pcָ�������Ļ�������������archIntEntry

���������������archIntEntry(��base��)

��ͬģʽ��Ӧ��ͬ��ջλ��

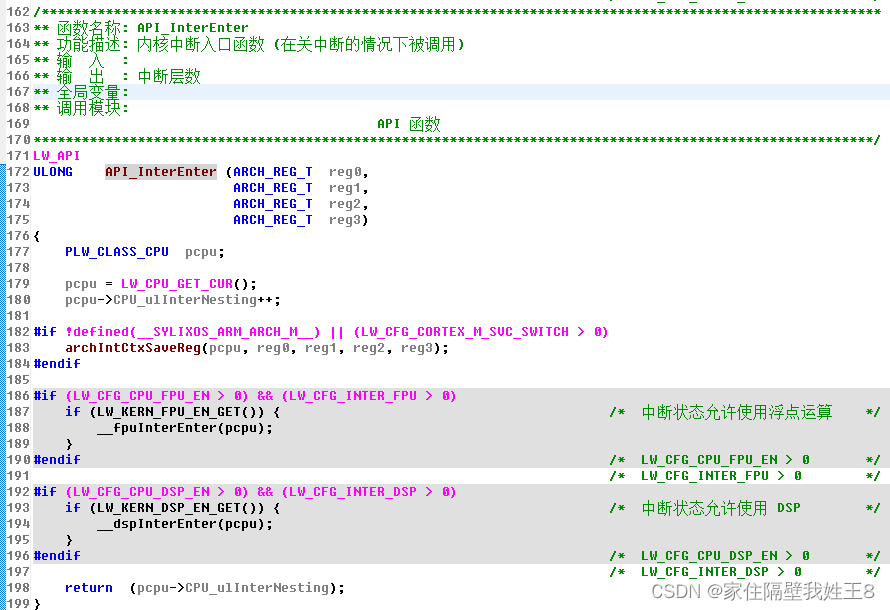

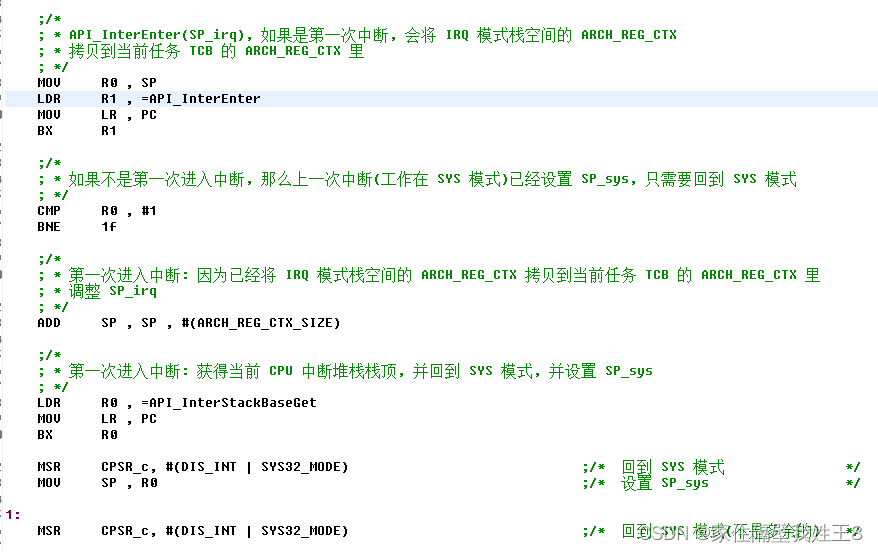

��һ����cpu��ؼĴ�������ջ��,�ڶ�������ϵͳ����õ��жϽ��뺯����(API_InterEnter)

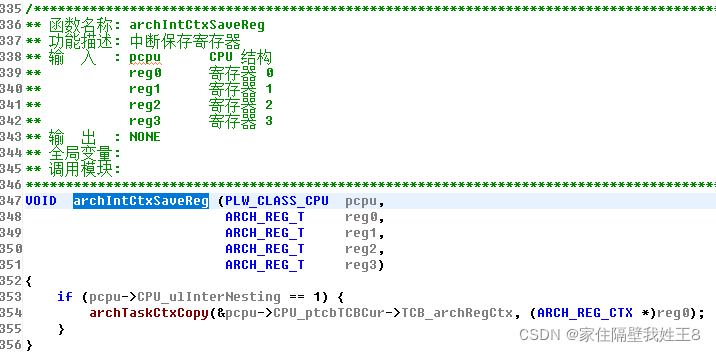

�ж���ں���API_InterEnter�����ж�Ƕ��ֵCPU_ulInterNesting++,Ȼ�����archIntCtxSaveReg

archIntCtxSaveReg������һ���жϱ���Ĵ���

���������������һ�ο���(archTaskCtCopy����),ǰ���ж����archIntEntry��Ҳ���˿���

����Ŀ����ٰ��жϴ洢��������ƿ�TCB��

���쳣����(��������ж����),�������ȴ���IRQ��Ӧ��ջλ��(��ʱ����)��

�ڶ��α���ʱ,�洢����Ӧ�����ĵ�������ƿ�TCB��(archTaskCtCopy����)��

�����α�������������������̡�

�ж��Dz��ǵ�һ�ν����ж�

��һ�ν����ж�,��ȡCPU�ж϶�ջ(���ǵ�һ�β����ж�,������ж�Ƕ��)

�ܽ�:1.���浽��ʱ��IRQ��Ӧ��ջλ�á�2.�����ı��浽TCB�С�3.����������������жϴ�����ջ������λ�á�4.���������������ж����̡�

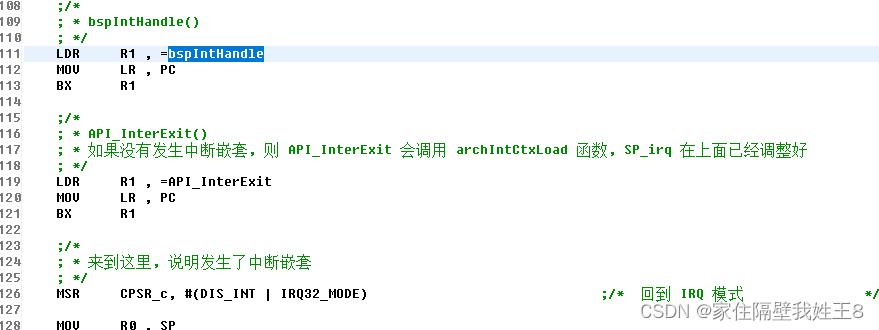

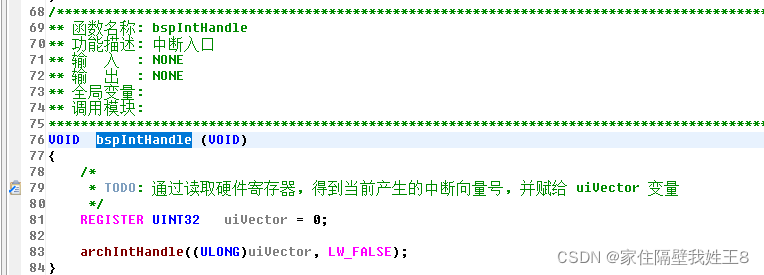

bspIntHandle�����жϵĺ���(bspLib.c�е�bspIntHandle����)

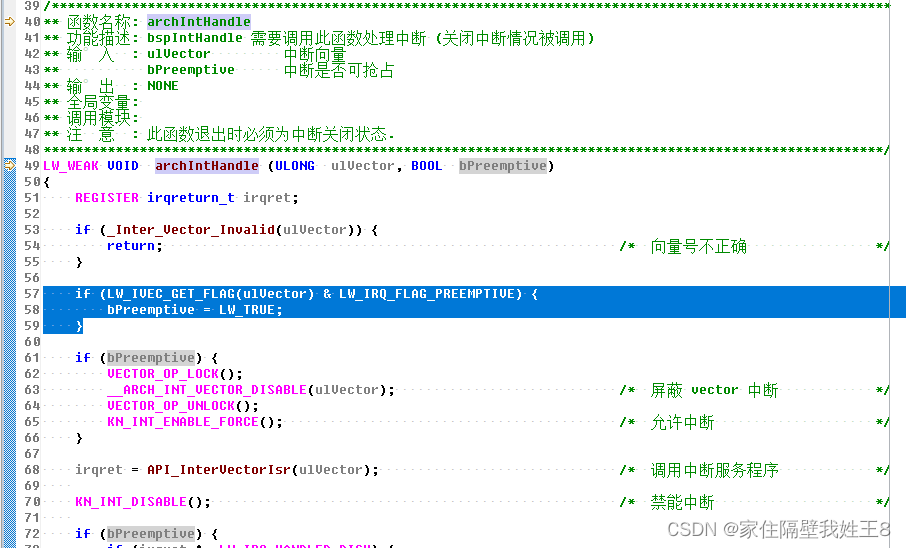

��������л�ȡ�жϺŲ�����archIntHandle

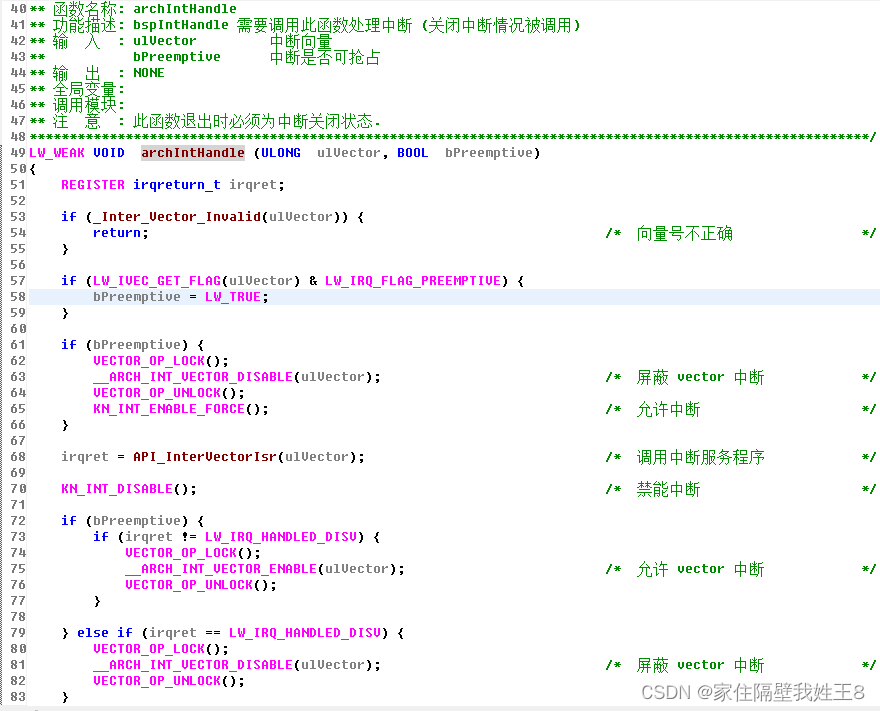

archIntHandle�����ֻص�BASE�еĴ���

���ж��жϺ��Ƿ�Ϸ�;Ȼ���ж��жϺ��Ƿ����ռ;�������ռ�ᷢ��Ƕ��,������ռ����API_InterVectorIsr�ж��ܷ�������

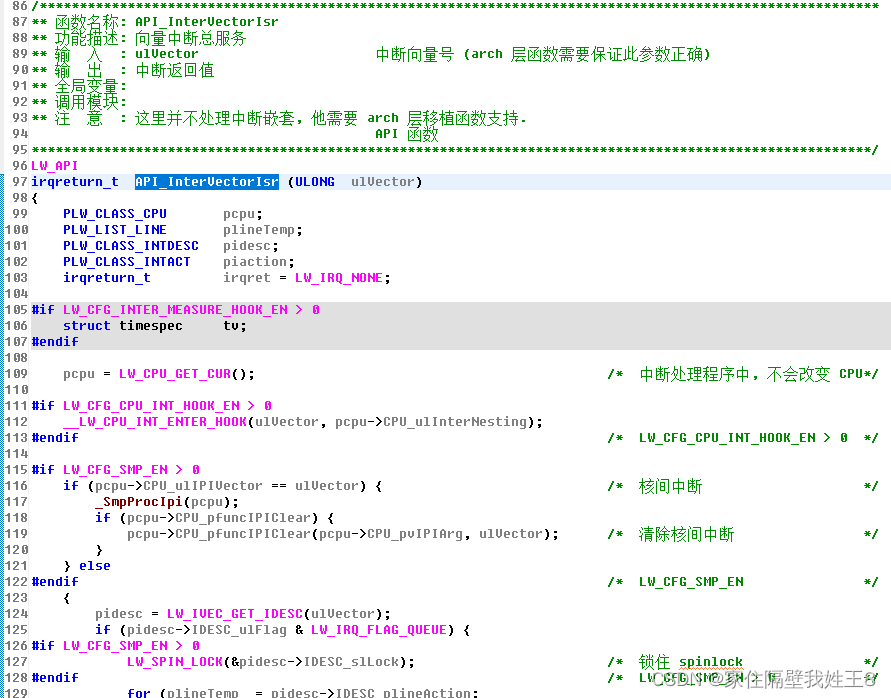

����API_InterVectorIsr�ж��ܷ�����

��������л�����жϺŵ��������ж�����жϷ������,����жϷ���ֵ��

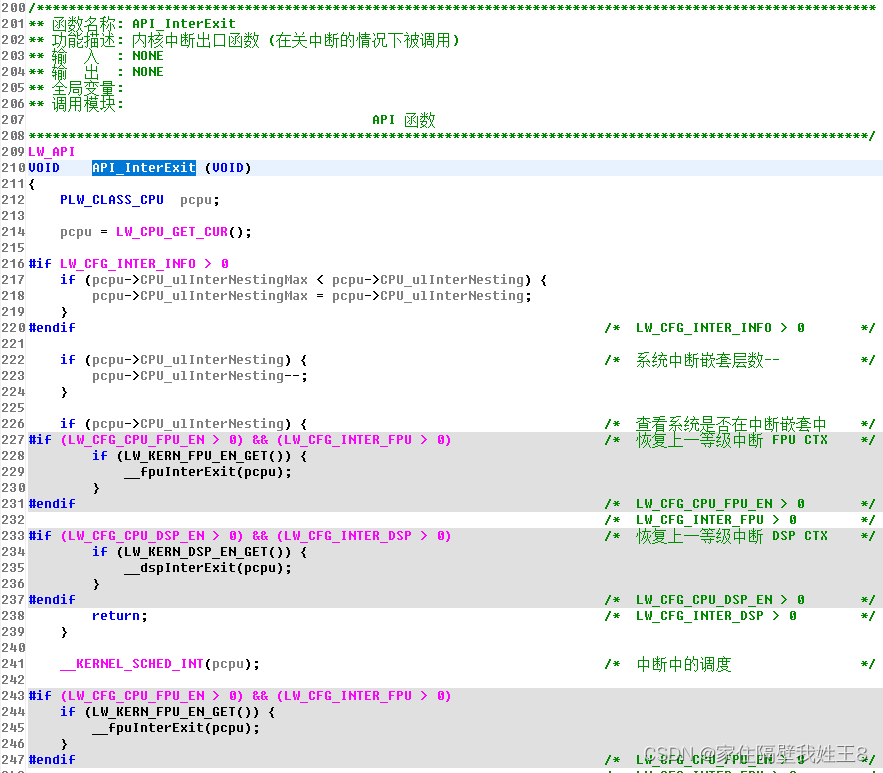

���ִ���ж��˳�API_InterExit����

�ж�Ƕ��ֵCPU_ulInterNesting�C(�ɸ������ֵ���ж���Щ�����Ƿ����ж��е���)

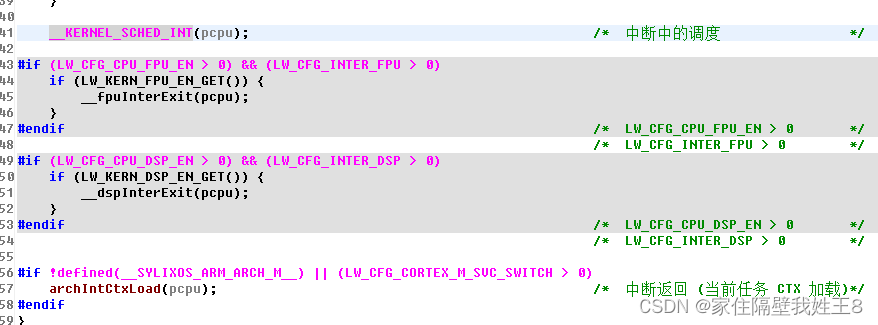

ִ���жϵ���,�ж��˳�֮ǰ,�ڵ��ȱ��ҳ���Ӧ�õ��ȵ�����

ִ���жϷ���,�����Ǹ���Ӧ�õ��ȵ�����,���������ġ�

�����ж�ǰҪ����������,�жϷ��غ�ָ�������(�ָ��������IJ�һ����֮ǰ�����������һ��,��Ϊ�ж��˳������л�ִ���жϵ���,�ҳ���Ӧ��ִ�е�����Ȼ��)��

�жϴ��������ܽ�:

1.archIntEntry �����������ת��λ�á������ı��浽 IRQ ģʽջ�С�

2.API_InterEnter ���ж�Ƕ�������ӡ��� IRQ ģʽջ�еļĴ�����Ϣ���浽 TCB �������С�

3.bspIntHandle ���жϿ������л�ȡ�жϺš�����ע��õ��жϷ������

4.API_InterExit ���ж�Ƕ�������١����ȡ��ָ�������

API_InterStackBaseGet

�жϵĴ���������ָ����ջ����;

��ͳ���ж϶�ջ��ʹ����(flag)

bspIntHandle(��Ҫʵ�ֵĺ���,��ͬ�жϴ��������̲�ͬ)

��ͬ�жϿ������������̲�ͬ

���� archIntHandle,�Ƿ�Ƕ��

API_InterExit

�ж��еĵ��Ƚӿ�

�ж������ĵĻָ�

�ж�Ƕ������:

�Ƚ��õ�ǰ�жϵ��жϺ�(���ǰ�жϺ��ٲ����ж�),Ȼ����������жϺš������жϽ���ʱ,���ж��Dz��ǵ�һ���ж�(�����ж�Ƕ��ֵ),Ȼ�����ж��������������ơ����ж��˳�ʱ�����������жϲ�ͬ,Ƕ���жϲ���ص����ȵ�������ǻص���һ���жϡ�

�ж�Ƕ��(���ȼ��ߵ��жϻ���ռ���ȼ��͵��ж�)

1.�ж�Ƕ������ʱ��

archIntHandle ����> API_InterVectorIsr

2.�ж�Ƕ��ջʹ�õı仯

����ʹ�õ�ǰIRQģʽջ

3.�ж�Ƕ�ķ���

�������,������쳣����������,���ǻص���һ���쳣λ��

�˼��ж�:���Լ��Ĵ�����֧_SmpProclpi(���)

��ͨ�ж�:�����жϺ�,�ҵ���Ӧ�жϷ������

��ʽ�ж�:�����жϺ�,�����жϷ������,�жϷ���ֵ

������ʽ�жϵķ���:

API_InterVectorSetFlag(LW_IRQ_4, LW_IRQ_FLAG_QUEUE);

��.�жϿ�������ʵ��

bspIntInit �жϿ������ij�ʼ��

bspIntVectorEnable/bspIntVectorDisable �ж�ʹ��/�жϽ���(��ӦMASK�Ĵ���)

bspIntVectorSetPriority/bspIntVectorGetPriority �ж����ȼ�����/�ж����ȼ���ȡ

bspIntVectorSetTarget/bspIntVectorGetTarget �жϰ������/�жϰ�˻�ȡ

bspMpInt �˼��жϴ���

S3C2440���жϿ����� ����,�ṹ��

ARM GIC V1,V2 Distributor+CPU Interface

ARM GIC V3,V4

���ж�

KN_INT_DISABLE/KN_INT_ENABLE

Disable IRQ Interrupts

��˴�����,ÿ���˶����Լ���Iλ

���ж�ֻ�ǹرձ��˵��ж�

2440�жϽӿ�ʵ��

/*********************************************************************************************************

����

*********************************************************************************************************/

/*********************************************************************************************************

** ��������: bspIntInit

** ��������: �ж�ϵͳ��ʼ��

** �� �� : NONE

** �� �� : NONE

** ȫ�ֱ���:

** ����ģ��:

*********************************************************************************************************/

VOID bspIntInit (VOID)

{

API_InterVectorSetFlag(LW_IRQ_4, LW_IRQ_FLAG_QUEUE); /* EINT 4 ~ 7 */

API_InterVectorSetFlag(LW_IRQ_5, LW_IRQ_FLAG_QUEUE); /* EINT 8 ~ 23 */

API_InterVectorSetFlag(LW_IRQ_0, LW_IRQ_FLAG_SAMPLE_RAND); /* EINT 0 used to sample random*/

}

/*********************************************************************************************************

** ��������: bspIntHandle

** ��������: ����

** �� �� : NONE

** �� �� : NONE

** ȫ�ֱ���:

** ����ģ��:

*********************************************************************************************************/

VOID bspIntHandle (VOID)

{

REGISTER UINT32 uiIrqVic = rINTOFFSET;

archIntHandle((ULONG)uiIrqVic, LW_FALSE);

}

/*********************************************************************************************************

** ��������: bspIntVectorEnable

** ��������: ʹ��ָ�����ж�����

** �� �� : ulVector �����

** �� �� : NONE

** ȫ�ֱ���:

** ����ģ��:

*********************************************************************************************************/

VOID bspIntVectorEnable (ULONG ulVector)

{

INTER_CLR_MSK((1u << ulVector));

}

/*********************************************************************************************************

** ��������: bspIntVectorDisable

** ��������: ����ָ�����ж�����

** �� �� : ulVector �����

** �� �� : NONE

** ȫ�ֱ���:

** ����ģ��:

*********************************************************************************************************/

VOID bspIntVectorDisable (ULONG ulVector)

{

INTER_SET_MSK((1u << ulVector));

}

/*********************************************************************************************************

** ��������: bspIntVectorIsEnable

** ��������: ���ָ�����ж������Ƿ�ʹ��

** �� �� : ulVector �����

** �� �� : LW_FALSE �� LW_TRUE

** ȫ�ֱ���:

** ����ģ��:

*********************************************************************************************************/

BOOL bspIntVectorIsEnable (ULONG ulVector)

{

return (INTER_GET_MSK((1u << ulVector)) ? LW_FALSE : LW_TRUE);

}

/*********************************************************************************************************

** ��������: bspIntVectorSetPriority

** ��������: ����ָ�����ж����������ȼ�

** �� �� : ulVector �������

** uiPrio ���ȼ�

** �䡡�� : ERROR CODE

** ȫ�ֱ���:

** ����ģ��:

*********************************************************************************************************/

#if LW_CFG_INTER_PRIO > 0

ULONG bspIntVectorSetPriority (ULONG ulVector, UINT uiPrio)

{

return (ERROR_NONE);

}

/*********************************************************************************************************

** ��������: bspIntVectorGetPriority

** ��������: ��ȡָ�����ж����������ȼ�

** �� �� : ulVector �������

** puiPrio ���ȼ�

** �䡡�� : ERROR CODE

** ȫ�ֱ���:

** ����ģ��:

*********************************************************************************************************/

ULONG bspIntVectorGetPriority (ULONG ulVector, UINT *puiPrio)

{

*puiPrio = 0;

return (ERROR_NONE);

}

#endif /* LW_CFG_INTER_PRIO > 0 */

/*********************************************************************************************************

** ��������: bspIntVectorSetTarget

** ��������: ����ָ�����ж�������Ŀ�� CPU

** �䡡�� : ulVector �ж�������

** stSize CPU ���뼯�ڴ��С

** pcpuset CPU ����

** �䡡�� : ERROR CODE

** ȫ�ֱ���:

** ����ģ��:

*********************************************************************************************************/

#if LW_CFG_INTER_TARGET > 0

ULONG bspIntVectorSetTarget (ULONG ulVector, size_t stSize, const PLW_CLASS_CPUSET pcpuset)

{

return (ERROR_NONE);

}

/*********************************************************************************************************

** ��������: bspIntVectorGetTarget

** ��������: ��ȡָ�����ж�������Ŀ�� CPU

** �䡡�� : ulVector �ж�������

** stSize CPU ���뼯�ڴ��С

** pcpuset CPU ����

** �䡡�� : ERROR CODE

** ȫ�ֱ���:

** ����ģ��:

*********************************************************************************************************/

ULONG bspIntVectorGetTarget (ULONG ulVector, size_t stSize, PLW_CLASS_CPUSET pcpuset)

{

LW_CPU_ZERO(pcpuset);

LW_CPU_SET(0, pcpuset);

return (ERROR_NONE);

}

#endif /* LW_CFG_INTER_TARGET > 0 */

��.�����쳣�Ĵ�������

1.�����쳣ʱ�������ı��档�ɷ������͵��쳣�ķ���

2.δ�����쳣��FPU�Ĺ�ϵ

3.�쳣����ʱ����Ϣ����

δ�����쳣��FPU