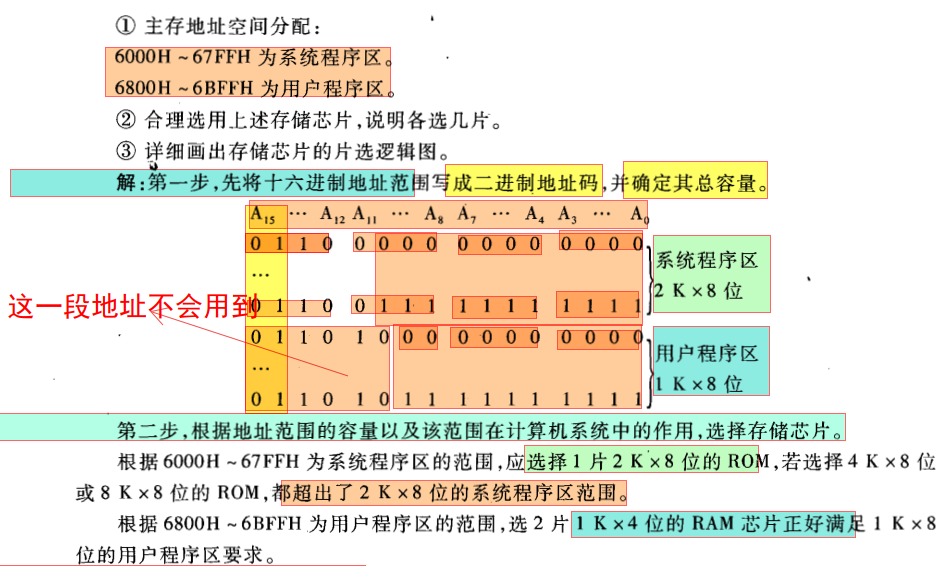

存储芯片的译码驱动方式和字位扩展案例

半导体存储芯片的译码驱动方式

- 半导体存储芯片的译码驱动方式有两种:

线选法和重合法

线选法

- 它的特点是用一根

字选择线(字线),直接选中一个存储单元的各位(如一个字节的各个位)。 - 这种方式结构较简单,但只适于容量不大的存储芯片。

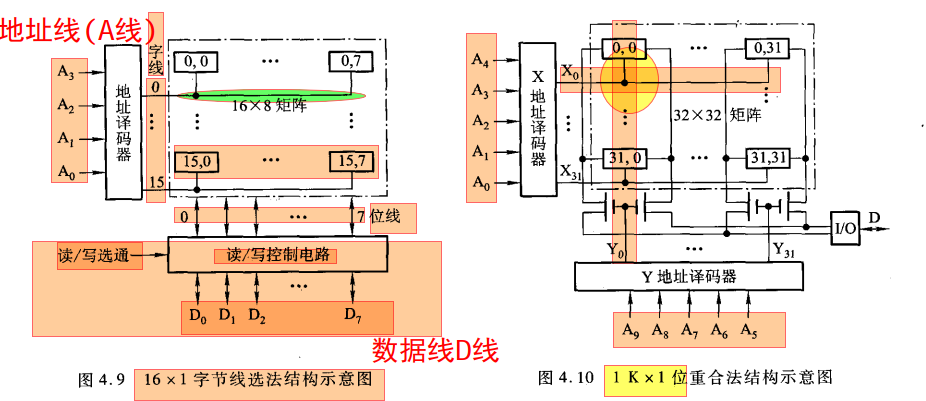

- 4.19 是一个 16×1

字节线选法存储芯片的结构示意图。 - 如当地址线 A 3 A 2 A 1 A 0 A_{3}A_{2}A_{1}A_{0} A3?A2?A1?A0? 为 1111 时,则第 15 根字线被选中,对应下图中的最后一行 8 位代码便可直接读出或写入。

- 4.19 是一个 16×1

重合法

- 由于被选单元是由 X、Y 两个方向的地址决定的,故称为重合法。

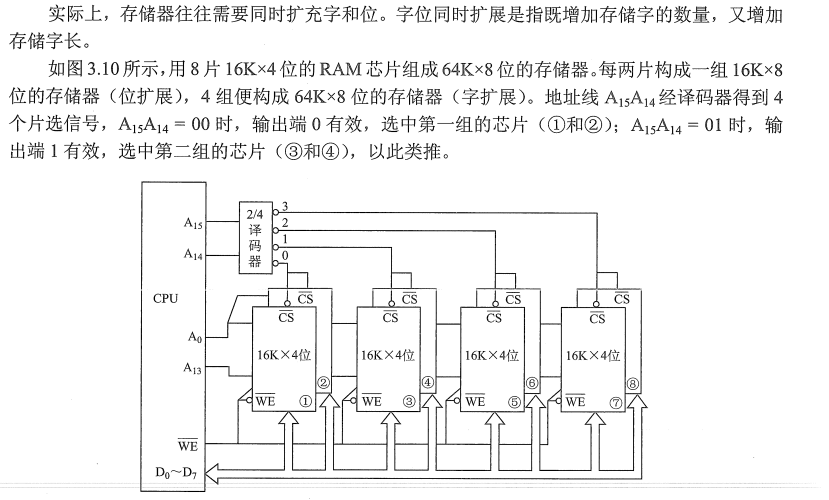

- 4.10 是一个 1K×1 位重合法结构示意图。

- 显然,只要用 64 根选择线(X、Y 两个方向各 32 根),便可选择 32×32 矩阵中的

任一位。 - 例如,当地址线为全 0 时,译码输出 X。和 Y。有效,矩阵中第 0 行、第 О 列共同选中的那位即被选中。

- 当欲构成 1K×1 字节的存储器时,只需用 8 片即可。

存储器与 CPU 的连接

合理选择存储芯片

要组成一个主存系统,选择存储芯片是第一步,主要指存储芯片的类型(RAM 或 ROM)和数量的选择。

通常选用 ROM 存放系统程序、标准子程序和各类常数,RAM 则是为用户编程而设置的。

此外,在考虑芯片数量时,要尽量使连线简单、方便。

地址线的连接

- 存储芯片的容量不同,其地址线数也不同,而 CPU 的地址线数往往比存储芯片的地址线数要多。

- 通常将 CPU 地址线的

低位与存储芯片的地址线相连,以选择芯片中的某一单元(字选),这部分的译码是由芯片的片内逻辑完成的。 - 而

CPU地址线的高位则在扩充存储芯片时使用,用来选择存储芯片(片选),这部分译码由外接译码器逻辑完成。

数据线的连接

- CPU 的数据线数与存储芯片的数据线数不一定相等,在相等时可直接相连;

- 在不等时必须对存储芯片扩位,使其数据位数与 CPU 的数据线数相等。

读写命令线的连接

- CPU 读/写命令线一般可直接与存储芯片的读/写控制端相连, 通常高电平为读, 低电平为写。

- 有些

C

P

U

\mathrm{CPU}

CPU 的读/写命令线是分开的(读为 $\overline{RD} $(read), 写为

W

E

̄

\overline{WE}

WE(write) , 均为低电平有效)

- 此时 C P U \mathrm{CPU} CPU 的读命令线应与存储芯片的允许读控制端相连,

- 而 CPU 的写命令线则应与存储芯片的允许写控制端相连。

- Pin Name Abbreviations - Using Altium Documentation

https://techdocs.altium.com ? files ? wiki_attachments

片选线的连接

- 片选线的连接是 CPU 与存储芯片连接的关键。

- 存储器由许多存储芯片叠加而成,哪一片被选中完全取决于该存储芯片的片选控制端 Cs 是否能接收到来自 CPU 的片选有效信号。

- 片选有效信号与 CPU 的

访存控制信号M R E Q  ̄ \overline{MREQ} MREQ?(MemoryRequst)(低电平有效)有关, - 因为只有当 CPU 要求访存时,才要求选中存储芯片。

- 若 CPU 访问 IO,则 M R E Q  ̄ \overline{MREQ} MREQ? 为高,表示不要求存储器工作。

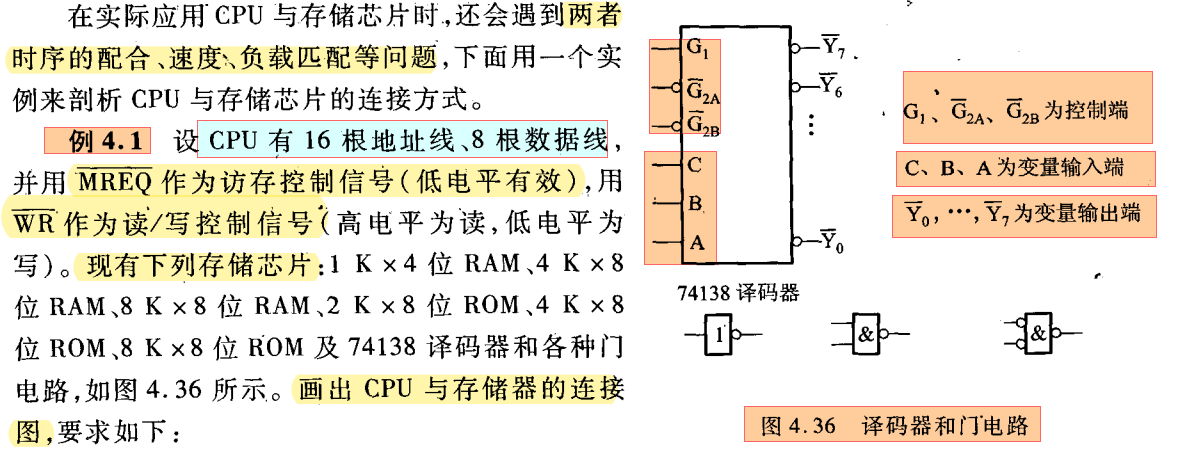

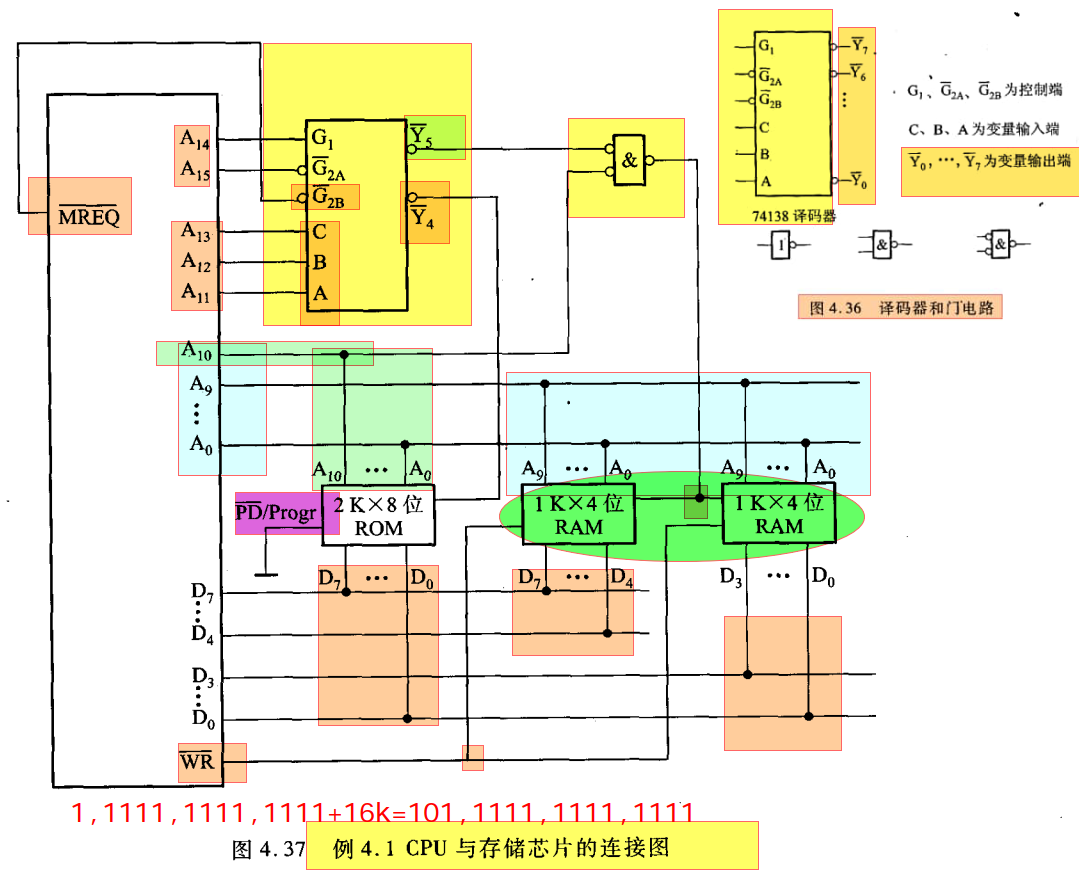

示例

注意到存储是按照字节编址,容量是(范围*8bit)

也不是必须要将十六进制转换为二进制(可以直接执行十六进制的减法运算: 67 F F H ? 6000 H + 1 = 800 H = 2 11 = 2 × 2 10 67FFH-6000H+1=800H=2^{11}=2\times2^{10} 67FFH?6000H+1=800H=211=2×210=2k

类似的, 6 B F F H ? 6800 H + 1 = 400 H = 2 10 H = 1 k 6BFFH-6800H+1=400H=2^{10}H=1k 6BFFH?6800H+1=400H=210H=1k

此处+1是因为此处范围为闭区间,包括起始地址

但是在画片选逻辑图的时候,需要结合cpu地址线的高位部分以及要求的寻址范围,得出哪些cpu地址线需要保持高电平/低电平,从而便于接入特定的地址译码器(驱动其)进行片选

另外我们可以从二进制形式中方便的看出 A 11 , A 12 , A 13 A_{11},A_{12},A_{13} A11?,A12?,A13?的规律,即他们除了 A 11 A_{11} A11?外,其余都保持不变(分别是 A 12 = 0 , A 13 = 1 A_{12}=0,A_{13}=1 A12?=0,A13?=1);如此一来,就可以确定 A 13 , A 12 , A 11 A_{13},A_{12},A_{11} A13?,A12?,A11?(高位到地位分别是100,101这两种可能(十进制就是4,5;所以最终在连接译码器输出端的时候,我们接入的是 Y 4 , Y 5 Y_{4},Y_{5} Y4?,Y5?而不是其他的译码器输出))

- 第一片存储芯片用作系统空间,寻址空间需要11条地址线才能够充分利用该芯片的存储单元

- 第二部分是有两片小的4位芯片组合成一个整体上有8位字长的芯片组,然而位扩展不会增加寻址范围,因此和扩展前的地址线要求一致,仅需要10条地址线

- M R E Q  ̄ \overline{MREQ} MREQ?端:注意,cpu上的访存控制信号 M R E Q  ̄ \overline{MREQ} MREQ?和 A 14 A_{14} A14?的始终保持低电平不同,在需要访存的时候, M R E Q  ̄ \overline{MREQ} MREQ?信号(低电平有效/触发,所以型号名上有overline)才会呈现低电平,从而达到只在需要访存的时候驱动地址译码器进行存储芯片片选

-

A

12

,

A

13

,

A

14

A_{12},A_{13},A_{14}

A12?,A13?,A14?这几条地址本质上和其他地址线没有什么不同(是指,如果该cpu接入的存储系统(芯片不通过小芯片扩展而成,而是同一块芯片的时候,这些地址线仍然以同样的方式工作))

- 当然,这里被用来接入片选译码器,但是译码器应该对于这几条线是透明的.

- 关键在于图中的与非门(用于控制片选RAM部分(芯片组))

- 由于ROM和RAM属于的是字扩展(而非位扩展),所以他们不能同时被选中

- 而 A 10 A_{10} A10?比较独特,因为ROM芯片片内地址需要11条线(也就是需要 A 10 A_{10} A10?,但是RAM片内并用不上 A 10 A_{10} A10?)(本例中,存储扩展后,可寻址地址范围不连续)

- guess:

- 我们要让 A 10 A_{10} A10?有效(高电平)的时候只访问ROM,而不访问RAM

- 又,译码器 Y 5  ̄ \overline{Y_{5}} Y5??为低电平的时候有效,故当 A 10 , Y 5  ̄ A_{10},\overline{Y_{5}} A10?,Y5??均为低电平的时候才选中RAM(书上的说明是用了与门),RAM也是电平有效(选中)

- 后两个芯片构成一组(字长的扩展(也就是为扩展),来匹配机器 cpu 字长)(执行为扩展的时候,注意数据线(D线)的划分:高位部分和低位部分分别连接到不同的被位扩展的芯片上,同时所有成员芯片被同时片选中(是通过该位扩展芯片组的被选中而同时选所有成员 ))

- 一般各个存储芯片都有自己的使能端(片选 C S  ̄ \overline{CS} CS(ChipSelect))(和存储芯片的地址线以及数据线都是不同的)