例子1

题目:

设CPU有16根地址线、8根数据线,并用MREQ作为访存控制信号(低电平有效),用WR作为读/写控制信号(高电平为读,低电平为写)。

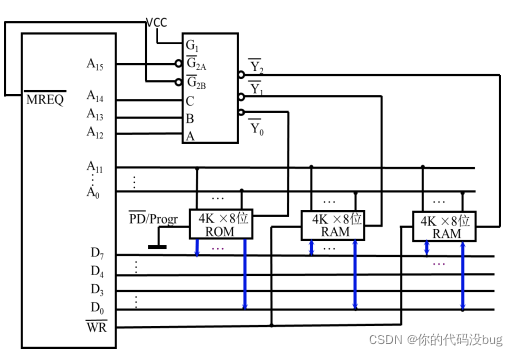

现有下列存储芯片:1 Kx4位RAM、4 K x8位RAM、8 Kx8位RAM;2 K x8位ROM.4 Kx8位ROM、8 Kx8位ROM;74138译码器和各种门电路。如下图所示:

画出CPU与存储器的连接图,要求如下:

①主存地址空间分配:

6000H ~ 67FFH为系统程序区。

6800H ~ 6BFFH为用户程序区。

②合理选用上述存储芯片,说明各选几片

③详细画出存储芯片的片选逻辑图。

1.写出对应的二进制地址码

H代表是16进制

那么6000就应该写成 0110 0000 0000 0000(六进制每一位对应二进制四位)

67FF对应0110 0111 1111 1111

2.确定芯片的数量及类型

系统程序区使用ROM,用户程序区使用RAM

系统程序区A0~A10变化,同时CPU为8根数据线,所以2K×8位。题目提供了这样的ROM。

用户程序区同A0~A9变化,为1K×8位。题目没有提供这样的芯片,但是可以用2片1K×4位芯片,通过位扩展变成1K×8位芯片。

3.分配地址线

74138译码器用来片选(选择芯片)

A13、A12、A11分别连接74138译码器的C、B、A,如果为1 0 0,Y4有效,选中ROM;如果为1 0 1,Y5有效,选中RAM。

G1高电平有效,连接A14

A15可以连接在74138译码器的G2A上(低电平有效)

74138译码器的G2B也是低电平有效,那么用什么连接?题目中CPU的MREQ低电平时,才访问存储器,那么正好可以连接G2B。

4.连接

观察写出的二进制地址码,CBA(101)使Y5有效的同时,A10还得为低电平才能选中RAM,如果A10不是低电平,那么就会超出范围。

所以Y5和A10通过 与门 输出,作为片选线连接两个RAM。

两个RAM因为要位扩展,所以CPU数据线各连接4条。

ROM只读,所以编程线接地。

?

例子2

题目:

假设同前,要求最小4K为系统程序区,相邻8K为用户程序区。

1.写出对应的二进制地址码

最小4K,说明从0开始

相邻8K,那么ROM地址之后加1,其中A0~A11变化,212为4K

那么还需要4K,从上个4K后继续加1,其中A0~A11变化,又为4K

2.确定芯片的数量及类型

系统程序区使用ROM,用户程序区使用RAM

系统程序区A0~A11变化,同时CPU为8根数据线,所以4K×8位。题目提供了这样的ROM。

用户程序区同A0~A11变化,为4K×8位。题目也提供了这样的芯片,所以不需要位或字扩展。

3.分配地址线

G1高电平有效,可以直接连接电源,或者A15取反

A15为0,可以接在G2A或G2B上

MREQ低电平访问存储器,也可以和G2A或G2B相连

4.连接