��4�´�������ϵ�ṹ

ѧϰ���������:֪������Ȼ����Ȥ,�����������������ϵͳ��ι���,Ƕ��ʽ����

4.1 Y86-64ָ���ϵ�ṹ

һ��������֧�ֵ�ָ���ָ����ֽڼ������Ϊ����ָ���ϵ�ṹ,�� ISA,�ڴ�������Ϊ(��ָ��ϼ���������)�����ʵ�ִ�����֮���ṩ��һ�����ISA�ṩ�˳���ִ�е�һ��˳��˵��,Ҳ����һ��ָ��ִ������,��һ��ָ��ŻῪʼ��

����һ��ָ���ϵ�ṹ**(���� Y86-64)**�����������״̬��Ԫ��ָ������ǵı�D�롢һ���̹淶���쳣�¼�������

Y86-64�����е�ÿ��ָ����ȡ���Ĵ�����״̬��ijЩ����,��Ϊ����Ա�ɼ�״̬

�õ���ISA����RISCָ�������,Ҳ��CISCָ������ԡ�Ȼ��,����ָͬ����֯�ŵ�������д���,�ڴ�,���ݱ�ִ�е�ָ��IJ�ͬ,ÿ�����еIJ���Ҳ����ͬ���ݴ�,���ǹ�����SEQ������,����ÿ��ʱ������ִ��һ��ָ��,����ͨ����������Ρ�

4.2����ƺ�Ӳ����������HCL

��Ӳ�������,�õ��ӵ�·�������λ��������ĺ���,�Լ��ڸ��ִ洢����Ԫ�д洢λ��������ִ���·�����������ź����ϵĸߵ�ѹ��͵�ѹ����ʾ��ͬ��λֵ��

�ڵ�ǰ�ļ�����,��1����1.0�������ҵĸߵ�ѹ��ʾ��,����0����0.0�������ҵĵ͵�ѹ��ʾ�ġ�

Ҫʵ��һ������ϵͳ��Ҫ������Ҫ����ɲ���:�����λ���в����ĺ�������������洢λ�Ĵ洢����Ԫ,�Լ����ƴ洢����Ԫ���µ�ʱ���ź���

���������ֵ�·�Ļ������㵥Ԫ�����Dz��������,������������λֵ��ij������������

���ܶ��������ϳ�һ����,���ܹ��������(computational block),��Ϊ��ϵ�·( combinational circuits)����ι�����Щ���м�������:

- ÿ�����ŵ����˱������ӵ�����ѡ��֮һ:1)һ��ϵͳ����(��Ϊ������),2)ij���洢����Ԫ�����,3)ij�����ŵ������

- �����������ŵ��������������һ�𡣷������ǿ��ܻ�ʹ���ϵ��ź�ì��,���ܻᵼ��һ�����Ϸ��ĵ�ѹ���·���ϡ�

- ��������������ġ�Ҳ���������в�����·������һϵ�е��Ŷ��γ�һ����·,�����Ļ�·�ᵼ�¸��������ĺ��������塣

��ϵ�·�ӱ����Ͻ�,���洢�κ���Ϣ���෴,����ֻ�Ǽ���Ӧ�����ź�,�������������ij�������������Ϊ�˲���ʱ���·(sequential circuit),Ҳ������״̬���������״̬�Ͻ��м����ϵͳ,���DZ������˰�λ�洢��Ϣ���豸���洢�豸������ͬһ��ʱ�ӿ��Ƶ�,ʱ����һ���������ź�,����ʲôʱ��Ҫ����ֵ���ص��豸�С���������洢���豸:

- ʱ�ӼĴ���(��ƼĴ���)�洢����λ���֡�ʱ���źſ��ƼĴ�����������ֵ��������ʴ洢��(����ڴ�)�洢�����,�õ�ַ��ѡ��ö����д�ĸ��֡�

- ������ʴ洢�������Ӱ���:1)�������������ڴ�ϵͳ,Ӳ���Ͳ���ϵͳ�����������ʹ������������һ���ܴ�ĵ�ַ�ռ��ڷ����������;2)�Ĵ����ļ�,�ڴ�,�Ĵ�����ʶ����Ϊ��ַ��

4.3 Y86-64��˳��ʵ�֡�

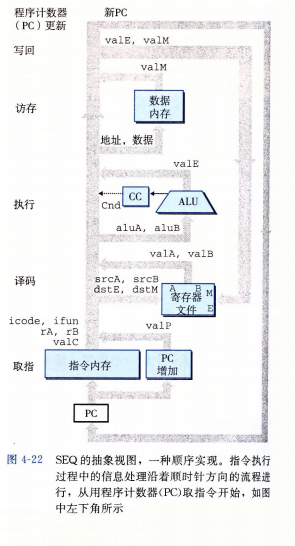

��������֯�ɽ�:ȡָ,����,ִ��,�ô�,д��,����PC

ͨ����ִ��ÿ����ָͬ������IJ�����֯��һ��ͳһ������,�Ϳ����ú������ĸ���Ӳ����Ԫ�Լ�һ��ʱ�ӿ��Ƽ����˳��,�Ӷ�ʵ����������������������һ��,�������ͱ���Ҫ����Щ��Ԫ֮��·���ź�,������ָ�����ͺͷ�֧���������ʵ��Ŀ����źš�

SEQΨһ�����������̫���ˡ�ʱ�ӱ���dz���,��ʹ�ź�����һ�������ڴ������еĽΡ�

����ʵ�ַ������ܳ������Ӳ����Ԫ,��Ϊÿ����Ԫֻ������ʱ�����ڵ�һ����ʱ���ڲű�ʹ�á����ǻῴ��������ˮ���ܻ�ø��õ�����

4.4��ˮ�ߵ�ͨ��ԭ��

��ˮ��ͨ���ò�ͬ�Ľβ��в���,�Ľ���ϵͳ�����������ܡ�������һ��������ʱ��,����ָ���ͬ�Ľδ��������������ֲ����ԵĹ�����,���DZ���dz�С��,���ṩ������˳��ִ����ͬ�ij�����Ϊ��ͨ�����µ���SEQ�������ֵ�˳��,������ˮ��,���ǵõ�SEQ+,����������ˮ�Ĵ���,������ PIPEһ��ˮ�ߡ�Ȼ��,������ת����,�����˽������һ��ָ��͵���һ��ָ��,�Ӷ��������ˮ�ߵ����ܡ��м������������Ҫ�������ˮ�߿���������ͣ��ȡ��һЩ��ˮ�߽Ρ�

4.5 Y86-64����ˮ��ʵ��

�� PIPE�����,��ȡ��һЩ��ʩ����ȷ����������ء���ˮ����Ƶ�Ŀ�ľ���ÿ��ʱ�����ڶ�����һ����ָ��,Ҳ����˵ÿ��ʱ�����ڶ���һ����ָ�����ִ�нβ�������ɡ�

�²��֧�����ݲ²ʼȡָ�ļ�����Ϊ��֧Ԥ����

һ���,ͨ������ˮ�߽ṹ�м����쳣������,���Ǽ��ܹ��Ӹ����쳣��������ȷ��ѡ��,Ҳ�ܹ�����������ڷ�֧Ԥ�����ȡ����ָ����ɵ��쳣�������Ϊʲô���ǻ���ÿ����ˮ�Ĵ����а���һ��״̬��stat��

Ϊ�˱����쳣ָ��֮���ָ������κγ���Ա�ɼ���״̬,�����ڷô��д�ؽ��е�ָ����쳣ʱ,��ˮ�߿����������ֹ����������Ĵ������������ڴ档