3.1 �洢������

�洢Ԫ�洢���м�¼һλ��������Ϣ�Ĵ洢��λ�洢��Ԫ�����ɸ��洢Ԫ��ɡ�������Ϣ�����Ļ�����λ�洢�����뵼�������ʹ��Բ�����ȡ��ʽ˳���ȡ�������ȡ�洢���ķֲ�ṹ�Ĵ����� Cache �����桢�����洢���洢���ֲ�ṹ

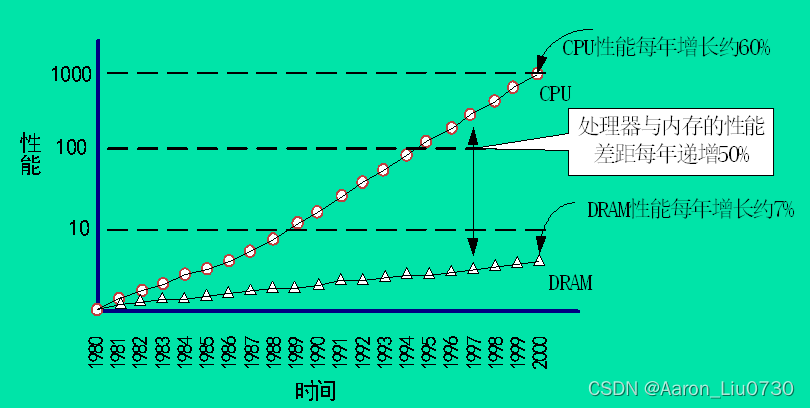

?����˶Դ洢��Ҫ��������,�ٶȿ�,�ɱ�������֮���ì��?

�洢�����ʵľֲ���(Locality)ԭ��

(1)ʱ��ֲ���(Temporal Locality):��ǰ����ʹ�õ���Ϣ�ܿ����Ǻ���������Ҫ�õ���Ϣ,�����ѭ���Ͷ�ջ����.

(2)�ռ�ֲ���(Spatial Locality):ָ����ʹ�õ�����Ϣ�ܿ����ڴ洢�ռ������ڻ����.��˳��ִ�еij��������(������),�������.

(3)�ֲ�ṹ:�ֲ���ԭ���Ǵ洢ϵͳ��νṹ���������ԵĻ���.???һ��:??????

?����:

��:�����洢��ϵͳ(cache��MM), ��һ������Ϊ1KB,����ʱ��1 m S

�ڶ�������Ϊ1MB,����ʱ��10 m S,CPU�ȷ��ʵ�һ��,�粻��,���ɵڶ���������һ��.

��:��Ϣ�ɴӵ�һ��100%(��90%)ȡ��,�ֱ���ƽ������ʱ��:

��:100%ʱ:TA=1*100%+10*0%=1 m S

?????? 90%ʱ:TA=1*90%+10*10%=1.9 m S

����:��ߵ�һ���ķ���ʱ��ı��ʿ�ʹƽ������ʱ��ӽ�(�����)��һ�����ٶ�.

���洢���������ĵ�λ,�Ǽ�������������ij��� !

3.2? ���洢�������뼼��ָ�� ?

3.2.1? ���洢������

����洢�� (RAM , random access memory)ֻ���洢�� (ROM, read-only memory)�ɱ�̵�ֻ���洢�� (PROM, programmable ROM)�ɲ����ɱ��ֻ���洢�� (EPROM, erasable PROM)���õ�����Ŀɱ��ֻ���洢�� (E 2 PROM, electrically EPROM)ע:RAMΪ��ʧ�Դ洢��,ROMΪ����ʧ�Դ洢��

3.2.2 ���洢������Ҫ����ָ��

RAM�����ͼƬ�ͼ۸���Բο��������ƽ̨

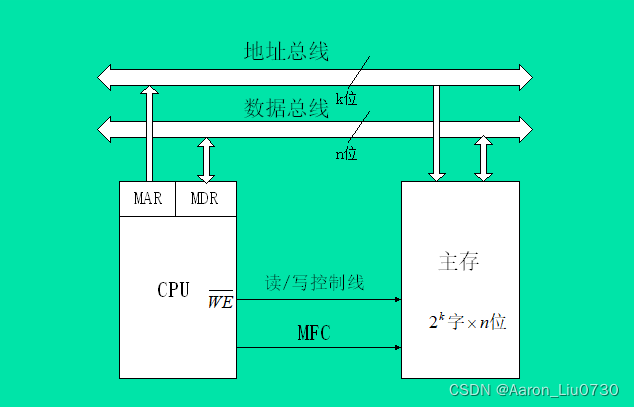

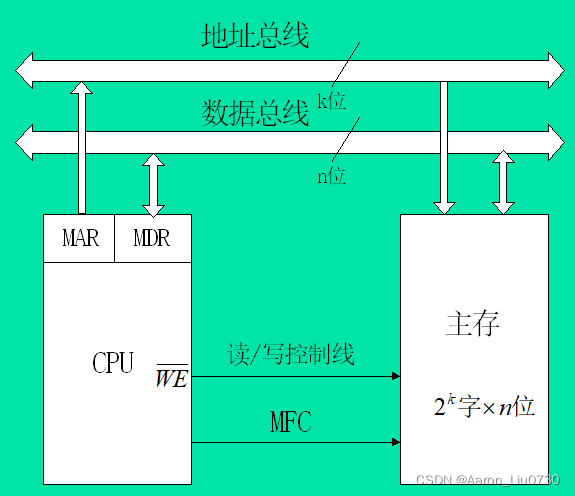

���洢����CPU������

3.3?? �����д�洢��(RAM)?

RAM(Random Access Memory) :������ضԴ洢������һ��Ԫ��ȡ,��ȡʱ����õ�Ԫ������λ���ء��뵼�����Ԫ����Ҫ��:1. �� 2 ���ȶ�״̬, ��ʾ��ֵ �� 0 �� �� �� 1 �� ;2. ���ⲿ�źż�����, 2 ���ȶ�״̬�ܽ����������ת��;3. ���ⲿ�źż�����,�ܶ��� 2 ���ȶ�״̬;4. �洢�ɿ�����ԭ���Ϸ�,�뵼�����Ԫ���ɷ�Ϊ˫�� (bipolar) �ͺ� MOS(Metal Oxide Semiconductor) �͡������ֿɰ�����ԭ����Ϊ��̬�Ͷ�̬���֡�SRAM(Static RAM)��̬ RAM ,���ÿ������Լ���ֻҪ��Դ�е�,�����ȶ�������ϢDRAM(Dynamic RAM)����̬ RAM�����Դ��,��Ҫ���ڶ������ ( ˢ�� ) ��?

3.3.1? ��̬������SRAM???????

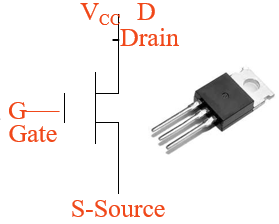

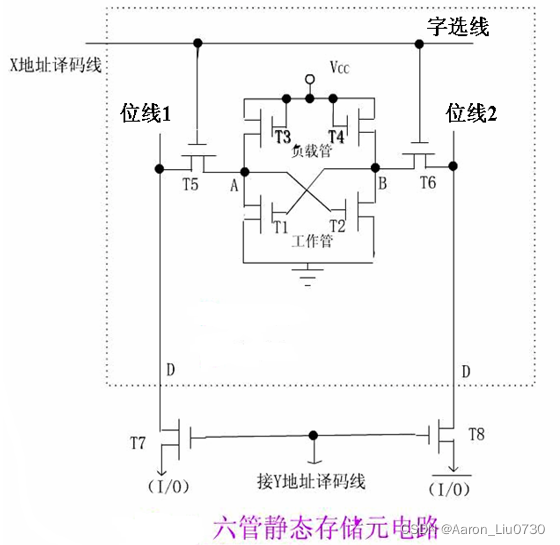

����SRAM�洢Ԫ��������MOS������������϶��ɵĴ���������������4��MOS����ɵĴ������洢һλ��������Ϣ?

MOS �ܾ�̬���䵥Ԫ�ص�:�ŵ�:���ƻ��Զ���,������ǿ,�ɿ���

ȱ��:���䵥Ԫ���Ӷ�,ռ��Ƭ�����,���Ľϴ�,���ɶȲ��ߡ�

˫���� (bipolar) :�� TTL �� ECL(Emitter-Couple Logic) ,�ٶȿ�,���ڸ��ٻ��档3.3.2? SRAM�洢�������?

ʵ��Ӧ�õ� SRAM �洢���������ڴ洢��Ϣ�Ĵ洢����,����һЩ������·,���ַ�����·��������·����д��·�Ϳ��Ƶ�·����ɡ�

1.�洢��

? �洢�����ڶ�洢Ԫ����,�Ǵ洢��Ϣ�ij������洢���еĸ��洢Ԫͨ�����һ���Ľṹ,һ������֯�ɶ�ά�������ʽ��

2.��ַ�����·

? ��ַ�����·���ڽ��ӵ�ַ�������ĵ�ַ�źŷ���ɶ�Ӧ�洢��Ԫ��ѡ���źš������������Ϣ����CPU�ĵ�ַ�Ĵ�������ַ�Ĵ������ڴ��Ҫ���ʵĴ洢��Ԫ�ĵ�ַ��

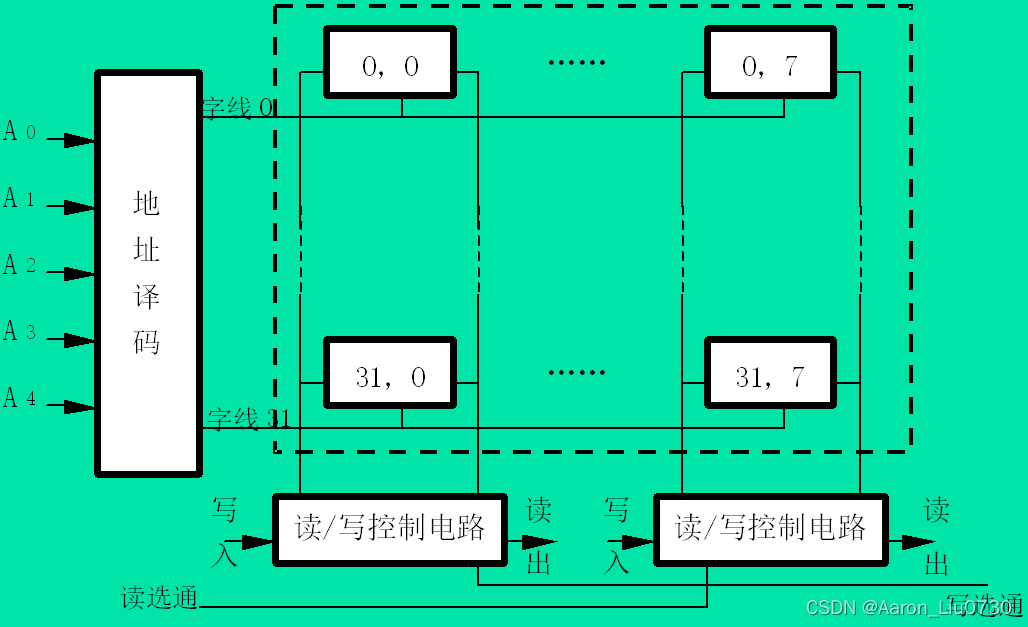

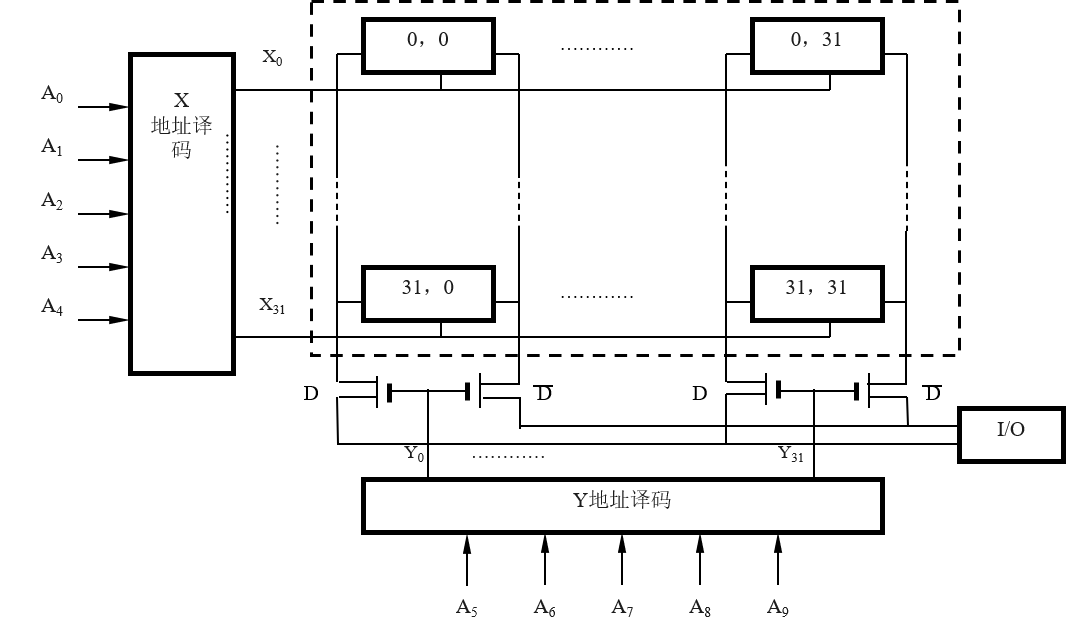

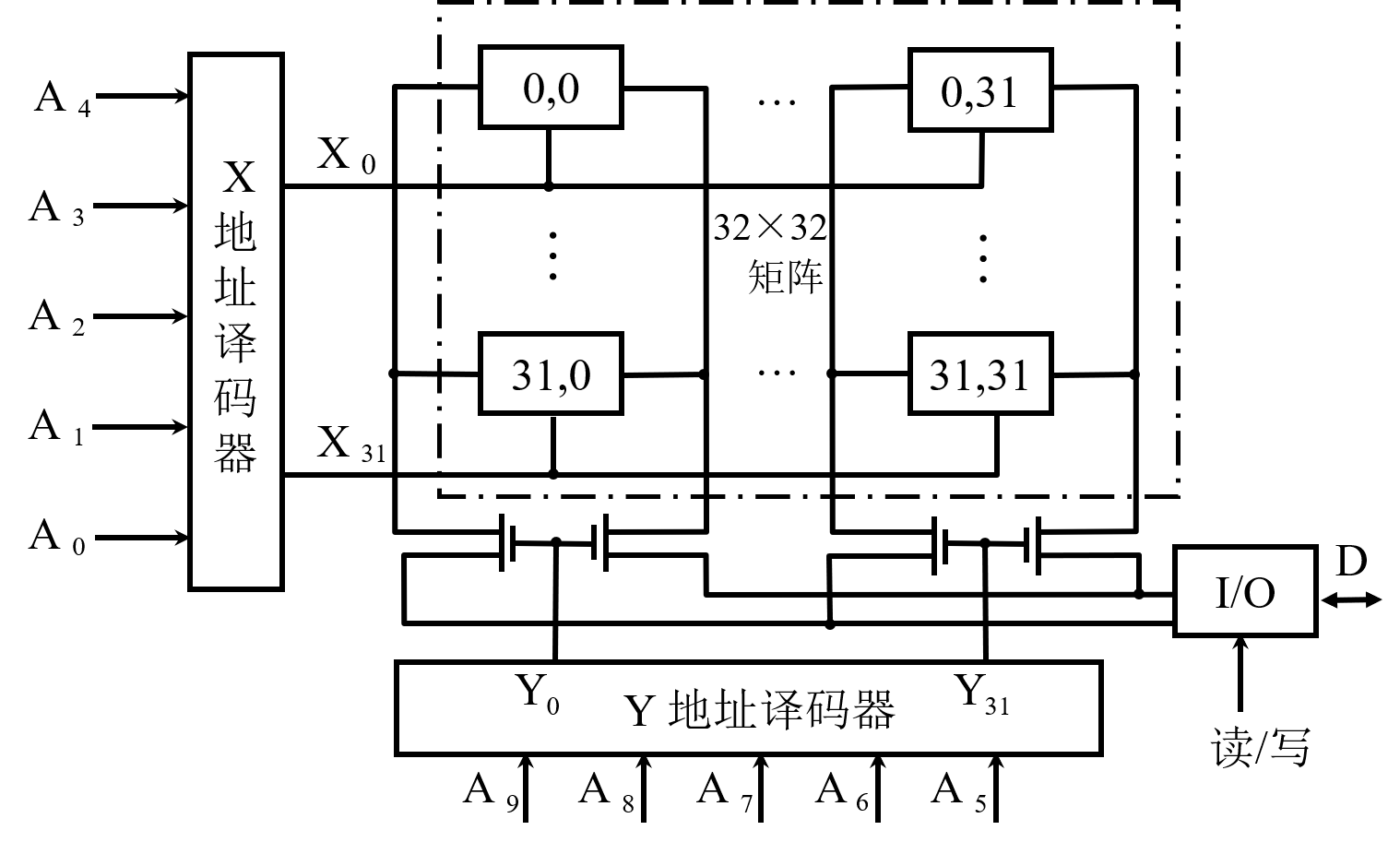

��ַ���������ַ�ʽ,һ���ǵ����뷽ʽ,��������������Ĵ洢��;��һ����˫���뷽ʽ,�����������ϴ�Ĵ洢���������뷽ʽ

?˫���뷽ʽ

?

3.������

? ��˫����ṹ��,ÿ��X�����ѡ����Ҫ����һ�������ϵ����д洢Ԫ��·,���ݸ��غܴ����,Ϊ���ܹ���������X����ѡ�����ϵ����д洢Ԫ��·,���������������һ��������,

4.I/O��·

? I/O��·�����������ߺͱ�ѡ�õĵ�Ԫ֮��,���ڿ��Ʊ�ѡ�еĴ洢��Ԫ������д��,�õ�·������Ϣ�Ŵ����á�

5.Ƭѡ���/д���Ƶ�·

? ĿǰÿһƬ�Ĵ洢�����վ���������,����,һ���洢������Ҫ��һ�������Ĵ洢оƬ��ɡ��ڽ��е�ַѡ��ʱ,����ҪѡƬ,����ҪƬѡ��·��

? �����Դ洢оƬ�Ƕ�����д,��һ�����ɶ�/д���Ƶ�·����ɡ�

6.�������

? Ϊ����չ�洢��������,���轫��ƬRAM�������߲���ʹ��;����˫�������������ӡ������Ҫ�õ���̬�����������

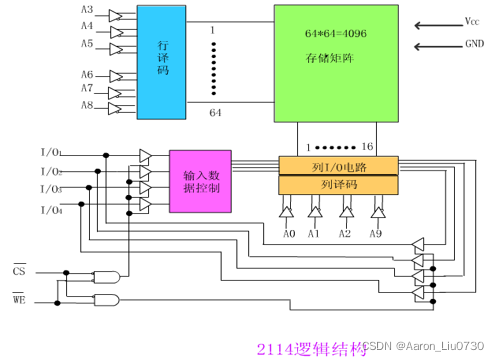

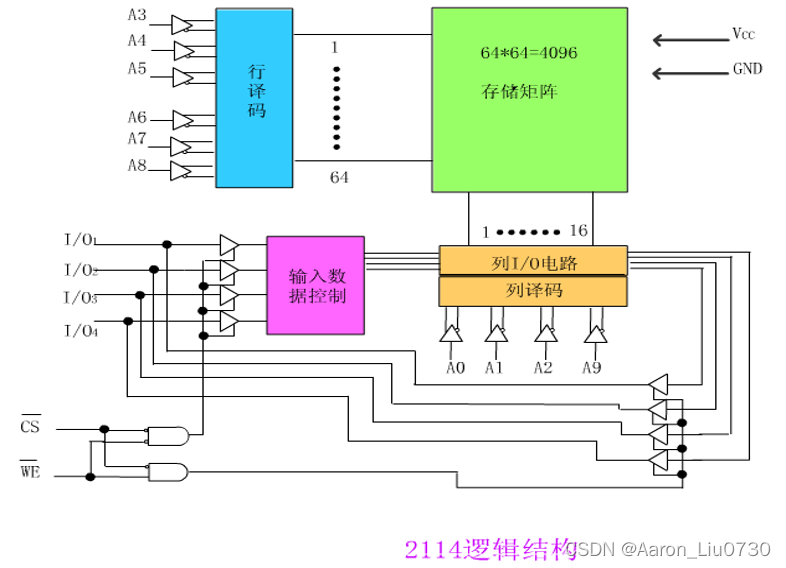

SRAMʵ��-Intel 2114 ?

SRAMʵ��-Intel 2114 ?

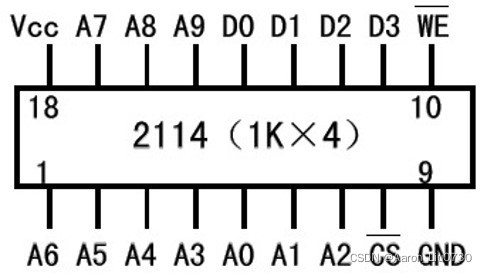

RAM2114����10����ַ��,4�������ߡ���������Ϊ:1024�֡�4λ(�ֳ�Ϊ1K ��4)

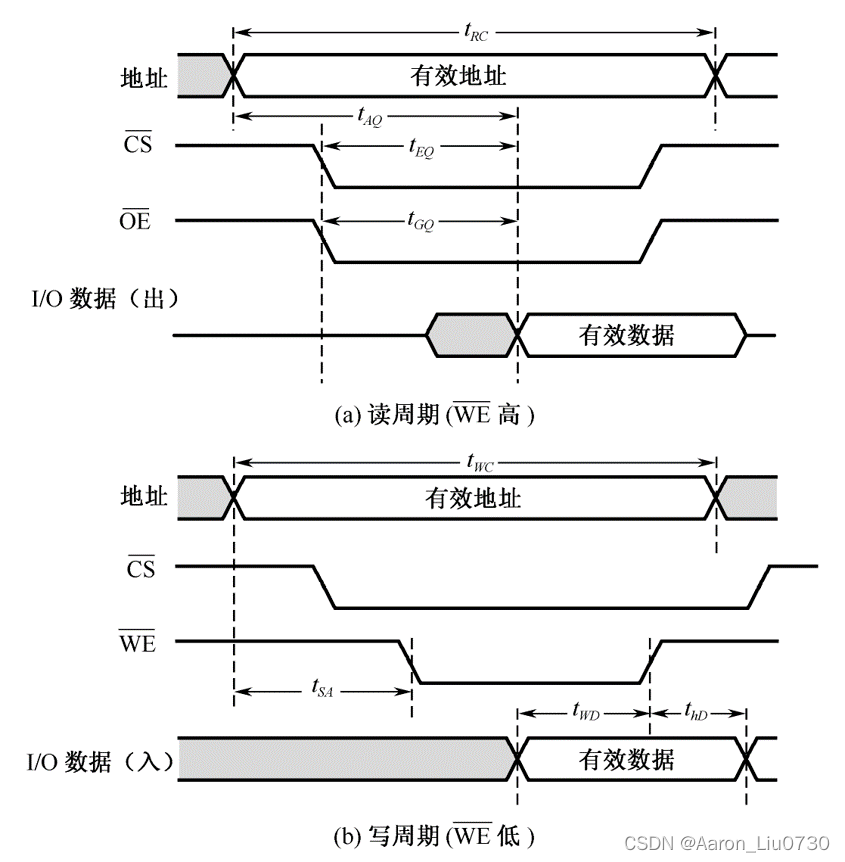

SRAM�Ķ�д����?

3.3.3? ��̬�洢��

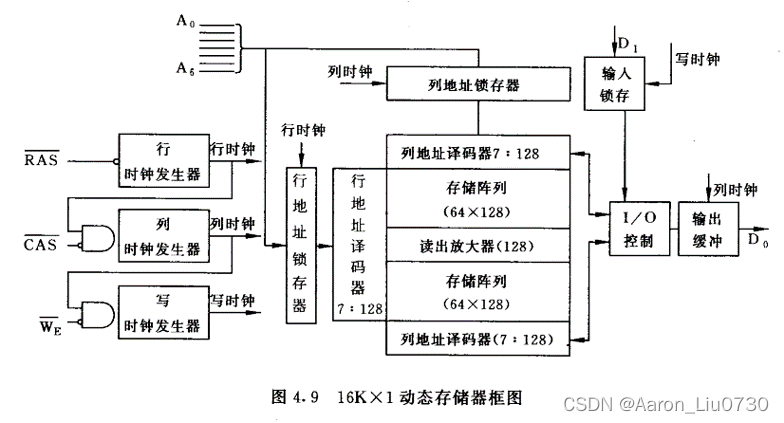

���ܴ洢��Ԫ��·ͼ���� 1K λ DRAM���ܴ洢��Ԫ��·ͼ������ɶ�

DRAM�ĵ�������?

�����ɶȸ�,���ĵ�

�ھ�����ʧ��,����ˢ��

���ƻ��Զ���,���������д

�ܶ�����д,ˢ�¾�����ˢ�·Ŵ������С�

DRAM�洢��-Intel 2116 ?

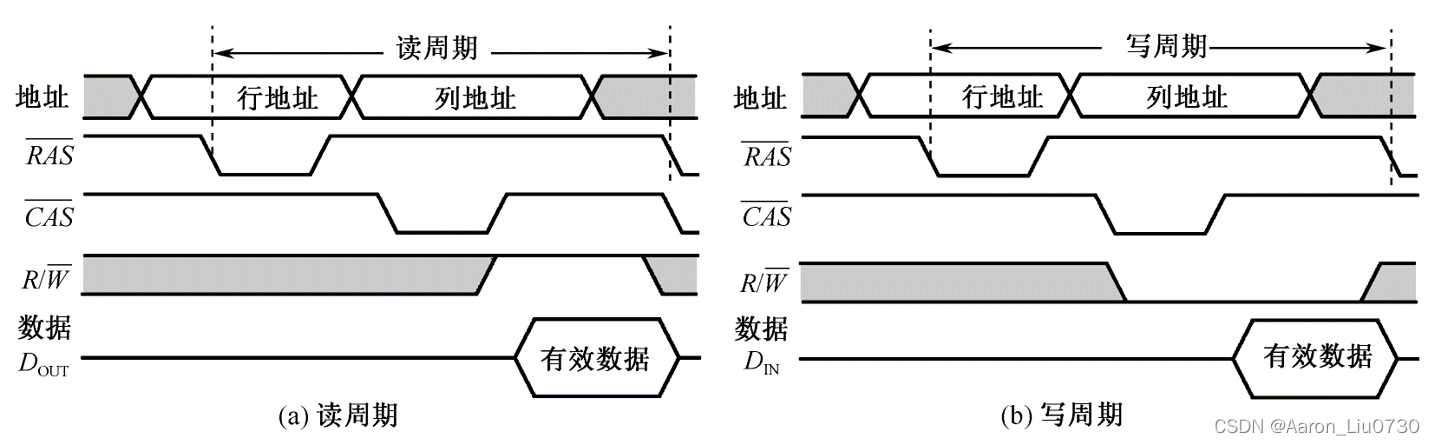

3.3.4 DRAM��ˢ�»��� ?

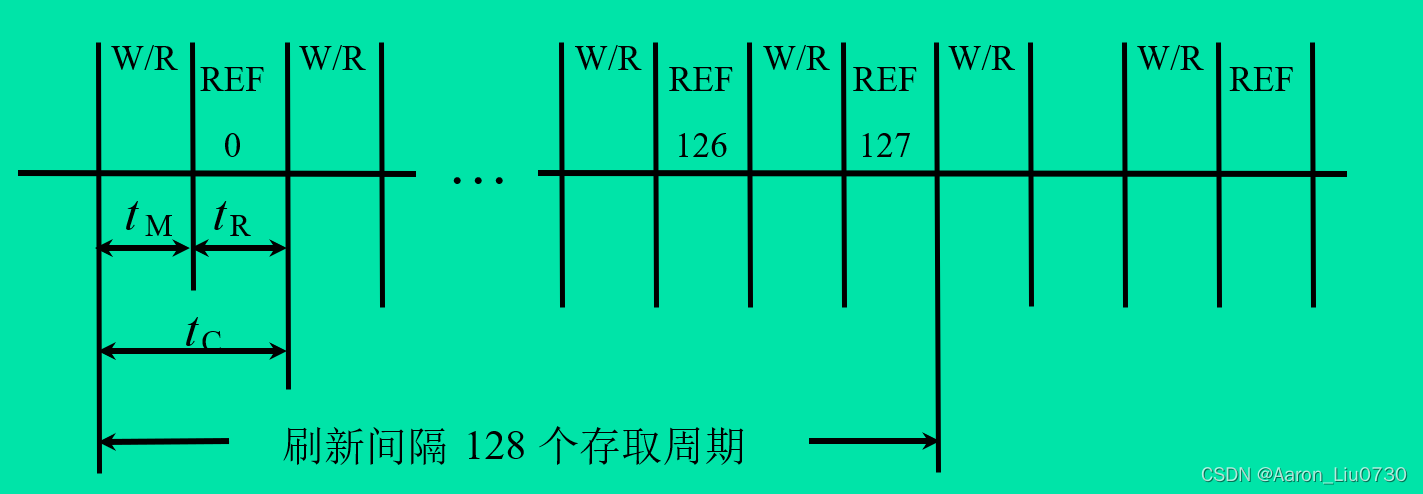

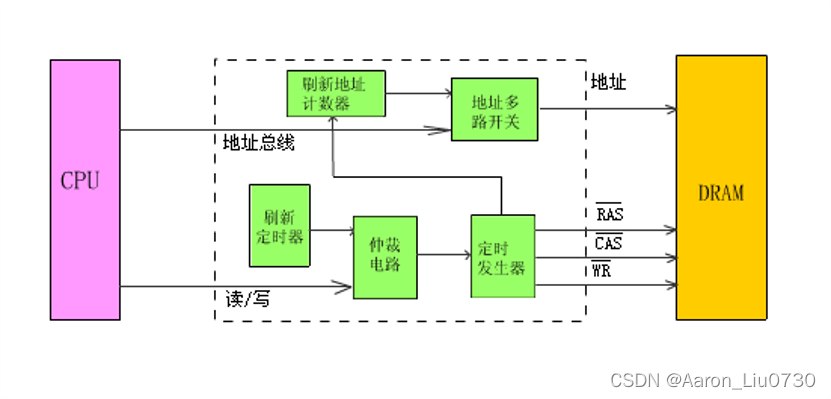

��̬ MOS �洢������ �� ���� �� ��ʽ����ˢ�¡���Ϊ�ڶ��������лָ��˴洢��Ԫ MOS դ�����ݵ��,������ԭ��Ԫ������ ,���Զ������̾���ˢ�¹��̡�ͨ��,��ˢ�¹�����ֻ�ı���ѡ���ߵ�ַ,ÿ��ˢ��һ�С����ζԴ洢����ÿһ�н��ж���,�Ϳ�����ɶ����� DRAM ��ˢ�¡� ����һ�ζ������洢��ˢ�½�������һ�ζ������洢��ȫ��ˢ��һ��Ϊֹ,��һ��ʱ������ˢ������, һ��Ϊ 2ms , 4ms , 8ms �����õ�ˢ�·�ʽ������: ����ʽ����ɢʽ���첽ʽ ��?����ʽˢ��

�����������ˢ��ʱ����( 2ms )��,���մ洢��������С���а���ˢ��ʱ��,ˢ���ڼ�Ҫֹͣ�� / д������ (128 ��,ϵͳ��������Ϊ 500ns, ��ÿ��ˢ�������ڹ��� 4000 ���������� )

���ü���ʽˢ�µ�ϵͳ��ȡ���ڲ���ˢ�¹�����Ӱ�졣��д������ˢ�¹��������ˢ�������зֿ�����,���,ϵͳ�Ĵ�ȡ�ٶȱȽϸ�,��ֻȡ���ڵ�Ԫ��·����Χ��·����ʱ�����ڼ���ˢ���ڼ��ڲ��ܽ����κζ�/д����,���ʱ���Ϊ��ʱ��,�����ʱ�����������ܽ����κβ���������洢оƬ�ĵ�Ԫ��Ŀ����,����ʱ�����,��ζ�������ڸ�����ʱ���ڲ��ܽ����κβ�����

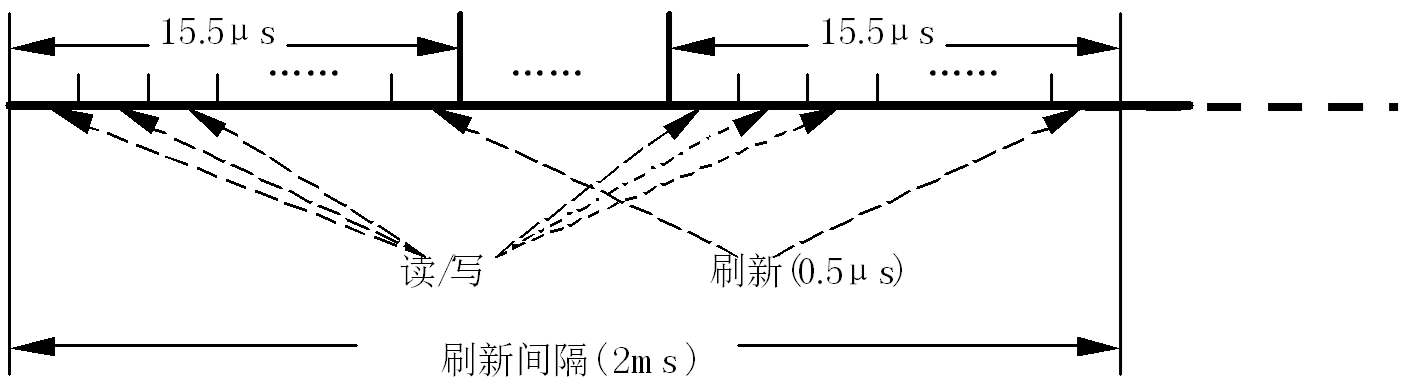

��ɢˢ��(��ȡ����Ϊ1 ms )

�� 128 ��128 ������

?(��ȡ����Ϊ 0.5 ms + 0.5 ms )

�첽ˢ��(�ֲ�ʽˢ��)

�첽ˢ�³�����������ˢ�¼��ʱ��,���� 2ms ���ʱ���ڽ�ˢ�²���ƽ�����䵽���������ʱ���ڽ��С��������е�ˢ�¼���������ˢ�¼��ʱ�� (2ms) ����������

�洢�����Ƶ�·

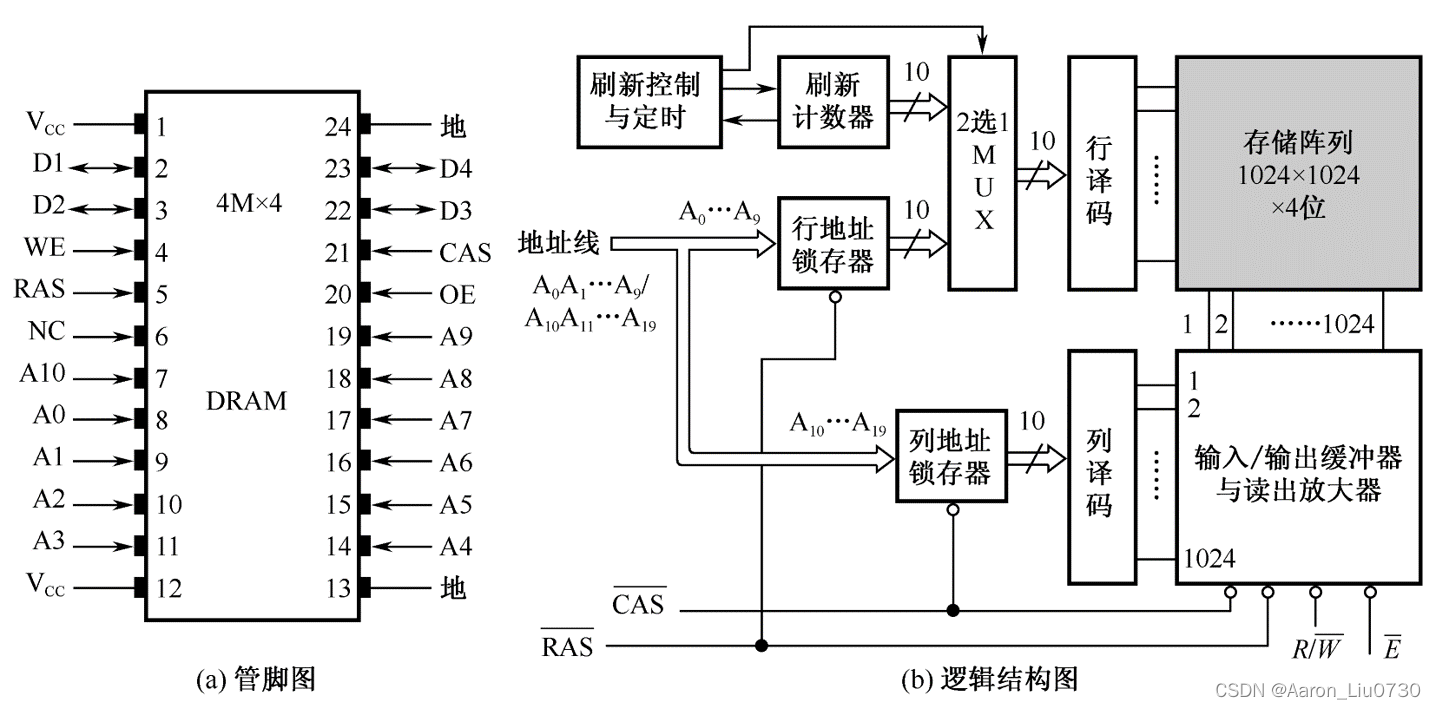

?1MX4λDRAM

3.3.5 SRAM��DRAM�Ƚ�?

3.4 ֻ���洢�������ٴ洢��?

ֻ���洢����һ��Ϊ����ʧ��(Non-Volatile)�Ĵ洢����ROM�������������ŵ�,һ�ǽṹ��,λ�ܶȱȿɶ�/д�洢����;���Ǿ��з���ʧ��,���Կɿ��Ըߡ�

��Ĥʽֻ���洢��( Mask-Programmable ROM )��ģʽ ROM ��Ҫ���������Ȱ������ij�������ݶ�оƬͼ��(��Ĥ)���� 2 �ι�̶��γ�,����������һƬ������ ROM ���úܴ�,������ͬ�����ݵ� ROM �ͺܱ��ˡ������ģʽ ROM �����ڳ��������Ķ��Ͳ�Ʒ,�����ڴ�ż����ϵͳ��ʼ����Ϣ�� BIOS ( Basic Input Output System )�ȡ�?

һ�α��ֻ���洢�� (Programmable ROM , PROM)????????PROM�ֳ�Ϊ�ɱ��һ�ε� ROM(One Time PROM ,��� OTPROM) ���ڳ���ʱ,���д洢Ԫ�����ӹ���ͬһ״̬ �� 0 �� ( �� �� 1 �� ) ,�û��ɸ�����Ҫͨ����̽�ijЩ�洢Ԫ��״̬�ı����һ״̬ �� 1 �� ( �� �� 0 �� ) �������ֱ��ֻ�ܽ���һ��,һ��������,�����ݱ㲻���ٸı䡣?

������ɱ��ֻ���洢�� (Erasable Programmable ROM , EPROM)������ɱ��ֻ���洢�����Ϊ EPROM �����ִ洢���ǽ� PROM �ı���˿�ij��� MOS FET ���ɵĵ��ӿ��ء��仹ԭ����Ϊ������ƹ�������һ��ʱ�� (15 ~ 20 �������� ) ,������ EPROM ������ʹ��,�������������ϵ����һ����( 100 ������)��?

������Ϳɱ��ֻ���洢�� (Electrically Erasable Programmable ROM , EEPROM)������͵Ŀɱ��ֻ���洢��Ҳ���Ϊ EAROM(Electrically Alterable ROM) ,��洢Ԫ�� EPROM ����,�����ӿ��ػ�ԭʱ�����������,ֻ������źż�����ɲ��������� EEPROM �� EPROM ��ĿǰӦ����㷺��ֻ���洢����EPROM ��Ȼ���пɷ�����̵��ŵ�����㷺ʹ��,�� EPROM ֻ���������,����һ���洢��Ԫһ���洢��Ԫ�ض�������,���Ҳ��������Ƚ��鷳���� EEPROM �˷��� EPROM ����һ���㡣????????EEPROM�Ľṹ��EPROM����,���Ǿ߸���դ����MOS,�����������F˿����һ��,��������ٻ�ԭ��ȥ����EEPROM�ڸ�դ��������һ������������,���ʱ��ʹ���ͨ��������դ,������ʱ��ʹ���ͨ��������,�������ͱ�̾��õ���ɡ�

���ٴ洢��( Flash Memory )���ٴ洢��( Flash Memory )��� ���� , 1988 ���� Intel ��˾�����Ƴ�,Ҳ��һ�����ʧ�Դ洢�� NVM ( Non-Volatile Memory )��ʹ�ڹ����Դ�رպ����ܱ���Ƭ����Ϣ,��һ������ ROM ��ͬ���� EEPROM ���, ���ٴ洢�� Ҳ���Խ��е�����Ϳ��ظ����,��������Ҫ����ĸߵ�ѹ,���ҳɱ����͡��洢�ܶȸ�������ص�����ʹ�����ڹ㷺�������ڸ�������

3.5 �洢����չ

λ��չ

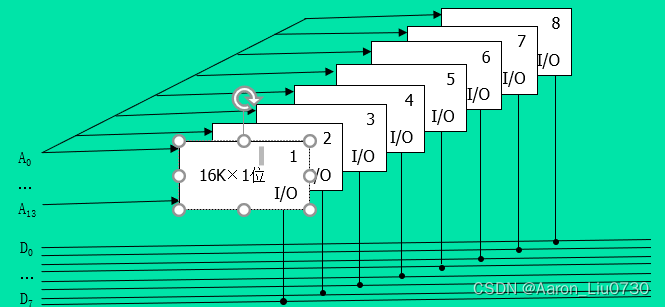

����洢����洢оƬ����һ�¶�λ������,����Ҫ����λ��չ��(��:16K��8λ,16K��1λ),λ��չ��ָֻ��λ��������е���չ,���Ӵ��ֳ���λ��չҪ�����洢оƬ����ַ�ߡ�Ƭѡ�ź�������/д�����ź��߲���,����оƬ�������ߵ����г���

����չ

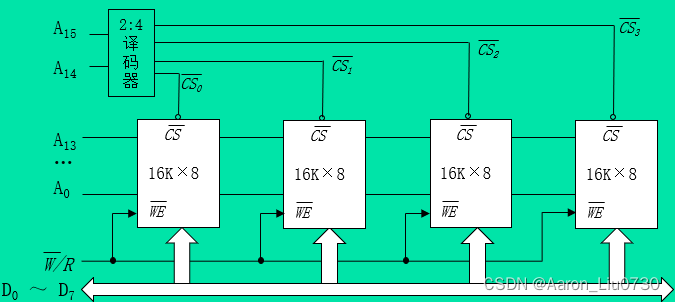

����洢����洢оƬλ��һ��,����������,����Ҫ��������չ,(��:64K��8λ,16K��8λ),��λ��,ֻ���������䡣����չ�ľ��巽���ǽ�оƬ����ַ�ߡ������ߺͶ�/д�����߶�����,�ɵ�ַ��λ�����γ�Ƭѡ�ź��� ?

��λͬʱ��չ

����洢����洢оƬλ����һ��,����Ҳ����ͬ,����Ҫ������λͬʱ��չ,����Ҫ����λ���ϵ�����,��Ҫ���������ϵ����䡣��λͬʱ��չ��ǰ������չ��ʽ�����,ʵ��ʱֻҪ��ѭ���Ե���չ���ɼ��ɡ�????????��λͬʱ��չ�������ڹ�����������Ĵ洢����

?

����:

��Ҫһ��16M��16λ�Ĵ洢��,���д洢оƬΪ4M��8λ��

(1)������Ҫ���ٸ��洢��оƬ��

(16m * 16 )/(4m * 8) = 8 Ƭ

(2)�洢��оƬ�����洢���ĵ�ַ���ȸ���Ҫ����λ?

16 m * 8 --> 2^4? * 2 * 10^20 * 2^3

(3)�����ô洢��оƬ�������洢������ʾ��ͼ��

3.6 ��߷ô��ٶȵĴ�ʩ?

?

3.6.1 ���д洢��

˫�˿ڴ洢��?

���彻��洢�����彻�淽ʽ�Ƕ���洢������һ����֯��ʽ,����ģ��ı�ַ�ǽ�����е�,���볣��洢���в���˳��ʽ��ַ������ͬ��

?

���������ٶ�ģ���ֳ������������߿���,ģ���ȡһ���ֵĴ洢����Ϊ T ,���ߴ�������Ϊ �� ,�洢���Ľ���ģ����Ϊ m ,Ϊ��ʵ����ˮ�߷�ʽ��ȡ,Ӧ������??????????????? T=m��???????? (m=T/����Ϊ�����ȡ��)

? ����洢��Ҫ����ģ����������ڻ���� m ,�Ա�֤����ijģ��� m�� ʱ���ٴ�������ģ��ʱ,�����ϴδ�ȡ�����Ѿ���ɡ�����洢��������ȡ m ���������ʱ��Ϊ:????????????????? t1=T+(m-1)��

? ˳��ʽ�洢��������ȡ m ��������ʱ��Ϊ:????????????????? t2=mT.

���� q Ϊ��ȡ m ���ֵ���Ϣ��,�����Ϊ???????????????????? W1=q/t1?

?????????????????? W2=q/t2?

?3.6.2 DRAM�������뷢չ

1? FPM DRAM

FPM DRAM�ֳ�Ϊ��ҳģʽDRAM(Fast Page mode DRAM),�Ǵ�ͳDRAM�ĸĽ��Ͳ�Ʒ������DRAM��Intel 286��386ʱ�������С���Ҫ�ص��Dz����˲�ͬ������DRAM���е�ַ������ʽ,��ͳDRAM�ڴ�ȡһλ����ʱ,����ֱ������е�ַ���е�ַ��Ϣ��FPM DRAM����һѰַ��ʽ���˸Ľ�,�����е�ַ��,���CPU��Ҫ��������ͬһ�е�ַ��,�������ͬһ����������е�ַ������������е�ַ����ҳʽ������ʱ��ͼ

2? CDRAMоƬ

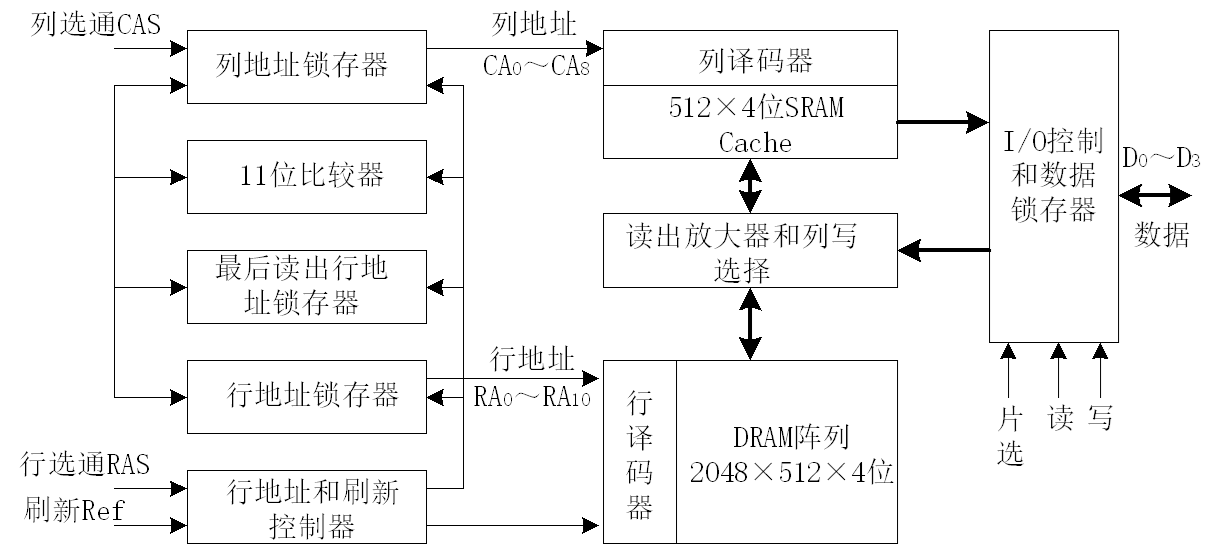

CDRAMоƬ�ֳ�Ϊ��������������DRAM,������DRAM�ϼ�����һСƬ��SRAMʵ�ֵĸ��ٻ���洢��(Cache),SRAM�б���������һ�ζ����������е�ȫ������,��ʹCPU�и���Ļ�����ʸ����ٵ�Cache������DRAM,���ʹDRAMоƬ�����ܵõ��������Ľ���?

1M��4λCDRAMоƬ�Ľṹ��ͼ

3? SDRAM ?

SDRAM �ֳ�Ϊͬ���� DRAM ( Synchronous DRAM ), SDRAM �Ƕ�̬�洢��ϵ����ʹ����㷺�ĸ��١��������洢��,���ڲ��洢��ĵ�Ԫ�洢��·��Ȼ�DZ��� DRAM �洢��ṹ,ֻ���ڹ����Ͻ����˸Ľ�,�繦�ĸ��͡����ɶȸ��ߵȡ�SDRAM ����˫�洢��ṹ,�ں�����������Ĵ洢����,�� CPU ��һ���洢����������ݵ�ͬʱ,��һ���洢�����Ѿ����ö� / д���ݡ�ͨ�������洢����Ľ������,��ȡ��Ч�ʵõ��ɱ���ߡ�

4? DDR SDRAM ?

DDR SDRAM ��˫������ SDRAM ( Double Date Rate SDRAM ),������ص��������ʱ�Ӵ����ص��ϡ����ض��ܽ������ݴ���( SDRAM �����������ش�������),��������� SDRAM ��˵�ܽ��ڴ�Ĵ����������һ����????????DDR�ڴ���Ϯ��SDRAM�ڴ��������ϵ,������ɱ�����ͨSDRAM�߲��˶��١�

3.6.3�����洢��

?

3.7 cache?

Cache��������

���� cache ��Ŀ�ľ�����������ʹ�����ƽ������ʱ��ӽ� cache �ķ���ʱ��

��: CPUִ��һ�γ���ʱ,cache��ɴ�ȡ�Ĵ���Ϊ1900��,������ɴ�ȡ�Ĵ���Ϊ100��,��֪cache��ȡ����Ϊ50ns,�����ȡ����Ϊ250ns,��cache/����ϵͳ��Ч�ʺ�ƽ������ʱ�䡣

������Cache�ĵ�ַӳ�䷽ʽ

ֱ��ӳ�䷽ʽȫ����ӳ�䷽ʽ������ӳ�䷽ʽcache д��������?

Write-back: д�ط�Write-through: ȫд�� ( дͨ�� )дһ�η� :

��ϰ��:��������

˼����:Cache������������Щ�����й�?

�������Ϊ��cache����������֯��ʽ����Ĵ�С?