内建自测试(Bist)

内建自测试(BIST)设计技术通过在芯片的设计中加入一些额外的自测试电路,测试时只需要从外部施加必要的控制信号,通过运行内建的自测试硬件和软件,检查被测电路的缺陷或故障。和扫描设计不同的是,内建自测试的测试向量一般是内部生成的,而不是外部输入的。内建自测试可以简化测试步骤,而且无需昂贵的测试仪器和设备(如ATE设备),但它增加了芯片设计的复杂性。

1.什么是BIST测试技术?

内建自测(Built-in Self Test) 简称BIST,是在设计时在电路中植入相关功能电路用于提供自我测试功能的技术,以此降低器件测试对自动测试设备(ATE)的依赖程度。

BIST是一种DFT(Design for Testability)技术,它可以应用于几乎所有电路,因此在半导体工业被广泛应用。举例来说,在DRAM中普遍使用的BIST技术包括在电路中植入测试向量生成电路,时序电路,模式选择电路和调试测试电路。

BIST技术的快速发展很大的原因是由于居高不下的ATE成本和电路的高复杂度。现在,高度集成的电路被广泛应用,测试这些电路需要高速的混合信号测试设备。BIST技术可以通过实现自我测试从而减少对ATE的需求。

BIST技术也可以解决很多电路无法直接测试的问题,因为他们没有直接的外部引脚,比如嵌闪。可以预见,在不久的将来即使最先进的ATE也无法完全测试最快的电路,这也是采用BIST的原因之一

2.BIST基本电路结构:

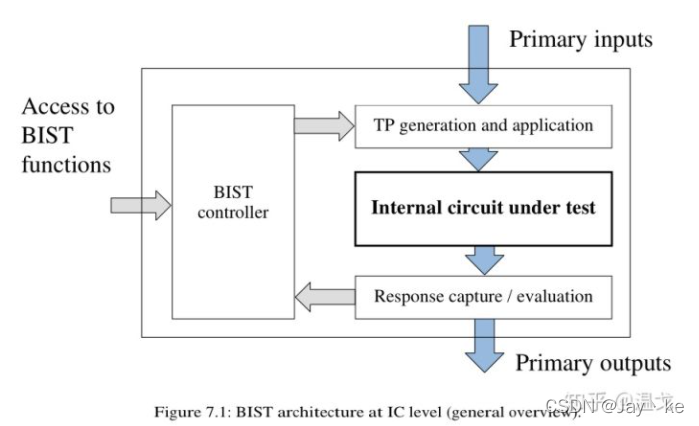

BIST 电路基本由三部分组成:

-

TPG (test pattern generator)测试向量生成器

用来自动生成测试向量,灌入CUT(circuit under test)的输入引脚。 -

ORA (output response analyzer)输出响应分析器

对待测电路的输出进行压缩对比,来确定电路是否有错误。 -

BIST controller 内建自测试控制器

控制何时将什么样的数据用到被测电路上,控制被测电路的时钟并决定何时读取预期响应

3.BIST技术分类:

大致可分为两类Logic?BIST(LBIST)?和?Memory?BIST?(MBIST)

LBIST通常用于测试随机逻辑电路,一般采用一个伪随机测试图形生成器来产生输入测试图形,应用于器件内部机制;而采用多输入寄存器(MISR)作为获得输出信号产生器。???MBIST只用于存储器测试,典型的MBIST包含测试电路用于加载,读取和比较测试图形。目前存在几种业界通用的MBIST算法,比如“March”,March-C,MATS+算法。

另一种比较少见的BIST称为Array?BIST,它是MBIST的一种,专门用于嵌入式存储器的自我测试。Analog?BIST,则用于模拟电路的自我测试。???BIST技术正成为高价ATE的替代方案,但是BIST技术目前还无法完全取代ATE,他们将在未来很长一段时间内共存。

4.BIST电路的优缺点:

优点:

1, 降低测试成本

2, 提高错误覆盖率

3, 缩短测试所需时间

4, 方便客户服务

5, 独立测试的能力

缺点:

1, 额外的电路占用宝贵面积

2, 额外的引脚

3, 可能存在的测试盲点

参考 https://zhuanlan.zhihu.com/p/169490809