̨����2nm��3nm�Ƴ�

̨������·����ɷ�����˾,���ļ��:̨����,Ӣ�ļ��:tsmc,���ڰ뵼�����칫˾��������1987��,��ȫ���һ��רҵ�����·�������(��Բ����foundry)��ҵ,�ܲ�����Ҫ����λ���й�̨��ʡ�������п�ѧ����

2017��,����ռ����56%��2018��һ����,�ϲ�Ӫ��85����Ԫ,ͬ������6%,������30����Ԫ,ͬ������2.5%,ë����Ϊ50.3%,������Ϊ36.2%,����10����Բ������ռ�����ܾ�ԲӪ�յ�19%����ֹ2018��4��19��,����TSM,��ֵ2174����Ԫ,��̬��ӯ��19��

2018��8��3����,̨���紫������ϵͳ����Բ�������,�����ƾ�Բ12�����пƾ�Բ15�����Ͽƾ�Բ14������Ҫ�����Ļ�̨ͣ�ߵ���Ϣ��̨����֤ʵ,ϵ���������,���������ڿ�����8��4��,̨���������ͨ�����ҵ����������

2020��8��26��,̨����(�Ͼ�)����˾�ܾ�����������2020����뵼�����ϱ�ʾ,̨�����5���ײ�Ʒ�Ѿ���������������,3���ײ�Ʒ��2021������,����2022����������������

2021��10��26��,̨���������Ƴ�N4P �Ƴ̹��ա�

̨����2nm,����Խ��Խ�Ͼ�

����ƻ��ڵ��ϵ�̨���н���һ��ȫ�µ�оƬ���쳧,��������ԱҪ������ȼ�����糧����������ʩ�ĵ������ġ��ù���ּ�ڲ����Ƚ��� 2 ���� (nm) �뵼�幤�������뵼��,���ƻ���Ϊ̨����ĵڶ��� 2 �������칤������һ������������̨���������,�ù�˾�Ѿ�����˻������� ̨������Ա������������ǰ¶��̨�мƻ�������ϸ��,�������ʾ,ý�屨���пƳ�������ˮ��Լ4.9���,��̨��Ԥ��,̨�����Ͽ�3�����³�һ��ĵ���Լ70�ڶ�,���̨�����п�������������2�����Ƴ�,�ĵ�������3���׳������ˡ� ̨�����п�������,ÿ�պ��õ�ˮ��������,Ҫ���л�ȼ������Ͽ��˽��������ֳ��ŷ�Դ˵,̨�����пƳ���һ�����õ�10��ֵ�ˮ,�õ��л�ȼú�糧һ���벿����ķ�����,���ܾ���,ϣ��̨����δ���ܶ����̵硣 ̨�����пƳ���һ�����õ�10��ֵ�ˮ,�ɳԵ��л�ȼú�糧һ���벿����ķ�������ϣ��̨����δ���ܶ����̵�,�ر����밶�����̵��ܾ����ν�����,��̨�������Ѳɹ������̵���Դ�� ����Ҫ��ȼú�ķ���,�����л��ȼ������Ҫ�Ͽ��,����ר��ѧ���ƹ�,2025��̨����ռǫ̈̄�õ���ʱ㽫��4%�ɳ���8%,�����dz��Lһ���� �ڽ���6��,������̨�����̨����2nm�����Ĺ滮,������2nm��Բ������������Ƽ�,���ڽ�����Щʱ������ˮ��Դ��ȱ��,�ù�˾���ܻ����������ڶ���2nm��Բ���ļƻ��� ̨����ĵ�һ���ܹ�ʹ����N2���켼������оƬ�Ĺ�����λ��̨�山�������ر�ɽ�����Ĺ�����2021��,��˾�������µ�R1�з���ʩ,������N3��N2�ڵ㡣Ŀǰ��û�й���̨����������Ƽ����е����ʽ�ı���,���ù�˾����,�ù��������ĸ��ν��졣

�����й�̨��ý��ı�����ʾ,Ϊ��ȷ���伴�������ļ�˾�Բ��������ˮ,�ݱ���,̨������������̨���ϲ����۸��������������ͷ�Ƽ���ҵ����һ���ص㡣 �ڷ���ý���һ��������,̨����������ƻ���̨���в�̨�и�������ڶ���֧�� N2 �� GigaFab(һ��ÿ�������� 100,000 ����Բ�����ľ�Բ��),����������δ�չ���ʩ�����ء��ù�˾������˵,���������վ���֮ǰ,�������˶������ء� ��Ҫ������̨�����Լƻ����������ܹ�ʹ����N2���켼��������Բ��GigaFab��

̨����̸2nm��ʵ�ַ�ʽ

�� 2021 �� 6 �µ� VLSI �����͵�·���ֻ���,�ٰ���һ�����ڡ����� 2nm-CMOS �����˴洢�����Ƚ����պ������������Ķ��ڿγ̡��ڱ�����,���ع�ǰ��������ǰ�����������ݽ�����������ʾ�ĸ��ǻ�����,�ṩ�˶����������ܷ�չ�ij�ɫ������

̨����:δ��ʮ��� CMOS ��������

ƽ�� MOSFET ��դ������ (Gate length:Lg) ���������ڴ�Լ 25nm,��Ϊ������դ��(single surface gate)���DZ���й©( sub surface leakage)�Ŀ��ƺܲ

���Ӹ����դ��(������ FinFET ��),��ʹ���еĹ���������������դ��֮��,�ܹ��� Lg ���ŵ�������ȵĴ�Լ 2.5 ����FinFET �Ѿ���Ӣ�ض�������õĸ߶���б����(highly sloped fin walls )�� 22 ����չ��������Ӵ�ֱ�ı�(vertical walls)��̨����Ϊ5 ������ʵʩ�ĸ�Ǩ���ʹ��� FinFET��

���ߵ�����������Ч�������� (effective channel width:Weff),Weff = 2Fh + Fth,���� Fh ����(Fin)�߶�,Fth ����(Fin)��ȡ����� Weff ���������ص�·(heavily loaded circuits)����������,�����ߵ������˷���Դ����(active power)��ֱ��������Ƭ�����ڶ̹���ЧӦ(short channel effects),�� Fw �ܵ�Ǩ���ʽ��ͺ���ֵ��ѹ�ɱ���(threshold voltage variability)���ӵ����ơ��� 5nm ������ʵʩ��Ǩ���ʹ���(����ָ��,���� pFET ��Ƭ�� SiGe)ʹ TSMC ���������������Լ 18%��

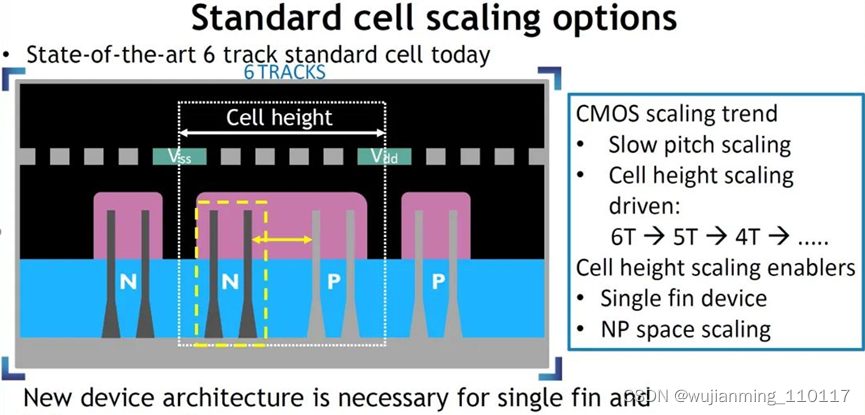

����������������С,��������͵����ֽ���Ϊһ�������⡣CPP(Contacted Poly Pitch)������cell����(��ͼ 1),�� Lg���Ӵ����� (Contact Width :Wc) �͵�Ƭ��� ( Spacer Thickness:Tsp) ���,CPP = Lg + Wc + 2Tsp������ Wc �����Ӽ�������,���ǽ��й��ոĽ��Ը��ƽӴ�,���� tsp �����Ӽ�������,����ʹ�ý����Ľ�糣������

ͼ 1. ��cell��С��

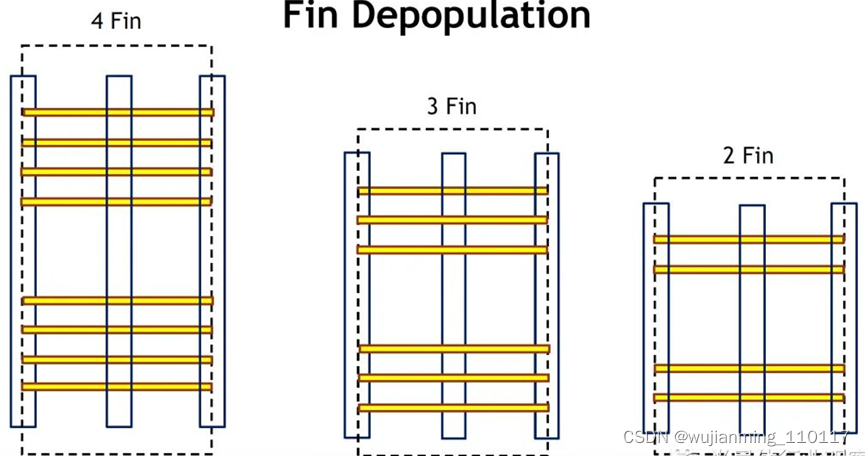

���ű�cell�߶ȵĽ���,ÿ����������Ƭ�����������(��Ƭ����),��ͼ 2��

ͼ 2. �����١�

Fin depopulation �����˵�Ԫ�ߴ�,���������ܶȲ��ṩ�˸��ߵ��ٶȺ��͵Ĺ���,����ȷʵ����������������

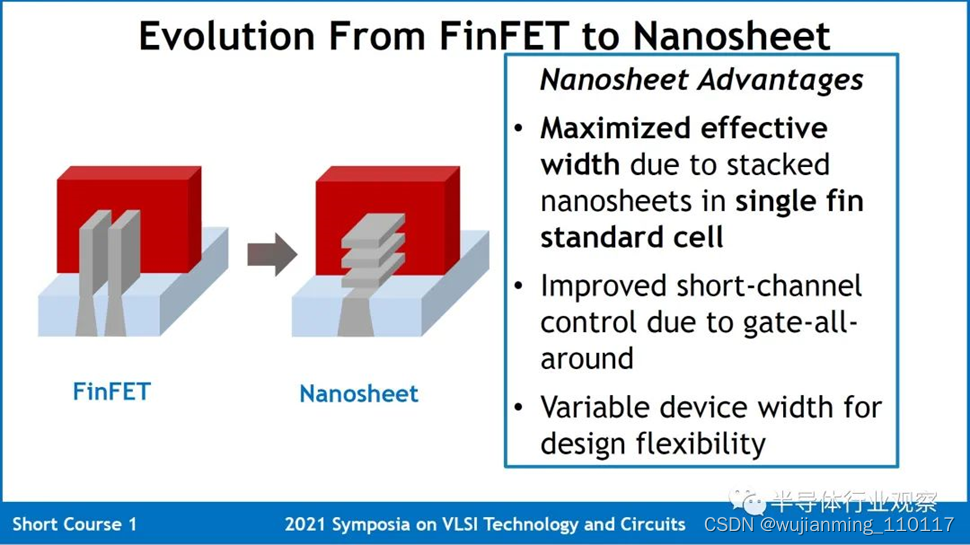

��FinFET ���ɵ��ѵ���ˮƽ����Ƭ (stacked Horizontal Nanosheets:HNS),ͨ���ı�Ƭ��(sheet width:��ͼ 3)��ͨ���ѵ�����Ƭ������ Weff ���������������ԡ�

ͼ 3. ����Ƭ����

����sheets�� Weff ���,Wee = N*2(W+H),���� N Ϊsheets������,W Ϊsheets�Ŀ���,H Ϊsheets�ĸ߶�(���)������,sheets�������ܵ��ײ�sheets���ܵ����ơ�sheets֮��ļ�����ż�������͵��ݵļ�С������,�������㹻����ʹդ������(gate metals)�͵����(dielectric)�����϶(gap)���� HNS ��ջ�·���һ���ײ�����̨������( bottom parasitic mesa device),����ͨ��ע��������п��ơ�

�� FinFET ��,nFET ����Ǩ���ʸ��� pFET ��ѨǨ���ʡ��� HNS ��,Ǩ���ʸ��Ӳ�ƽ��,����Ǩ���ʸ���,��ѨǨ���ʸ��͡�����ͨ���� SiGe ��������(cladding the channel )��ʹ��Ӧ���ɳڻ�����( Strain Relaxed Buffer)����߿�ѨǨ����,�������ּ����������ӹ��ո����ԡ�

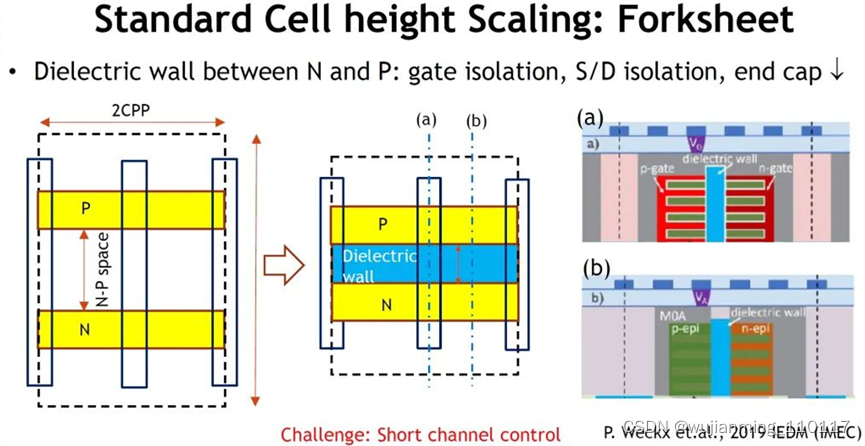

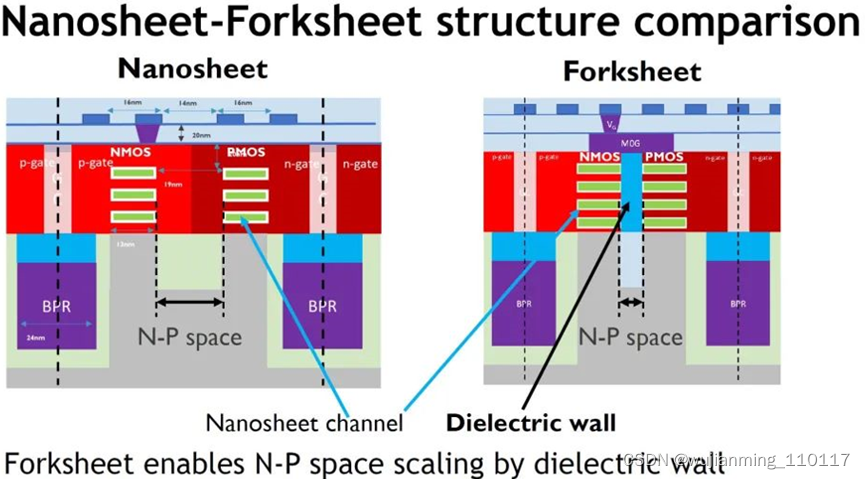

Imec ������һ����Ϊ Forksheet (FS) �ĸ���,������ nFET �� pFET ֮�������һ������,�Ӷ������� np ���,�Ӷ��γ��˸����յı���Ԫ,��ͼ 4��

ͼ 4.Forksheet

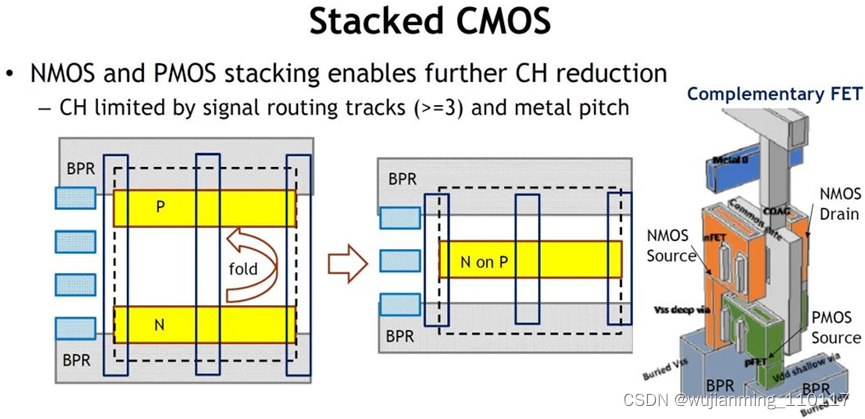

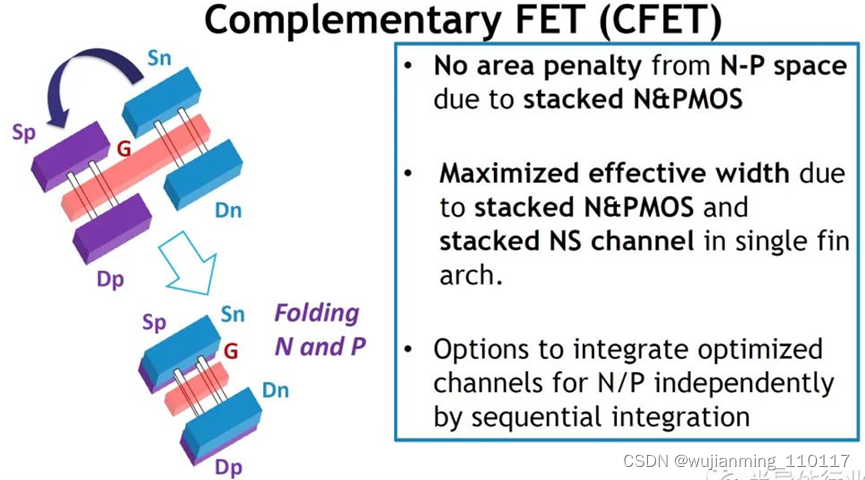

���˾��� FS �� HNS,����CFET(Complementary FET ),���߶ѵ� nFET �� pFET,�Ӷ�����ˮƽ np ��ࡣ

ͼ 5. CFET��

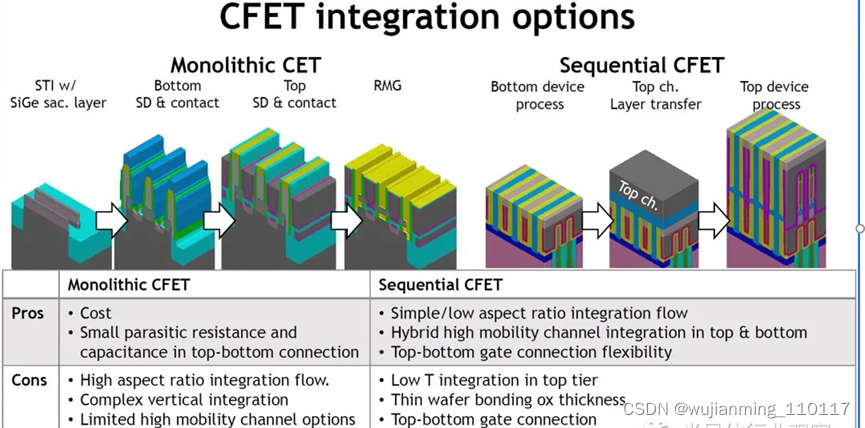

CFET ѡ�������Ƭ����(monolithic integration),���е� nFET �� pFET ������������ͬһ��Բ�ϡ������˳��(equential integration),���е� nFET �� pFET �����ڵ����ľ�Բ��,Ȼ������һ��,������ѡ���ж����ս�����о��С�

���� CFET,�ݽ���̸���˽�����ܼ��ɵ���� (Back End Of Line:BEOL) �����е� 3D ���ɡ���Щѡ����Ҫ���жྦྷ�蹵��(polysilicon channels )��������뵼��ĵ��¾����,�������������ܺͼ�����ս��

��ǰ�� (Front End Of Line:FEOL) ��,����̽�� CFET ֮���ѡ��,�����Ǩ���ʲ��ϡ����� FET (Tunnel FETs:TFET)�������� FET (Negative Capacitance FETs:NCFET)������ CMOS (Cryogenic CMOS)�͵�ά����(dimensional materials)��

��ά���ϲ������ܻ��ά���ϵ���ʽ,��Щ�����ṩ�� HNS ���̵� Lg ���͵Ĺ���,���Դ��������о��Ρ���ά����Ҳ������ HNS/CFET ����,��ѡ��ѵ�����㡣

IMEC:HNS/FS/CFET ѡ��

���� FinFET �ﵽ����,�����Խ��Խ�ߡ�Խ��Խ����Խ��Խ������Ƭ�����������ڽ����������������ӿɱ���,��ͼ 6��

ͼ 6. FinFET ���š�

�������Ƚ��ļ�����ÿ���豸�� 2 ����Ƭ�� 6 �쵥Ԫ(track cell)��ת������խ�� np ��ཫ��Ҫ�µ������ܹ����������,��ͼ 7��

ͼ 7. 6 �쵥Ԫ

Ϊ�˼��� CMOS ����,��Ҫ�� FinFET sot HNS ���ɵ����� FS �� CFET �� HNS,��ͼ 8��

ͼ 8. ���� CMOS ���ŵ�����Ƭ�ܹ���

�� FinFET ���ɵ� HNS �ṩ�˼�������,��� Weff,�Ľ��Ķ̹���ЧӦ,����ζ�Ÿ��̵� Lg ���õ���������,��Ϊ�ܹ��ı�Ƭ��,��ͼ 9��

ͼ 9. ��FinFET �� HNS��

�ݽ�������ϸ���� HNS �����Լ�һЩ��ս�Ϳ��ܵĽ�������������ĸ���Ҫģ����,HNS ������ FinFET ���շdz�����,��ͼ 10��

ͼ 10. HNS �������̡�

���� HNS ���������� FinFET ����,����ͬ�Ĺؼ�ģ������ѡ��ͷ�ʴ�̺�ʵ�ֶ����ֵ��ѹ�ر����ѡ����� HNS ���������ģ����ĵ�ϸ��,�кܶ�ܺõ���Ϣ,�ⳬ�������������������µķ�Χ��û����ȷ���۵�һ������,Ϊ�˽� HNS ������չ�� 5 �쵥Ԫ,��Ҫ����ʽ��Դ�� (Buried Power Rails:BPR),������һ�����ڿ����е����ѹ���ģ�顣

������֮ǰ����ʾ������,FS ����ʵ�� HNS �Ľ�һ����չ��ͼ 11 չʾ�˽��������( dielectric wall) HNS ��Ԫ�ĸ���ϸ��ͼ��

ͼ 11. ˮƽ Nanosheet/Forksheet �ܹ��Ƚϡ�

FS ������Ҫ��������Լ�С np ���,ͼ 12 ˵���˹������̡�

ͼ 12. Forksheet ���̡�

���� FS,CFET ͨ���ѵ������ṩ��ˮƽ np ��ࡣͼ 13. ˵���� CFET ���

ͼ 13. CFET ���

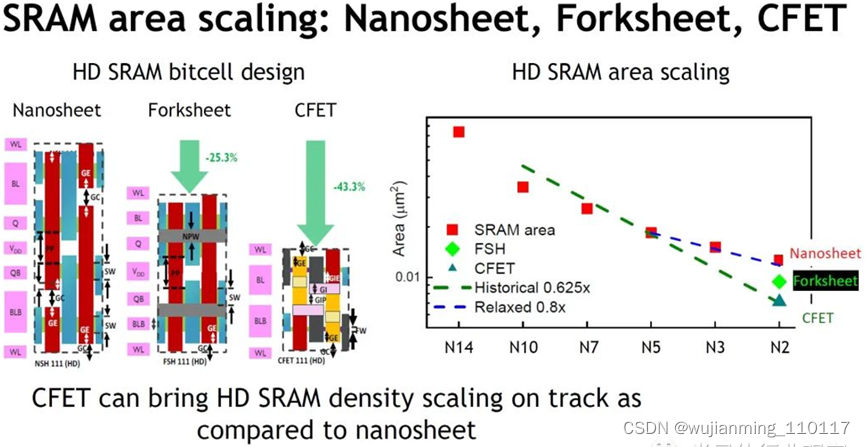

CFET ���� SRAM �����ر���Ȥ��SRAM �����Ѿ��Ż����Ҹ����������š�CFET �ṩ�˽� SRAM ���Żָ�����ʷ���Ƶ�DZ��,��ͼ 14��

ͼ 14. ʹ�� CFET ���� SRAM ���š�

��ǰ����,������ CFET ���췽��,��Ƭ��˳��ͼ 15 �Ա��������ַ�������ȱ�㡣

ͼ 15. CFET ����ѡ�

2021��12��27����Ϣ,̨���繫˾�ܲ�κ�ܼұ�ʾ,̨�������������̨�ϡ����۶���������Ͷ��,Ϊ�������ܵ�ƽ���Լ����յķ�ɢ,̨��һ����������ѡ��֮һ��

̨����Ԥ������Ʊ�ɽ�õ����� 2nm ��,�������õز���,̨������ܻᵽ̨������ 2nm ���ܡ�

̨�����߱��ľ�����������,�ø߿Ƽ�ҵ�˲ź�Ը������̨��,̨��Ҳ��Ԥ��������ѡ��֮һ��

̨���� 2nm �Ƴ̼������� 2025 ����������̨����滮,���������ѧ����ɽ�õ����� 2nm ��,Ŀǰ��ƹ��������ڰ�������õ�ȡ����ҵ,���������õز���,̨������ܻᵽ̨������ 2nm ���ܡ�

̨������ǰ�����ڸ��۽���,���� 7nm �� 28nm ����оƬ,�Ͽ����� 5nm �� 3nm �Ƚ��Ƴ̵������ص�,Ϊ�ﱱ���С�����ƽ�Ⲽ��,̨�н���̨����δ�������Ƚ��Ƴ̲��ܵ��ص�֮һ��

���������滮,̨����ά��һ��̬��,���Ʋ��ų��κο�����,�賧�ص�����������,�����������ֺ�����������̨�м����۵��ʺϰ뵼�彨�����õء�

���ڿƼ���ҵ��ˮ,̨���������Աָ��,̨��������ˮ���ж����ҵ,����̨���硢�Ѵ������,Ǣ��ÿ��Ҫ�õ� 10 ��ֵ�����ˮ,��ȷ����ˮ���ݡ���ˮ��Դ�����á�

��̨�����ý��DigiTimes ��TechTaiwan����,̨������λ��̨�ϸ�������̨���ѧ�� Fab 18 ��������3nm����(��ΪN3)оƬ�������� ��ʹ���½ڵ��оƬHVM����2022���°��꿪ʼ,�������¹��յ�����ʱ�䳬��100��,̨��������ĵ�һ��N3оƬ����2023������� ����һ������3nmоƬ��ƻ���豸Ԥ�ƻ���2023���״�����,��������A17оƬ��iPhone 15/Proϵ�л��ͺͲ���M3оƬ��ƻ��Silicon Mac����(�������ƶ����ݶ�)��

̨����� N3 ���켼���Ǵ���������һ���ڵ�,רΪ�����ֻ������ܼ��� (HPC) Ӧ�ó�������,��̨����ͨ�����Ƚ���ƶ���ƵIJ��Ա������ۡ��¹��ս�����ʹ�á����� 20 �㡱�ļ������� (EUV),�����е� N5 ���ڵ����ʵ���ԸĽ���̨�����ŵ�������� 10% �� 15%(����ͬ�Ĺ��ʺ;����������)���ߴ� 30% �Ĺ��Ľ���(����ͬ��ʱ�Ӻ��Ӷ���)���ߴ� 70% �����ܶȺ�20% �� SRAM�ܶ�������

̨�����Ͽ�3�����³�����������ʽ��������,�������˵���¶��Ϣ,N3Ԥ��2022�°�������,���5����(N5),���꽫�и����²�Ʒ��ƶ���(Tape-out),2023�����ῴ�����Թ���Ӫ��;ͬʱҲ���Ƴ�N3EΪN3����,����ʱ�̳�������N3������һ��(2023���°�)��

̨����滮3�������ײ�����Ŀ��Ϊ5����6��Ƭ,2023��3�¾ͻ���3����4��Ƭ��λ,����ƻ����ͷ��,�Ŷ���2022��12������1�½����Բ�,��Ҫ����2022���»����ײ��ͻ���������Ӣ�ض�,2023����һ����Ʒ������̨����3����4�����Ƴ̡�

Ӣ�ض�����2022��12����Ѯ���а뵼�幩Ӧ�̸߷��,��˾�߲�Ҳ�ƻ���̨������档ҵ��ָ��,Ӣ�ض������Ƴ̵���,�г�Ҳ�����ֲ�������,�����һ����Ʒ�������dz���Ҫ,���������ⲿ��ԴЭ�������ռ��Ӣ�ض���Ȼ�Ż���ʾ����������Ҫ�����������,����ҵ�����»��ǵ÷�����̬,�����õ��㹻3���ײ��ܡ�

̨���編˵��ָ��,5G�ֻ�оƬ��HPC����оƬ����3���������������ҪͶƬ��Ʒ,����ƻ����Ӣ�ض�����N3�ײ���������,�����ơ�AMD����ͨ��Ӣΰ���Ҳ�ƻ������ϡ�ҵ�翴��̨����3��������һ����߾��������Ƴ�,����3���������Ƴ�����ά�ָߵ�,����������Ӫ����������д���¸ߡ�

�����

https://mp.weixin.qq.com/s/pfMhmskEtabtqNXoRm_2tQ

https://mp.weixin.qq.com/s/a_67sNfHlVo-MSlAS3t-rA

https://mp.weixin.qq.com/s/EOgtkOpyTgqB3GV0GwYGqA