AXI_DMA �ػ�����

����

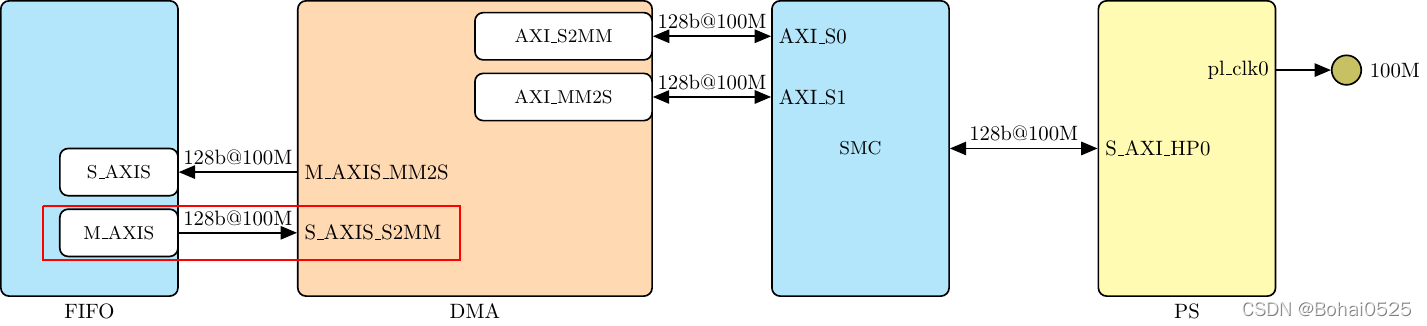

- MPSOC��PL��PS��������ݽ������벻��AXI_DMA��,������xazu3egƽ̫����֤�˸�IP(�õ�����Direct Register Mode),������������ڳ���(ѧϰ)������

- [����ͼƬת��ʧ��,Դվ�����з���������,���齫ͼƬ��������ֱ���ϴ�(img-vQ5lbo1P-

- [����ͼƬת��ʧ��,Դվ�����з���������,���齫ͼƬ��������ֱ���ϴ�(img-vQ5lbo1P-

1��DDR->fifo(MM2S)

- ʵ��PS��PL���ݴ���,PSͨ��AXI_Lite�ӿ�������ؼĴ���������MM2S���ݴ���,����Ĵ�����ο�pg021�ҾͲ�������;

int axi_dma_transfer(u8 dma_hd_id, u32 len)

{

int Status = 0;

dma_handle *dma_hd = &dma_hand[dma_hd_id];

dma_hd->trans_st = BUSYING;

Xil_DCacheFlushRange((UINTPTR)dma_hd->ptr_txbuff, DMA_BUFF_LEN);

Status = XAxiDma_SimpleTransfer(dma_hd->dma_ptr, \

(UINTPTR)dma_hd->ptr_txbuff, len, \

XAXIDMA_DMA_TO_DEVICE);

if (Status != XST_SUCCESS) {

return XST_FAILURE;

}

return XST_SUCCESS;

}

- �ص�˵һ��*XAxiDma_SimpleTransfer()*����,�ú����ȿ��Դ���MM2S����,Ҳ���Դ���S2MM����,�������ǰ���˳�����ú�����ؼĴ���,����ֻ��Ҫָ�������ݻ�����,���䳤�Ⱥ�,���ɡ�

- ����,һ���ط���Ҫע��������ݻ������Ķ��뷽ʽ��AXI_DMA����Ϊ�����(�ҵ�λ����128)

#define DMA_DATA_WIDTH 128

u8 dma_tx_buff0[DMA_BUFF_LEN]__attribute__((aligned (DMA_DATA_WIDTH)));

u8 dma_rx_buff0[DMA_BUFF_LEN]__attribute__((aligned (DMA_DATA_WIDTH)));

- ����ʵ�ʲ���

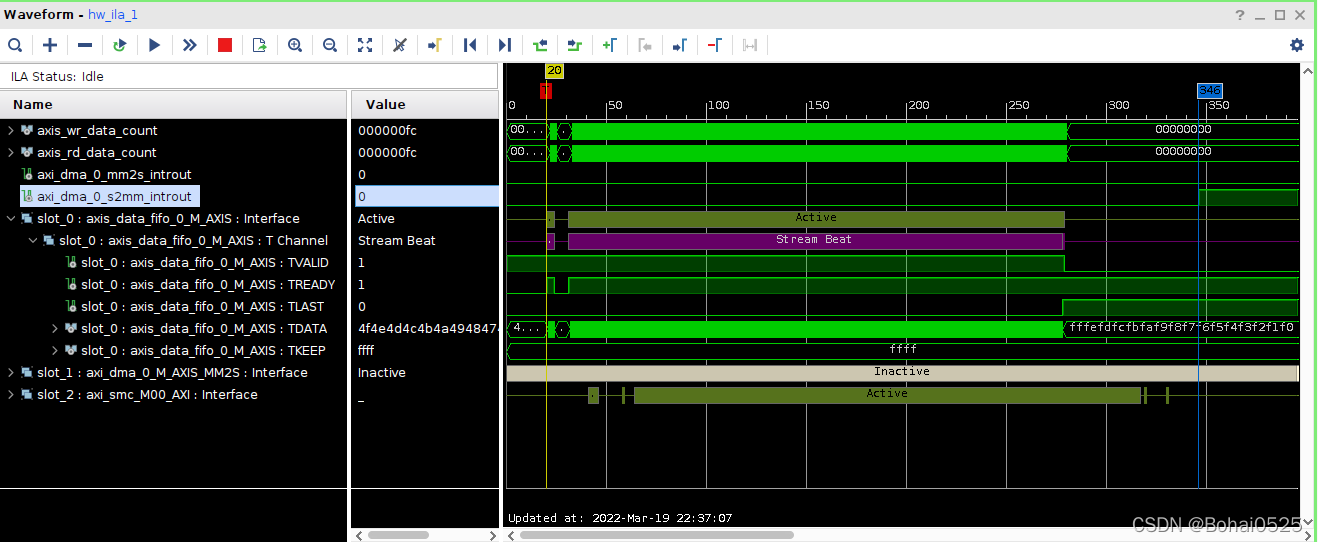

- ϵͳʱ��100MHz,����λ��128bit,������������4096Byte,��������Ҫ256��ʱ������

- ʵ����Ҫ535��ʱ������

- Ч��Ϊ47%

2��fifo->DDR(S2MM)

- 2.1��ͬ����������*XAxiDma_SimpleTransfer()*���������,��Ҫ���жϵĻ���Ҫ���������������

XAxiDma_IntrEnable(dma_hd->dma_ptr, XAXIDMA_IRQ_IOC_MASK, \

XAXIDMA_DEVICE_TO_DMA);

-

2.2������

-

ϵͳʱ��100MHz,����λ��128bit,������������4096Byte,��������Ҫ256��ʱ������

-

ʵ����Ҫ326��ʱ������

-

Ч��Ϊ78%

-

��fifo��������ʱ��ʹcpuû�з���S2MM,DMAҲ��Ԥ�Ȼ���80Byte����

-

-

2.3���ж�

-

DMA��last�źź�,�����ж�,

-

����DMA�ó�IDLE״̬

-

�����жϺ�õ�����ʵ���ݳ��ȿ��ܻ�С�����õĴ�������,��ʵ���ȿɲ�ѯreg58

-

3��ע������

��Direct Register Mode��

-

3.1��reg34 = 0x5011,����

- ԭ����DMAһ�ζ�ȡ����С��S_AXIS_S2MM����һ��ͻ������

- axi_streamһ��ͻ��������last�źž���

- ԭ����DMAһ�ζ�ȡ����С��S_AXIS_S2MM����һ��ͻ������

-

3.2���ĵ���û��˵��axi_dma��mpsoc�е��������,����ʵ��ʱ�ӿ����ܵ�300MHz

-