资源路径

链接:https://pan.baidu.com/s/1N61m5CMEoc8lRP4yn0ppMg?

提取码:41e7?

使用示例

下载解压于安装有vcs的虚拟机中,如安装路径为:

/home/xiaotu/my_work/auto_verification/则执行脚本:

/home/xiaotu/my_work/auto_verification/auto_verification -t xxx -f ./xxx.v-t:顶层名称;

-f:顶层文件,或包含顶层文件的文件夹;当为顶层文件时,文件名可以和顶层名不一致但必须含有顶层module的代码;当为文件夹时,其内部必须包含顶层.v文件;

测试1:-f mem.v,文件内只有一个mem

执行结果:

[xiaotu@xiaotu-eda ~]$my_work/auto_verification/auto_verification -t mem -f my_work/vcs_demo/rtl/mem.v

gen over! please cd ./mem_verification/sim此时,rtl已经被搬运到对应的mem_verification/rtl目录,同时生成testbench(部分):

parameter DATA_WD = 32;

parameter DEPTH = 512;

parameter DELAY = 3;

parameter ADDR_WD = $clog2(DEPTH);

parameter ERR_1BIT = 0;

parameter ERR_2BIT = 1;

parameter EOF = 0;

logic clk;

logic rst_n;

logic i_wr_en;

logic i_rd_en;

logic [ADDR_WD -1:0] i_addr;

logic [DATA_WD -1:0] i_data;

logic [DATA_WD -1:0] o_rdata;

logic o_1bit_event;

logic o_2bit_event;

logic [ADDR_WD -1:0] o_mem_err_addr_1bit;

logic [ADDR_WD -1:0] o_mem_err_addr_2bit;

initial forever #5ns clk = ~clk;

initial begin

rst_n = 1'b0;

`DELAY(30, clk);

rst_n = 1'b1;

end

initial begin

#100000ns $finish;

end

initial begin

i_wr_en = 0;

i_rd_en = 0;

i_addr = 0;

i_data = 0;

`DELAY(50, clk);

end

mem #(

.DATA_WD(DATA_WD),

.DEPTH(DEPTH),

.DELAY(DELAY),

.ADDR_WD(ADDR_WD),

.ERR_1BIT(ERR_1BIT),

.ERR_2BIT(ERR_2BIT),

.EOF(EOF))

u_mem(

.clk(clk),

.rst_n(rst_n),

.i_wr_en(i_wr_en),

.i_rd_en(i_rd_en),

.i_addr(i_addr),

.i_data(i_data),

.o_rdata(o_rdata),

.o_1bit_event(o_1bit_event),

.o_2bit_event(o_2bit_event),

.o_mem_err_addr_1bit(o_mem_err_addr_1bit),

.o_mem_err_addr_2bit(o_mem_err_addr_2bit)

);

endmodule然后呢要做的事就是在mem例化的上方,手动去force下信号驱动,定向构造一些激励。

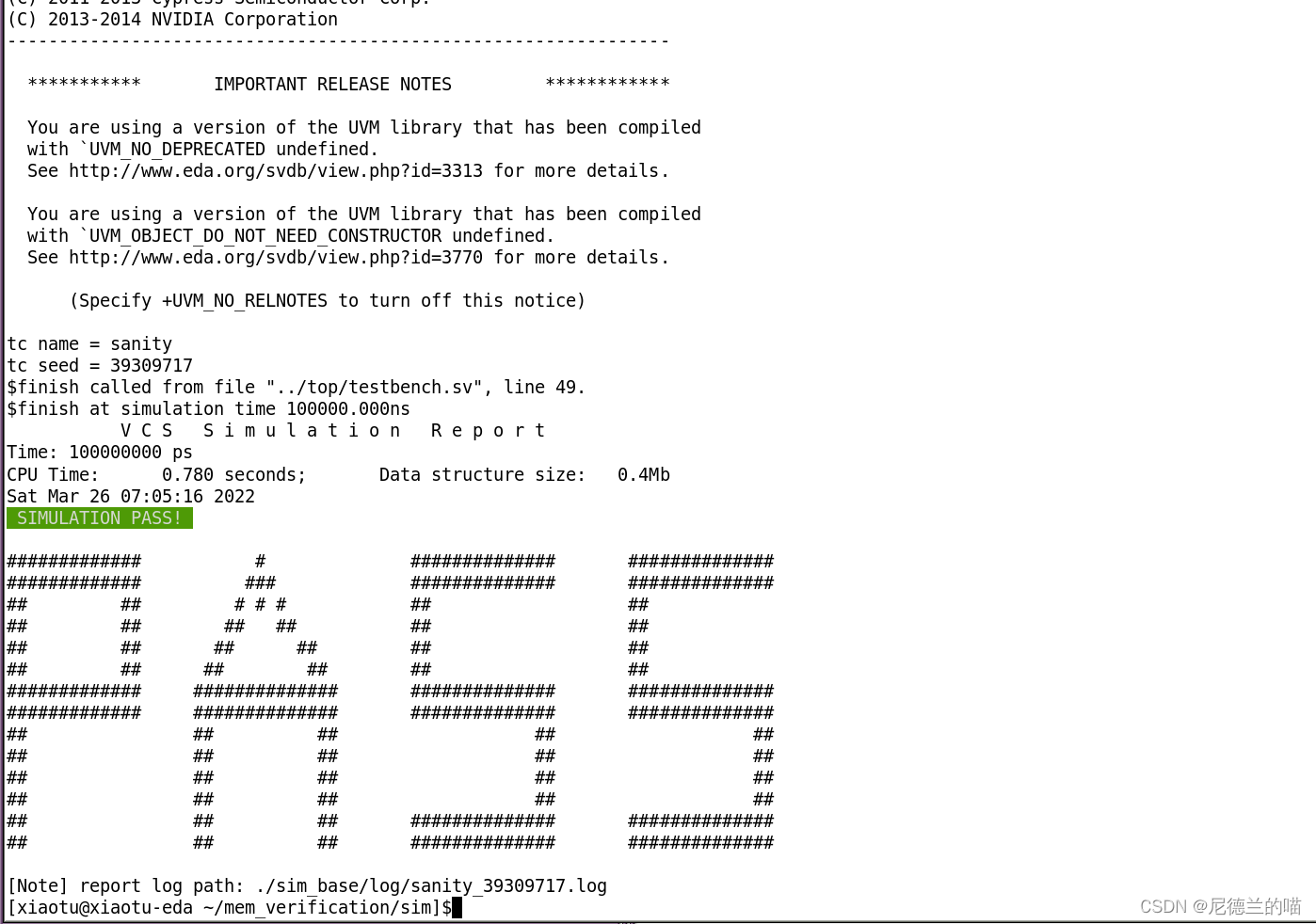

执行下:

测试2:-f目录,目录内有多个文件

[xiaotu@xiaotu-eda ~]$my_work/auto_verification/auto_verification -t triffic_light -f ./triffic_light

gen over! please cd ./triffic_light_verification/sim后续的流程一样,我就不贴图了。